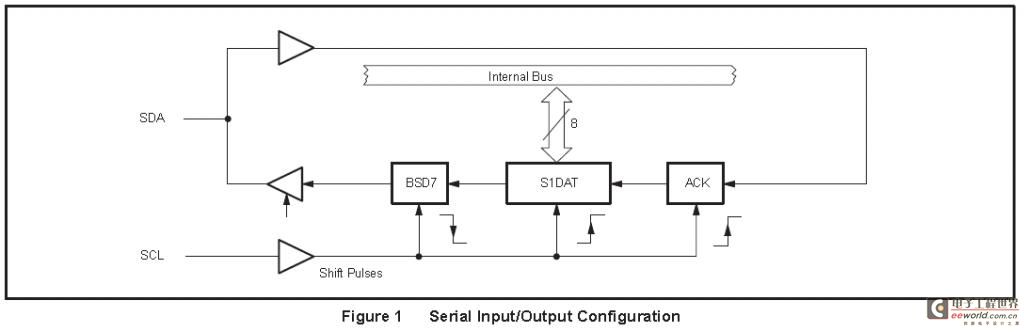

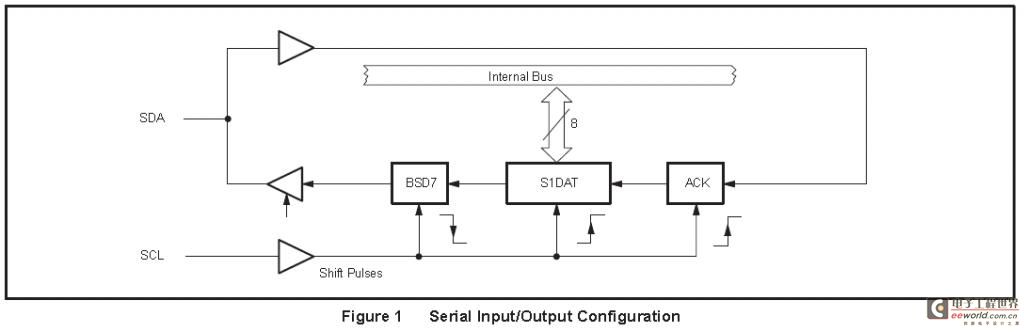

This article takes the IIC bus serial input and output structure of 8XC552 (a microcontroller from Philips) as an example to deeply understand the IIC bus protocol:

Reference address:I2C bus serial input and output structure

The serial input and output structure of the IIC bus ensures that the data register of the IIC bus can store the latest data on the bus. SDAT and ACK form a 9-bit shift register, which forms a ring structure. The data on the bus is continuously sampled while the serial output is in progress. The ACK flag is controlled by the bus and can be accessed by the CPU (1 is stored for non-acknowledgement, and 0 is stored for acknowledgement). On the rising edge of the clock pulse on the SCL line, the serial data is stored in SDAT through the ACK flag, and the serial data is shifted out along BSD7 on the falling edge of the SCL clock pulse. When a byte of data is shifted into SADT, the data in SDAT is valid, and the control logic sends the acknowledgement bit in the 9th clock pulse cycle.

Why must the data on the data line remain stable when the clock signal is high when the IIC bus is sending data? This is because the data on the bus will be collected during the high level period. If the data on the bus is unstable at this time, the collected data and the sent data will be inconsistent, thus shutting down the transmission (similar to arbitration failure). The protocol stipulates that the high or low level of the data line is allowed to change only when the clock signal is low. This is because the data in BSD7 is sent on the falling edge of the clock, and the data on the bus will not be collected during the low level of the clock pulse.

When the CPU writes to SDAT, SDAT7 is loaded with BSD7, which is the first bit of data sent to the SDA line. After 9 clock pulses, the 8-bit data in SADT is sent to the SAD line, and the acknowledgement bit appears in ACK. In this way, the data sent to the bus is returned to SDAT.

The SDA register contains the data to be sent or a data byte just received. When sending, the data is always shifted from right to left. When the data is shifted out, the data on the bus is shifted in at the same time. This structure of the shift register ensures that the data will not be lost when the bus competition fails. It is connected to the internal bus in parallel and to SDA in serial. When sending data, it is loaded into SDAT by the internal bus. When sending, the data is returned to SDAT in serial from the serial channel. When receiving, the newly received data on the SDA line is loaded.

Previous article:I2C Bus Timing Simulation (Part 2) - Deepen your understanding of the bus protocol

Next article:About I2C and SPI bus protocols

- Popular Resources

- Popular amplifiers

Recommended Content

Latest Microcontroller Articles

- Learn ARM development(16)

- Learn ARM development(17)

- Learn ARM development(18)

- Embedded system debugging simulation tool

- A small question that has been bothering me recently has finally been solved~~

- Learn ARM development (1)

- Learn ARM development (2)

- Learn ARM development (4)

- Learn ARM development (6)

He Limin Column

Microcontroller and Embedded Systems Bible

Professor at Beihang University, dedicated to promoting microcontrollers and embedded systems for over 20 years.

Professor at Beihang University, dedicated to promoting microcontrollers and embedded systems for over 20 years.

MoreSelected Circuit Diagrams

MorePopular Articles

- LED chemical incompatibility test to see which chemicals LEDs can be used with

- Application of ARM9 hardware coprocessor on WinCE embedded motherboard

- What are the key points for selecting rotor flowmeter?

- LM317 high power charger circuit

- A brief analysis of Embest's application and development of embedded medical devices

- Single-phase RC protection circuit

- stm32 PVD programmable voltage monitor

- Introduction and measurement of edge trigger and level trigger of 51 single chip microcomputer

- Improved design of Linux system software shell protection technology

- What to do if the ABB robot protection device stops

MoreDaily News

- Analysis of the application of several common contact parts in high-voltage connectors of new energy vehicles

- Wiring harness durability test and contact voltage drop test method

- From probes to power supplies, Tektronix is leading the way in comprehensive innovation in power electronics testing

- From probes to power supplies, Tektronix is leading the way in comprehensive innovation in power electronics testing

- Sn-doped CuO nanostructure-based ethanol gas sensor for real-time drunk driving detection in vehicles

- Design considerations for automotive battery wiring harness

- Do you know all the various motors commonly used in automotive electronics?

- What are the functions of the Internet of Vehicles? What are the uses and benefits of the Internet of Vehicles?

- Power Inverter - A critical safety system for electric vehicles

- Analysis of the information security mechanism of AUTOSAR, the automotive embedded software framework

Guess you like

- Division circuit

- Android smart wearable device development from entry to mastery pdf download

- Why can't we develop industry software like Matlab?

- Android control LED-2-JNI basis of SinlinxA33 development board

- Free application: Canaan AI new product K510 development kit, RISC-V dual-core CPU @ 800MHZ (with training video)

- Watchdog for C2000-8027 series

- Some questions about magnetic field

- EEWORLD University Hall----Live Replay: Melexis consumer-grade ultra-low power position sensor simplifies design and reduces costs

- EEWORLD University - Multiphase Buck Regulator Design: Case Study

- I need help from the experts on writing MAX7219 dot matrix in microPython

LTC1052MP

LTC1052MP

京公网安备 11010802033920号

京公网安备 11010802033920号