Introduction

With the continuous development of industrial technology, the requirements for microcontroller control are becoming higher and higher. Microcontrollers are required to have higher response speed and stronger data processing capabilities. Various high-performance new microcontrollers have been rapidly developed and applied. . Microcontrollers are mainly high-speed digital signals. Weak signals are easily affected by electromagnetic interference from the outside world. At the same time, problems such as power outages and endless loops may occur in the microcontroller system. In industrial control situations, once a control error occurs, it will cause incalculable losses. Therefore, how to improve the reliability of control has been an important issue for a long time. This article introduces a practical development plan using the 32-bit high-performance microcontroller MC68HC376, and focuses on the design and implementation methods to improve system reliability.

MC68HC376 is a new type of 32-bit high-performance microcontroller launched by Motorola. It has strong data processing, logical operation and information storage capabilities, and supports BDM (Background Debug Mode) mode. Through a simple dedicated cable interface, the microcontroller system can be directly simulated, developed and programmed. In addition, due to its high internal integration and less external expansion work, MC68HC376 has strong anti-interference capabilities. At the same time, through the anti-interference design of external hardware circuits and software, the control system can achieve higher reliability.

1 Basic structural design of the control system

MC68HC376 has a high degree of integration. Its main functional modules include 32-bit CPU; system integration module (SIM); 4K spare RAM; 8K on-chip ROM; 10-bit queued analog-to-digital converter (QADC) ; Queue serial communication module (QSM); Constructible clock module (CTM4); Time processing unit (TPU);

3.5K static TPURAM; CAN control module (TOUCAN). Its basic performance is as follows:

(1) 24-bit address bus and 16-bit data bus structure, supporting 32-bit data operations.

(2) 2 8-bit dual-function I/O, 1 7-bit dual-function I/O, 16~44 analog input channels.

(3) It has system protection logic and can perform clock monitoring and bus monitoring at the same time.

(4) Fast speed, the system clock can reach 20.97MHz with a 4.194MHz crystal oscillator.

(5) Low power consumption and low-power sleep function.

(6) Support high-level language and background debugging.

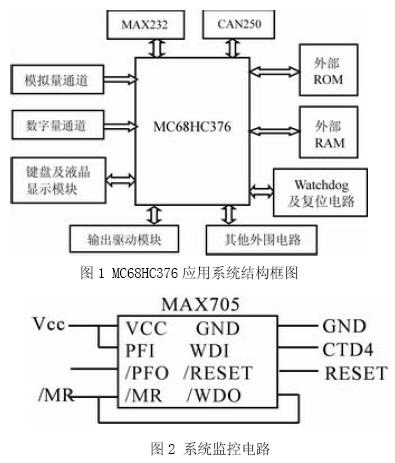

The basic structure of system expansion MC68HC376 has a high degree of internal integration, so it requires less peripheral expansion work. The basic structure includes external Flash ROM, RAM, analog input channel, digital input channel, keyboard, liquid crystal display, RS-232 level converter MAX232 and CAN controller CAN250, etc. The structural block diagram is shown in Figure 1. This article focuses on the reliability design of the system.

2 System Reliability Design

2.1 Microprocessor Hardware Monitoring Circuit

This article uses the monitor MAX705 chip to form an external monitoring circuit. The external wiring of the circuit is shown in Figure 2. The circuit features a watchdog timer, automatic and manual reset functions, and voltage threshold monitoring.

Since the logic state of the CPU and bus is uncertain when the system is powered on, powered off, or when the supply voltage is insufficient, the microcontroller should be maintained in a reset state to avoid control errors. For the MAX705, the reset threshold voltage is 4.65V, so when Vcc is lower than 4.65V, the system remains in reset. At the same time, connect Vcc to the PFI pin. When Vcc is lower than 1.25V, the PFO pin outputs a warning signal. If it is in the power warning state for a long time, a power failure may occur and should be dealt with.

When the system is running normally, the CTD4 channel of the CTM4 module of MC68HC376 regularly provides pulses to the WDI pin of MAX705 at an interval of less than 1.6s; once the system fails to operate normally and causes the WDI pin of MAX705 to lose pulses, the watchdog timer Overflow makes /WDO low. Since /WDO is connected to the manual reset pin /MR, the /RESET pin sends a low active reset signal to MC68HC376 to restore the system to the reset state.

2.2 External filter circuit

Since the system uses an external reference frequency source, in order to improve the stability and reliability of the system frequency, a filter circuit needs to be connected to the XFC pin of MC68HC376. This circuit should reduce the leakage current of the XFC pin as much as possible to improve the stability of the clock and the performance of the internal phase-locked loop. Figure 3 shows a highly stable filter circuit.

2.3 Output drive circuit reliability design

The control device provides control signals to the control and adjustment action units after monitoring and analyzing the system conditions. If the output signal is disturbed or an erroneous control signal is sent due to device failure, the system will be harmed due to erroneous regulatory control actions. Therefore, corresponding blocking control and anti-interference design should be implemented for the output drive circuit to improve the reliability of the control.

(1) Latching control circuit

The retriggerable bi/monostable multivibrator 74LS123 is used to form the output latching circuit. The circuit wiring is shown in Figure 4. Connect pin A of 74LS123 to the CTD4 channel of the CTM4 module of MC68HC376. Under normal circumstances, CTD4 provides pulses at regular intervals, so that the oscillator circuit cannot flip. At this time, /Q remains 1; if the device fails, CTD4 loses pulses. Then the oscillation circuit makes /Q flip to 0, so the latch signal becomes 0 and the output control signal is latched.

At the same time, the other pin of AND gate 4081 is connected to the TCH15 pin of the TPU module of MC68HC376, which is directly controlled by MC68HC376. In normal operation, when it is necessary to output a control signal, set TCH15 to 1; when it is not necessary to output a control signal, set TCH15 to 0, so that the blocking signal is 0 and the output part is blocked, thus preventing interference or other reasons. causing malfunction.

(2) Anti-interference design of the control signal output part

. When the latch signal is turned on, the output control signal may deviate due to disturbance. Therefore, the corresponding output circuit form should be designed to reduce the impact of disturbance. The form of the output circuit is shown in Figure 5 (only one output signal is shown here).

When using single-wire control, once interference occurs, the level of the control signal will change, causing malfunction. The "0,1" control method is used here, using two adjacent control lines, one is directly connected to the AND gate 4081, and the other is connected to the 4081 through the NOT gate 4069, that is, when the two control lines are "0,1" When outputting a valid level signal 1. In this way, when there is high disturbance or low disturbance such that the control line becomes 1 or 0 at the same time, an invalid level signal 0 is output. In this system, the CPWM7 pin of the CTM4 module and the latch signal are used to control the opening signal; the opening signal and the control signal of MC68HC376 are used to control the action output signal. This fully improves the reliability of output control. Note that the I/O control signal of the microcontroller should use a pull-up resistor.

2.4 Power-off alarm circuit

When a certain level of the working power supply of the system loses power, the control device will not be able to operate normally, or the control signal will not be executed correctly. At this time, an alarm signal should be issued. The power-down alarm circuit is shown in Figure 6. The working power supplies of each level are connected in series through the isolation MOC8050. Once a power failure occurs, the level of the power failure alarm changes from high to low, and the alarm device is activated. Software reliability design

2.5 Software watchdog

In the SIM module of MC68HC376, there is a software watchdog. In the monitoring program, the software watchdog can be turned on to improve the reliability of the system. The software watchdog is controlled by the SWE bit in the MC68HC376 system protection control register (SYPCR). When the SWE bit is 1, the watchdog starts and starts timing. When the device is working normally, the program should write 55H and AAH to the software service register (SWSR) before the software watchdog overflows. When the writing is completed, the software watchdog will clear the current timing value and restart timing.

If the timing value overflows, the /RESET pin of MC68HC376 will be valid and the system will be reset. In this way, it can automatically return to the reset state when the program is in an infinite loop or jumps due to other reasons.

The watchdog overflow time is determined by the system frequency and the watchdog divider bit (SWP) and watchdog time zone (SWT[1:0]) of the SYPCR register, as shown in Table 1. When choosing the watchdog overflow time, you should pay attention to the appropriate size. If the value is too large, the program may be in an infinite loop or jump state for a long time, resulting in control errors or failures; if the value is too small, the program will increase in size. burden and reduce the operating efficiency of the device.

2.6 Program area division and operation level control

CPU32 can perform two priority level operations: monitoring level and user level. At the monitor level, the CPU can operate on all internal integrated resources and all instructions, while at the user level, its access to some registers and instructions will be restricted. Effective use of this priority level in the program will allow controlled access to internal resources and some system instructions, thereby improving the reliability of system operation. The S bit in the status register SR of CPU32 determines the working level of the CPU. When S=1, the CPU is at the monitoring level; when S=0, the CPU is at the user level.

Generally, the program area and data area of the microcontroller are in the same physical address space. For MC68HC376, the external physical space can be expanded and divided through the function code FC[2:0], and external decoding of FC[2:0] can be implemented to enable monitoring-level programs, monitoring-level data, user-level programs, and user-level data respectively. Use separate address spaces. For each module inside MC68HC376, the address space where the general register of this part is located can be determined through the SUPV bit in the corresponding structural register. When SUPV=1, the relevant register is placed in the supervisory level data address space, and the CPU It can only be accessed and operated at the monitoring level; when SUPV=0, the relevant registers are placed in the data-level data address space, and the CPU can access and operate them at will. In this way, the entire program has a strong structure and controls access by level, which enhances the reliability of operation.

2.7 Bus Monitor

When MC68HC376 performs internal bus operations, the data strobe response pin (/DSACK) and the automatic vector pin (/AVEC) should have corresponding response signals. The bus monitor in the SIM module can monitor the /DSACK and /AVEC signals. When the response time exceeds the timing value, the bus error (/BERR) pin is valid. The program should monitor the status of /BERR so that bus errors can be handled accordingly in a timely manner.

The timing value of the bus monitor is determined by the bus monitoring time area (BMT[1:0]) in the system protection control register (SYPCR). When BMT[1:0]=00, the timing value is 64 system clocks; when BMT[1:0]=01, the timing value is 32 system clocks; when BMT[1:0]=10, the timing value is 16 system clocks; when BMT[1:0]=11, the timing value is 8 system clocks. Programmers should make choices based on actual operating conditions.

Other measures to improve reliability include configuring decoupling capacitors; the system clock circuit is powered by an independent power supply VDDSYN to reduce interference to the MCU, and the system clock can still maintain operation when the MCU is powered off. When wiring, the clock circuit is set in the center of the circuit board; the Standby RAM uses two power supplies, VDD and VSTBY, to supply power. VDD supplies power during normal operation. When a power outage occurs, it automatically switches to VSTBY for power supply. At the same time, in the software, storing the stack and some important data in Standby RAM is beneficial to the preservation of important operating parameters.

3 Conclusion

This solution uses the new 32-bit microcontroller MC68HC376 with high performance, high integration and strong reliability as the core. It also adopts a variety of design measures to improve system reliability in terms of hardware, software and board wiring. The digital low-frequency and low-voltage control device RSA800 using this solution has passed the product type test of the Electric Power Equipment and Instrument Quality Inspection and Testing Center of the Ministry of Electric Power Industry.

References

1 MC68336/376 user's manual. Motorola.Inc.1996

2 CPU32 reference manual. Motorola.Inc.1996

3 CTM configurable timer module reference manual. Motorola.Inc.1996

4 QADC queued analog-to-digital converter reference manual. Motorola .Inc.1996

5 SIM system integration module reference manual. Motorola.Inc.1996

6 QSM queued serial module reference manual. Motorola.Inc.1996

7 Wang Xingzhi et al. Anti-interference technology of single chip application system. Beijing University of Aeronautics and Astronautics Press. 1999

8 Wang Furui et al. Design Encyclopedia of Single-chip Microcomputer Measurement and Control Systems [M]. Beihang University Press. 1999

9 Li Hua et al. Practical interface technology for MCS-51 series single-chip microcomputer. Beihang University Press. 1993

Previous article:Studying transient processes using microcontroller data acquisition system

Next article:High reliability system design based on 32-bit microcontroller MC68HC376

Recommended ReadingLatest update time:2024-11-16 16:20

Professor at Beihang University, dedicated to promoting microcontrollers and embedded systems for over 20 years.

Professor at Beihang University, dedicated to promoting microcontrollers and embedded systems for over 20 years.

- Innolux's intelligent steer-by-wire solution makes cars smarter and safer

- 8051 MCU - Parity Check

- How to efficiently balance the sensitivity of tactile sensing interfaces

- What should I do if the servo motor shakes? What causes the servo motor to shake quickly?

- 【Brushless Motor】Analysis of three-phase BLDC motor and sharing of two popular development boards

- Midea Industrial Technology's subsidiaries Clou Electronics and Hekang New Energy jointly appeared at the Munich Battery Energy Storage Exhibition and Solar Energy Exhibition

- Guoxin Sichen | Application of ferroelectric memory PB85RS2MC in power battery management, with a capacity of 2M

- Analysis of common faults of frequency converter

- In a head-on competition with Qualcomm, what kind of cockpit products has Intel come up with?

- Dalian Rongke's all-vanadium liquid flow battery energy storage equipment industrialization project has entered the sprint stage before production

- Allegro MicroSystems Introduces Advanced Magnetic and Inductive Position Sensing Solutions at Electronica 2024

- Car key in the left hand, liveness detection radar in the right hand, UWB is imperative for cars!

- After a decade of rapid development, domestic CIS has entered the market

- Aegis Dagger Battery + Thor EM-i Super Hybrid, Geely New Energy has thrown out two "king bombs"

- A brief discussion on functional safety - fault, error, and failure

- In the smart car 2.0 cycle, these core industry chains are facing major opportunities!

- The United States and Japan are developing new batteries. CATL faces challenges? How should China's new energy battery industry respond?

- Murata launches high-precision 6-axis inertial sensor for automobiles

- Ford patents pre-charge alarm to help save costs and respond to emergencies

- New real-time microcontroller system from Texas Instruments enables smarter processing in automotive and industrial applications

- Crazy Shell AI open source drone GPIO (remote control indicator light control)

- Where can I get an evaluation board for Toshiba's rice-sized Bluetooth module?

- 16. Low-power intelligent TWS in-ear detection chip VK233DS, Shenzhen Yongjia Microelectronics is the first choice

- [Atria AT32WB415 Series Bluetooth BLE 5.0 MCU] PWM breathing light

- 30V8A stepper motor driver, step angle 1.8 degrees, required accuracy 0.1 degrees, should I choose chip or H bridge

- Can the 66AK2L06 SoC enable miniaturization of test and measurement equipment?

- Circuit diagram of leakage alarm automatic control socket

- How to detect mosquitoes using ultrasonic sensor circuit

- 2021 National College Student Electronics Competition Released

- Share the application manuals, library functions, routines and selection tables of the full range of MM32 MCU products of Lingdong Microelectronics

Siemens PLC from Beginner to Mastery with Color Illustrations (Yang Rui)

Siemens PLC from Beginner to Mastery with Color Illustrations (Yang Rui) 【Follow me Season 2 Episode 2】Arduion UR4 homework submission code

【Follow me Season 2 Episode 2】Arduion UR4 homework submission code

京公网安备 11010802033920号

京公网安备 11010802033920号