Ultrasonic motor (USM) has many advantages, such as being able to directly output low-speed high torque, fast transient response (up to ms level), high positioning accuracy (up to nm level), and no electromagnetic interference. The operation of USM requires two high-frequency AC power supplies with a certain amplitude, orthogonal (or adjustable) phase, and a frequency above 20 kHz. The amplitude, frequency, and phase of the driving signal source directly affect the performance of USM. In order to facilitate the performance test and research of USM, it is necessary to provide a test power supply that is adjustable in amplitude, frequency, and phase. In the past, ultrasonic drivers were mostly composed of discrete devices, such as the literature, and their circuit structure was complex. Although the literature used FPGA or CPLD to generate, the frequency change of the generated signal was discontinuous. The literature used a single-chip microcomputer and a dedicated DDS chip, which had the disadvantages of poor anti-interference and low reliability.

This article introduces the use of ALTERA's FPGA devices and VHDL programming based on DLL digital frequency direct synthesis technology (DDS). The two-phase four-way frequency and phase adjustable high-frequency PWM signals are generated by the phase accumulation method. The four gate drive signals of the H-bridge of the external power control circuit are used through the drive circuit and the optical coupling isolation circuit. The main circuit of the H-bridge is connected to the DC power after voltage regulation, isolation, rectification and filtering of the main power. The DC power is controlled by the gate drive signal to form an AC signal of a two-phase high-frequency PWM wave with adjustable amplitude, frequency and phase difference. After smoothing by an external inductor, the PWM wave signal is converted into a quasi-sine wave signal to achieve the performance test of the USM.

1 Power Control Circuit

As shown in Figure 1, the two-phase AC signals A and B applied to the USM are four-way pulse signals generated by the FPGA to control the MOS tube switch to control the on and off of the rectified and filtered DC power. Under the action of the H-bridge inverter shown in Figure 1, the DC power is inverted into a rectangular wave AC power with the same switching frequency as the inverter. After being smoothed by the series inductor, the two-phase high-frequency quasi-sine wave signal required by the USM is obtained. The amplitude of this signal can be adjusted by the voltage regulator of the main circuit. The phase difference between the A and B phases depends on the phase difference of the gate drive signals on both sides of the H-bridge, that is, the phase difference of the gate S1 and S2 (or S3 and S4) drive signals. The same-side bridge arm cannot be turned on at the same time to avoid large current passing through the MOS switch tube and damaging the switch tube. In theory, the two control signals on the same side should be complementary in phase to achieve push-pull output. Considering the delay characteristics of the switch device, the signal should have a certain delay when opening the gate, that is, the dead time. In view of the above analysis and the requirements of USM performance testing, the gate control signal should have a PWM high-frequency wave with a duty cycle greater than 50% and adjustable frequency, phase, and dead time.

2 Generation of PWM frequency modulation and phase modulation high frequency signals

The DDS design in the reference divides the amplitude of a rectangular wave into 2n equal parts and stores them in a table in order. The data (amplitude) is read in order of the addresses in the table using the high-frequency clock fclk. The phase accumulator can be used to read an amplitude information every M addresses. The frequency of the rectangular wave is proportional to the product of the input clock frequency and the phase increment M, which is M times the base frequency clock fclk/2n. The frequency of the signal can be adjusted by adjusting the step size M (frequency control word). The phase of the rectangular wave can be adjusted by adjusting the address of the ROM table read for the first time. The adjustment parameter is called the phase control word. If 0 and 1 in the ROM lookup table each account for half, a square wave signal with continuously adjustable frequency and phase can be obtained; changing the proportion of 1 in the table will result in a rectangular wave with different pulse widths. If the proportion of 1 can be adjusted externally, a PWM signal with adjustable frequency, phase, and duty cycle is generated. Since there are only two numbers 0 and 1 in the table, and both appear continuously, the comparator can be used to replace the ROM table, and the count value of the original address generation counter is divided into two parts, one part clears the output signal, and the other part sets it to 1. Compared with the two solutions, the latter greatly saves FPGA resources. The RTL level schematic is shown in Figure 2.

FWORD[16. . O] in the program design is the frequency control word M in the principle description, which is connected to the 32-bit counter F32[32. . 6]. The frequency of its output signal FOUT is calculated according to the following formula: FFOUT=fclk/222·FWORD, the frequency resolution is Fmin=25fclk/222, and the maximum output frequency is Fmax=Fmin FWORDmax. When the system frequency fclk=50MHz, Fmin=0.745 Hz, Fmax=97.648 kHz, that is, the output frequency can be adjusted between 0.7 and 97.6 Hz. The phase control word is 9 bits, and the phase of the output signal FOUT can be calculated according to the following formula: POUT=360°/2°×PWORD, and the minimum resolution is 360°/2°=0.7°. DIEIN[8. . O] is the duty cycle (dead zone) adjustment control word input. The duty cycle is calculated according to the formula: (29-DIEIN)/210x100%. The maximum duty cycle is 50% and the minimum is close to 0. The duty cycle is adjusted so that the two MOS tubes on the same side of the H bridge in Figure 1 are not turned on at the same time (so the duty cycle cannot be greater than 50%). If the duty cycle is too small, the conversion efficiency of the entire system will be reduced.

With the single-phase frequency-modulated phase-modulated PWM signal design as the underlying component, the structured description method (instantiation statement) of VHDL is used to set the four single-phase frequency-modulated phase-modulated signal DDS components to different phases according to the phase requirements. The phase word PWORD is 9 bits, U0: PWORD=0, initial phase=0; U2: PWORD="100000000", initial phase is 180°; the initial phase of the U1 component is PWOR-D, and the initial phase of the U2 component is PWORD+"00000000", which realizes that the phase difference between UO and U1 is PWORD, and the phase difference between U0 and U2, and U1 and U2 is 180° respectively, thus realizing the design of four-way frequency-modulated phase-modulated PWM signals.

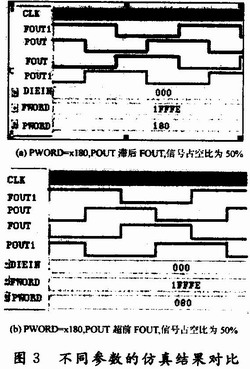

By adjusting FWORD, PWORD and DIEIN, the frequency, phase difference and duty cycle of the four output signals can be adjusted respectively. The simulation results are shown in Figure 3. From the simulation diagram, it can be seen that the four phase sequences obtained by leading 90° and lagging 90° are exactly opposite. If it is used to drive the four switches in Figure 1, two signals with a difference of 90° are obtained, one is that phase A leads phase B, and the other is that phase A lags phase B. Use it to drive USM, and without changing the motor connection, by adjusting the phase difference PWORD, the rotation direction of the motor can be easily controlled.

3 Experimental tests

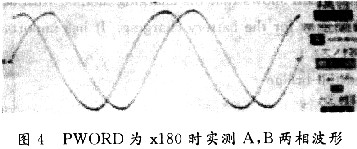

The above four control signals are downloaded to the FPGA, and then applied to the power control circuit of Figure 1 after passing through the drive isolation module introduced in the document. The A and B two-phase waveforms of USM are measured by an oscilloscope as shown in Figure 4. The signal obtained by the above circuit is applied to the drive of the USM45 ultrasonic motor. The required drive signal frequency of the motor is 45.8 kHz, the phase difference is 90°, and the peak-to-peak value can reach 300 V. The frequency control word is set to FWORD=x0F000, the phase control word is PWORD=x180 (or x080), and the dead time DIEIN=x33~xFF is adjusted to successfully drive the USM 45 motor. After running for about 10 minutes, the motor speed decreases. By reducing FWORD to xED00, that is, when the signal frequency is 45.2 kHz, the motor speed rises to the initial value (65 rpm). Ultrasonic motors generally work between the resonance and anti-resonance points of the stator admittance 2 frequency characteristic. As the motor operating temperature increases, the harmonic frequency and anti-resonance frequency change by about 1.4 kHz. Since the USM45 motor has a small power, the rated power is only 2 W, and it is tested under no-load, the temperature rise is small, and the change of the resonant frequency is also small (only about 0.6 kHz).

4 Conclusion

The four-way frequency modulation and phase modulation PWM signals generated by FPGA according to the phase accumulation oscillator method have high frequency resolution and can achieve fast frequency switching under the premise of maintaining phase continuity. This signal not only successfully drives and tests the USM45 motor under the action of the external inverter circuit, but can also be conveniently applied to the driving of stepper motors and DC motors, as well as the frequency modulation and speed regulation of stepper motors and the PWM speed regulation of DC motors by adding a dedicated L298N driver chip.

Previous article:A mixed-signal universal battery charger design

Next article:How to Design a Power Supply for a Multi-Load System

Recommended ReadingLatest update time:2024-11-16 16:17

- Popular Resources

- Popular amplifiers

-

Analysis and Implementation of MAC Protocol for Wireless Sensor Networks (by Yang Zhijun, Xie Xianjie, and Ding Hongwei)

Analysis and Implementation of MAC Protocol for Wireless Sensor Networks (by Yang Zhijun, Xie Xianjie, and Ding Hongwei) -

MATLAB and FPGA implementation of wireless communication

MATLAB and FPGA implementation of wireless communication -

Intelligent computing systems (Chen Yunji, Li Ling, Li Wei, Guo Qi, Du Zidong)

Intelligent computing systems (Chen Yunji, Li Ling, Li Wei, Guo Qi, Du Zidong) -

Summary of non-synthesizable statements in FPGA

Summary of non-synthesizable statements in FPGA

- MathWorks and NXP Collaborate to Launch Model-Based Design Toolbox for Battery Management Systems

- STMicroelectronics' advanced galvanically isolated gate driver STGAP3S provides flexible protection for IGBTs and SiC MOSFETs

- New diaphragm-free solid-state lithium battery technology is launched: the distance between the positive and negative electrodes is less than 0.000001 meters

- [“Source” Observe the Autumn Series] Application and testing of the next generation of semiconductor gallium oxide device photodetectors

- 采用自主设计封装,绝缘电阻显著提高!ROHM开发出更高电压xEV系统的SiC肖特基势垒二极管

- Will GaN replace SiC? PI's disruptive 1700V InnoMux2 is here to demonstrate

- From Isolation to the Third and a Half Generation: Understanding Naxinwei's Gate Driver IC in One Article

- The appeal of 48 V technology: importance, benefits and key factors in system-level applications

- Important breakthrough in recycling of used lithium-ion batteries

- Innolux's intelligent steer-by-wire solution makes cars smarter and safer

- 8051 MCU - Parity Check

- How to efficiently balance the sensitivity of tactile sensing interfaces

- What should I do if the servo motor shakes? What causes the servo motor to shake quickly?

- 【Brushless Motor】Analysis of three-phase BLDC motor and sharing of two popular development boards

- Midea Industrial Technology's subsidiaries Clou Electronics and Hekang New Energy jointly appeared at the Munich Battery Energy Storage Exhibition and Solar Energy Exhibition

- Guoxin Sichen | Application of ferroelectric memory PB85RS2MC in power battery management, with a capacity of 2M

- Analysis of common faults of frequency converter

- In a head-on competition with Qualcomm, what kind of cockpit products has Intel come up with?

- Dalian Rongke's all-vanadium liquid flow battery energy storage equipment industrialization project has entered the sprint stage before production

- Allegro MicroSystems Introduces Advanced Magnetic and Inductive Position Sensing Solutions at Electronica 2024

- Car key in the left hand, liveness detection radar in the right hand, UWB is imperative for cars!

- After a decade of rapid development, domestic CIS has entered the market

- Aegis Dagger Battery + Thor EM-i Super Hybrid, Geely New Energy has thrown out two "king bombs"

- A brief discussion on functional safety - fault, error, and failure

- In the smart car 2.0 cycle, these core industry chains are facing major opportunities!

- The United States and Japan are developing new batteries. CATL faces challenges? How should China's new energy battery industry respond?

- Murata launches high-precision 6-axis inertial sensor for automobiles

- Ford patents pre-charge alarm to help save costs and respond to emergencies

- New real-time microcontroller system from Texas Instruments enables smarter processing in automotive and industrial applications

- Differential Amplification

- Cadence Problem

- Detailed analysis of the working mode of the microcontroller IO port

- Purgatory Legend-PS2 Interface War

- DSP C language IIR filter program source code

- 【Smart network desk lamp】8. Maix bit driver RGB

- How does GD32 replace STM32?

- Starting from 0, learn the 10 terms you need to know about PCB

- [Evaluation of domestic FPGA Gaoyun GW1N-4 series development board]——11. Click on the LCD1602 screen

- Back to Basics: Exploring the Benefits of Affordable Bluetooth Low Energy

Analysis and Implementation of MAC Protocol for Wireless Sensor Networks (by Yang Zhijun, Xie Xianjie, and Ding Hongwei)

Analysis and Implementation of MAC Protocol for Wireless Sensor Networks (by Yang Zhijun, Xie Xianjie, and Ding Hongwei)

京公网安备 11010802033920号

京公网安备 11010802033920号