1.

As an important part of modern electronic products, background signal sources must meet the requirements of high precision, high speed, and high resolution. As a dynamic signal source for inspecting high-precision radar equipment, it is even more necessary to meet these requirements. In the daily maintenance of radar measurement equipment, since it is neither possible nor possible to use tracking dynamic targets to complete the equipment performance inspection, the signal source is used to generate signals for inspection, and the signal source cannot simulate the actual dynamic signal, so in most cases The dynamic performance of the device cannot be accurately checked. This article studies and implements an intelligent dynamic signal source based on FPGA (Field Programmable Gate Array), using DDS (Direct Digital Synthesis) technology. The solution combining FPGA and DDS shows many outstanding advantages: high frequency resolution; ultra-wide frequency range; the ability to generate various modulated waves and arbitrary waveforms; and the key parts are easy to realize full digitization.

2 DDS principle and theoretical analysis

2.1 DDS principle

DDS is "direct digital frequency synthesis", which is a relatively new frequency synthesis technology. After several years of development, it has now matured and is widely used. The basic principle of this technology is to use a highly stable reference clock source to quantify the sampling time interval, directly sample, quantize and signal the signal to be generated, and then output the required analog signal through D/A conversion and low-pass filtering. The principle is shown in Figure 1.

|

Under normal circumstances, the number of bits in the accumulator is generally relatively high to obtain high frequency and phase resolution. However, considering the following two reasons, the general function generator only uses the high M bits of the N-bit accumulator and discards them. Its low bits: first, the memory capacity of the RAM of the function generator (waveform memory) is limited; second, due to the accuracy limit of digital/analog conversion and the influence of external interference, as the number of bits increases, the resolution of its output amplitude value decreases. It cannot be increased without limit.

2.2 Theoretical analysis

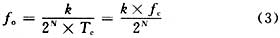

2.2.1 DDS output frequency expression

fc is the reference clock frequency, Tc=1/fc; fo is the output frequency, To=1/fo; k is the frequency control word, that is, the phase increment.

Suppose the length of the accumulator is N bits, and the function generator produces a periodic sine wave whose output is M bits (the highest M bit among the N bits, M

360°/2M (1)

Similarly, the LSB in N bits is equivalent to 2π/2N radians. The 360°/2N radians is the minimum phase increment. Therefore, the phase increment corresponding to the k value is k*2π/2N radians. In this way, it takes 2π/(K*2π/2N) reference clock cycles to complete one cycle of sine wave output, that is, 2N/K cycles. Therefore, the period of the output frequency can be obtained as:

It can be seen that the output frequency fo is proportional to the frequency control word k. If the output frequency fo is known, the frequency control word k can be calculated.

2.2.2 Frequency resolution of the system

When k=1, the corresponding output frequency is the lowest frequency value that can be output, that is, the frequency resolution:

fo=fc/2N (4)

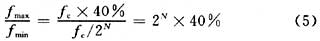

2.2.3 The highest frequency that the system can output.

In theory, the highest frequency that the system can output is mainly limited by the Nyquist frequency. According to the sampling theorem, when k=2N-1, the system output reaches the highest frequency of the theoretical output: fo=fc/2. However, in the actual designed DDS system, the maximum output frequency of the design must be less than fc/2 due to the following reasons: First, the non-ideality of the output filter. Generally, the maximum frequency of the output signal is 40% of the reference clock frequency fc. Second, if a sinusoidal signal is generated, and the output frequency is half of the sampling clock, and the sampling point is exactly at zero, the required signal cannot be generated. However, from the analysis of the above points, the DDS system can obtain a very wide frequency adjustment range, and its relative bandwidth is:

3 Design of dynamic signal generator

3.1 The system block diagram of dynamic signal generation process

is shown in Figure 2. The digital part of DDS, the core part of the dynamic signal generator, is implemented with FPGA. At the same time, the FPGA also receives external control signals and generates synchronization signals used to control the operation of the entire circuit, and sends the FPGA working status to the PC microcomputer. In Figure 2, the NCO, D/A conversion and filter circuit constitute the DDS circuit. The register is used to store the frequency control code that generates dynamic signals; the clock processing circuit is used to generate sampling clock signals and synchronization signals; the serial port circuit is used to complete the task of interfacing with the microcomputer and receive control signals and data from the microcomputer. The NCO consists of a latch, phase accumulator and waveform memory (RAM). The latch serves as a phase increment register, and the phase accumulator is used to implement the accumulation of addresses, and the address information is used to obtain the corresponding waveform data from the waveform memory. The waveform memory is used to store various waveform data, and a variety of signal waveform data can be generated by the computer, thereby realizing the multi-function of the signal source. After passing through the waveform memory, these digital signals are converted into digital/analog signals to obtain analog signals. Finally, the signal is filtered, amplified and output through the operational amplifier and filter shaping circuit.

|

It can be seen from expression (3) that as long as the frequency control code k changes, the output frequency changes accordingly, thereby achieving a change in signal frequency.

In Figure 2, the part within the dotted line is the FPGA part, and the part outside the dotted line mainly serves the FPGA. The memory completes the function of configuring the FPGA; the interface circuit completes the level conversion function, mainly converting the TTL level output by the FPGA into the RS 232 standard level.

The filter design uses a crystal filter to filter out the phase noise of the generated dynamic signals to meet the needs of radar equipment applications.

3.2 Key parameter design

3.2.1 Reference clock selection

Since the frequency of the signal to be generated is 5 MHz, it can be seen from the above analysis that the reference clock must be greater than:

fc=25 MHz is selected here.

3.2.2 Selection of accumulator digits

The selection of accumulator digits mainly depends on the frequency resolution of the 5 MHz signal. The resolution required by this dynamic 5 MHz signal generator is δ=8×10-5Hz. According to the expression (4), the number of digits N in the accumulator can be calculated.

Among them, fc=25 MHz is the clock frequency, δ is the resolution, then the number of bits in the phase accumulator is:

Take the number of bits of the NCO phase accumulator to be N=40.

3.2.3 Selection of the number of digits of the function generator

The selection of the digits of the function generator mainly depends on the phase resolution of the output 5 MHz signal. The required resolution of this dynamic 5 MHz signal generator is a=0.034°, then According to expression (1), the number of digits of the function generator can be calculated as:

M=14.

3.3 Main chip selection

3.3.1 Selection of FPGA chip

Since the frequency control code needs to be completely loaded into the RAM of the FPGA before generating dynamic signals, the RAM of the FPGA must meet certain requirements. The calculation process is as follows:

the time length for generating dynamic signals is set to 500 s, and the frequency control codes per second are 80, so there are a total of: 500×80=40 000 frames of data. Each frame of data is 16 bits, and the total number of register bits required is: 40 000 × 16 = 640 000. A function generator also needs to be implemented in the NCO. The address width of the function generator is 14 bits, and the data width is also 14 bits. The number of registers required is: 214×14=229 367. So the final number of register bits required is: 640 000+229 376=869 376.

Secondly, there must be a dedicated clock processing circuit in the FPGA, with at least 2 PLLs. NCO requires many clocks, and there is a strict timing relationship between clocks. The main types of clocks include: clock required for digital/analog conversion; serial port clock; reference clock; 80 Hz signal.

Altera's Stratix chip can meet the needs. The core voltage of the chip is 1.5 V, using O. 13 μm, made with all-copper technology, with a maximum register capacity of ~Mb.

3.3.2 Selection of digital-to-analog conversion chip

The number of digits of the phase accumulator is 14 bits, so the number of digits of the D/A conversion device must also be 14 bits. After selection and comparison, AD Company's AD9754 digital/analog conversion device can meet the requirements. The digital/analog converter has 14-bit accuracy and a maximum adjustment rate of 125 MSPS. It integrates a two-level input register and a reference current source on the chip, so the circuit design is simple and the operation is flexible. It only requires fewer external components to complete the data. /Analog conversion function.

AD9754 is a current-mode output device and requires current-to-voltage conversion. It is planned to use the AD9631 operational amplifier of AD Company to complete the current-to-voltage conversion function. The unit gain bandwidth of this operational amplifier is 175 MHz in the case of large signals and wider in the case of small signals. The supply voltage is ±5 V, and the output slew rate is 1300 V/μs.

3.4 Algorithm design

Software design mainly includes configuring FPGA, calculating waveform data and frequency control code data. At the same time, the software also needs to complete the monitoring and display tasks. VC++ is used for software development and Windows NT is used for operating system. The frequency control code is calculated by the software and sent to the RAM of the FPGA through the serial port. Waveform data can be written into the RAM of the FPGA in the form of an initialization file, and can be written into sine waves, triangle waves, square waves and other waveforms, as well as various modulation waveforms. Different waveform data are distinguished by the function generator address, so that the waveform of the output signal can be changed at any time. After the system control command is issued, it can work offline.

3.4.1 Frequency control code algorithm

According to expression (3), the expression for calculating the frequency control code can be obtained as follows:

k=(fo×2N)/fc

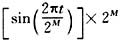

3.4.2 The waveform data algorithm

expression is as follows:

Among them, M is the data width of the function generator, here it is 14, t is the time unit, here it is an integer, the value range is: 0, 1,..., 2M-1, in fact t is the input address value of the function generation .

4. Generate signal waveform diagram.

During the debugging stage, the design was verified using the FPGA development board and it worked normally. The waveform is shown in Figure 3.

|

As can be seen from Figure 3, the output is a 5 MHz digital signal, which is generated under the condition of fixed frequency control code increment. After multiple samplings and waveform comparisons, its frequency changes. Since there are only 5 sampling points in one cycle, the signal waveform does not look very smooth. Observing the spectrum through the 8566A spectrum analyzer, the spectrum characteristics of the generated 5 MHz signal are very good, with clutter suppression above 70 dB and harmonic suppression above 45 dB.

5 Conclusion

The high-precision radar equipment is inspected through the generated dynamic 5 MHz signal, which proves that this solution is feasible and can complete the inspection of the dynamic performance of the equipment, making the maintenance of the equipment more targeted.

Previous article:Design of wide-band digital phase-locked loop and implementation based on FPGA

Next article:Design and verification of DDR read and write control using FPGA IP

Recommended ReadingLatest update time:2024-11-16 17:42

- Huawei's Strategic Department Director Gai Gang: The cumulative installed base of open source Euler operating system exceeds 10 million sets

- Analysis of the application of several common contact parts in high-voltage connectors of new energy vehicles

- Wiring harness durability test and contact voltage drop test method

- Sn-doped CuO nanostructure-based ethanol gas sensor for real-time drunk driving detection in vehicles

- Design considerations for automotive battery wiring harness

- Do you know all the various motors commonly used in automotive electronics?

- What are the functions of the Internet of Vehicles? What are the uses and benefits of the Internet of Vehicles?

- Power Inverter - A critical safety system for electric vehicles

- Analysis of the information security mechanism of AUTOSAR, the automotive embedded software framework

Professor at Beihang University, dedicated to promoting microcontrollers and embedded systems for over 20 years.

Professor at Beihang University, dedicated to promoting microcontrollers and embedded systems for over 20 years.

- Innolux's intelligent steer-by-wire solution makes cars smarter and safer

- 8051 MCU - Parity Check

- How to efficiently balance the sensitivity of tactile sensing interfaces

- What should I do if the servo motor shakes? What causes the servo motor to shake quickly?

- 【Brushless Motor】Analysis of three-phase BLDC motor and sharing of two popular development boards

- Midea Industrial Technology's subsidiaries Clou Electronics and Hekang New Energy jointly appeared at the Munich Battery Energy Storage Exhibition and Solar Energy Exhibition

- Guoxin Sichen | Application of ferroelectric memory PB85RS2MC in power battery management, with a capacity of 2M

- Analysis of common faults of frequency converter

- In a head-on competition with Qualcomm, what kind of cockpit products has Intel come up with?

- Dalian Rongke's all-vanadium liquid flow battery energy storage equipment industrialization project has entered the sprint stage before production

- Allegro MicroSystems Introduces Advanced Magnetic and Inductive Position Sensing Solutions at Electronica 2024

- Car key in the left hand, liveness detection radar in the right hand, UWB is imperative for cars!

- After a decade of rapid development, domestic CIS has entered the market

- Aegis Dagger Battery + Thor EM-i Super Hybrid, Geely New Energy has thrown out two "king bombs"

- A brief discussion on functional safety - fault, error, and failure

- In the smart car 2.0 cycle, these core industry chains are facing major opportunities!

- The United States and Japan are developing new batteries. CATL faces challenges? How should China's new energy battery industry respond?

- Murata launches high-precision 6-axis inertial sensor for automobiles

- Ford patents pre-charge alarm to help save costs and respond to emergencies

- New real-time microcontroller system from Texas Instruments enables smarter processing in automotive and industrial applications

- EEWORLD University Hall----Live Replay: Energy Saving and Carbon Reduction-Omron Relay, Switch, and Connector Solutions for Photovoltaic Inverter/Energy Storage Systems

- Nonlinear Compensation Method for Sensor Bridge Circuit

- DIY_boostxl-k350qvg under the recent proofing storm

- Today is 520, another beautiful day for confession. What actions will you take?

- Design and Implementation of Digital Video Conversion Interface Based on FPGA

- CR Micro's 8-bit microcontroller CS98P154 with OTP ROM

- Creative Electronics: DIY Wireless Charger for Your Phone

- Specifications of several types of batteries

- [Lazy people take care of fish tank control system] Debug method in ON Semiconductor IDE environment

- W5500 UDP Issues

MATLAB and FPGA implementation of wireless communication

MATLAB and FPGA implementation of wireless communication CVPR 2023 Paper Summary: Robotics

CVPR 2023 Paper Summary: Robotics

京公网安备 11010802033920号

京公网安备 11010802033920号