CPLD (Complex Programmable Logic Device) is a complex user-programmable logic device that uses a continuous connection structure. This structure makes it easy to predict delays, making circuit simulation more accurate. CPLD is a standard large-scale integrated circuit product that can be used in the design of various digital logic systems. In recent years, due to the use of advanced integration processes and mass production, the cost of CPLD devices has continued to decline, and the integration density, speed and performance have been greatly improved. A single chip can realize a complex digital circuit system; coupled with easy-to-use development tools, the use of CPLD devices can greatly shorten the product development cycle and bring great convenience to design and modification [1]. This article takes the MAX7000 series of ALTERA as an example to realize parallel communication between the MCS51 microcontroller and the PC104 ISA bus. Using this communication method, data transmission is accurate and high-speed. In the data acquisition system controlled by the MCS51 microcontroller with a 12 MHz crystal oscillator, it can meet the requirements of real-time communication with the PC104 ISA bus interface, and the communication rate reaches 200 Kbps.

1 Overall system design

This system uses CLPD to realize parallel communication between the microcontroller and the PC104 ISA bus interface. Since PC104 mainly completes other data collection work and can only receive data sent by the microcontroller when it is idle, the real-time communication between the two parties is required to be very strong, but the amount of data is not large. Therefore, in the system design, the microcontroller receives data in interrupt mode, and PC104 receives data in query mode. The system design is shown in Figure 1.

In the microcontroller part of Figure 1, D[0..7] is the data bus, A[0..15] is the address bus, RD and WR are the read and write signal lines respectively, and INT0 is the external interrupt of the microcontroller. When the external interrupt signal of the microcontroller is valid, the microcontroller receives data.

In the CPLD part, a MAX7000 series EPM7128LSC84 is used to complete the data transmission, status query and delay waiting between MCS51 and PC104ISA bus interface.

In the PC104 ISA part, only the ISA 8-bit data bus D[0..7] is used, and A[0..9] is the address bus of PC104; IOW and IOR are read and write signals for the specified device; AEN allows DMA to control the address bus, data bus and read and write command lines for DMA transfer, as well as read and write of memory and I/O devices; IOCHRDY is the I/O ready signal, and the I/O channel ready is high. At this time, the memory read and write cycle generated by the processor is 4 clock cycles, and the generated I/O read and write cycle and DMA byte transfer require 5 clock cycles. MCS51 inserts a wait cycle into the CPU by setting this signal to a low level, thereby extending the I/O cycle; SYSCLK is the system clock signal, which is used to keep in sync with external devices; RESETDR is the power-on reset or system initialization logic, and is the system total clear signal. 2 Hardware implementation based on MAX+plus II

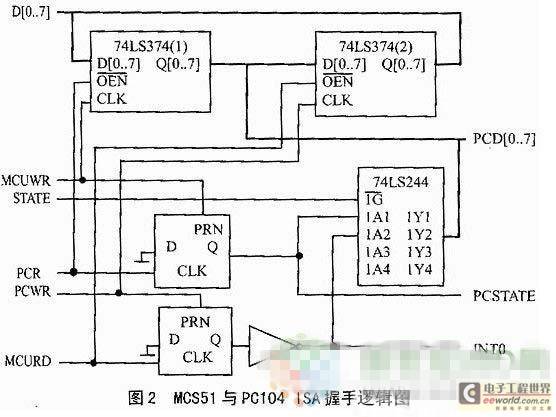

This system uses the CPLD development tool MAX+plusII of ALTERA. It supports multiple input methods, which provides great convenience for design and development. The main part of the system still uses the schematic input method. Since the current chips are provided in the library, it is very convenient to use. The schematic input part is shown in Figure 2 and Figure 3. Figure 2 mainly completes the data transmission and handshake judgment in the communication between the microcontroller and the ISA interface.

D[0..7] 8-bit bidirectional data bus of the microcontroller;

PCD[0..7] 8-bit bidirectional data bus of ISA interface;

PCRD ISA interface read valid signal;

PCWR ISA interface write valid signal;

Determine whether the microcontroller has written data or read data;

PCSTATE The microcontroller uses this to query the ISA interface to take away data;

MSCRD microcontroller read valid signal;

MCSWR microcontroller write valid signal;

INT0: external interrupt signal of the microcontroller;

When the MCUWR signal is valid, the microcontroller latches the data in 74LS374 (1). At this time, PCSTATE becomes high. PC104 uses the STATE signal to select 74LS244 to determine whether the data bit PCD0 is high. If it is high, it means that the microcontroller has sent data, so PCRD is enabled and the data is taken from the data memory 74LS374 (1). At this time, PCSTATE becomes low. The microcontroller determines that PC104 has taken the data by judging that this signal is low, and can send the next data.

When the PCWR signal is valid, PC104 latches the data in 74LS374 (2). At this time, INT0 becomes low, and the microcontroller generates an external interrupt, making the MCSRD signal valid, taking out the decoration from the data latch 74LS374 (2), and INT0 becomes high. PC104 uses the STATE signal to select 74LS244 to determine whether the data bit PCD1 is high. If it is high, it means that the microcontroller has taken the data and can send the next data. The most critical issue for PC104 to communicate with the microcontroller is speed matching. Since the speed of PC104 is fast and the speed of the microcontroller is slow, a wait cycle must be inserted at the IOCHRDY of PC104, as shown in Figure 3.

IOCHRDY is used to make the ISA interface wait for 5 clock cycles;

DLY_D delay input signal;

DLY_CK Delay wait clock

DLY_CLR waits for the clear signal to prepare for the next data transmission cycle;

DELAY delays the output signal by 5 clock cycles and serves as the input of the DLY_CLR signal;

SYSCLK System clock signal of the ISA interface.

During the communication between MCS51 and PC104, the DLY_D signal is always valid (high level). Under the action of the signal SYSCLK, the DELAY signal is valid once every 5 clock cycles, that is, it is high level. At this time, the DLY_CLR signal is valid (low level), the IOCHRDY signal becomes high level, and PC104 can read and write data.

The address decoding part uses text input, using ALTERA's hardware design and development language AHDL (Altera Hardware Description Language). AHDL is a modular high-level language that is fully integrated into the MAX+plusII system and is particularly suitable for describing complex combinational logic, state machines, and truth tables. The address decoding part uses text input, which fully demonstrates the advantages of text input. The text input content is as follows: SUBDESIGN Address

(PCA[9..0] : INPUT;

AEN,IOR,IOW : INPUT;

RESETDR,DELAY : INPUT;

A[15..14] :INPUT;

RD,WR : INPUT;

DLY_D : OUTPUT;

DLY_CK : OUTPUT;

DLY_CLR : OUTPUT;

STATE : OUTPUT;

PCRD : OUTPUT;

PCWR : OUTPUT;

MCURD : OUTPUT;

MCUWR: OUTPUT;)

BEGIN

!DLY_CLR=RESETDR#DELAY;

DLY_D=!AEN & (PCA[9..1]= =H"110");

DLY_CK=!AEN & (PCA[9..1]= =H"110")&(!IOR # ! IOW);

!PCWR=!AEN&(PCA[9..0]= =H"220")& !IOW;!PCRD=!AEN&(PCA[9..0]= =H"220")& !IOR;

!STATE=!AEN&(PCA[9..0]= =H"221")&!IOR;

!MCSRD=([15..14]= =H"1")& !RD;

!MCSWR=(A[15..14]= =H"2"& !WR;

END;

Note: PCA[9..0] is the address signal of PC104, A[15..14] is the address signal of the microcontroller, and PC104 uses port addresses 220H and 221H.

3 Communication Software Design

PC104 is based on the ISA bus. Address conflicts must be avoided in system software design. PC104 uses address bits A0 to A9 to represent I/O port addresses, which means there are 1024 port addresses: the first 512 are used by the system board, and the last 512 are used by the expansion slot. When A9=0, it represents the port address on the system board; when A9=1, it represents the port address on the expansion slot interface card [2]. Therefore, the reserved port addresses 220H and 221H are used to ensure that address conflicts will not occur.

In this program, PC104 uses query mode to receive data, and the microcontroller uses interrupt mode to receive data.

#define pcreadwrite 0x220 /*PC104 read and write data port address*/

#define pcrdstate 0x221 /*PC104 query status port address*/

PC104 write data function:

{ outportb(pcreadwrite,ch);

while ((inportb(pcrdstate)&0x02)!=0x02); /*Wait for the MCU to read the data*/

{ }

}

MCU reading subroutine:

MCUWR: MOV DPTR, #4000H

MOVX A, @DPTR

RETI

PC104 read data function:

Unsigned char pcread(int port)

{ while((inportb(pcrdstate)&0x01)!=0x01);/*Wait for the MCU to write data*/

{}

return inportb(pcreadwrite);

}

MCU write subroutine:

MCUWR: MOV DPTR, #8000H

MOVX@DPTR,A

; Wait for PC104 to read data

RET

4 Conclusion

Using CPLD to realize parallel communication between single-chip microcomputer and ISA bus interface has simple circuit structure and small size. One CPLD chip is enough. It is easy to control, has strong real-time performance and high communication efficiency. This design method has been successfully applied to various data acquisition systems developed by the author, used as parallel data communication between single-chip microcomputer and PC104, and the effect is very ideal.

Previous article:Design and breakthrough of automotive LED lighting drive system

Next article:Is the time right for intelligent LED drive control?

- Popular Resources

- Popular amplifiers

- MathWorks and NXP Collaborate to Launch Model-Based Design Toolbox for Battery Management Systems

- STMicroelectronics' advanced galvanically isolated gate driver STGAP3S provides flexible protection for IGBTs and SiC MOSFETs

- New diaphragm-free solid-state lithium battery technology is launched: the distance between the positive and negative electrodes is less than 0.000001 meters

- [“Source” Observe the Autumn Series] Application and testing of the next generation of semiconductor gallium oxide device photodetectors

- 采用自主设计封装,绝缘电阻显著提高!ROHM开发出更高电压xEV系统的SiC肖特基势垒二极管

- Will GaN replace SiC? PI's disruptive 1700V InnoMux2 is here to demonstrate

- From Isolation to the Third and a Half Generation: Understanding Naxinwei's Gate Driver IC in One Article

- The appeal of 48 V technology: importance, benefits and key factors in system-level applications

- Important breakthrough in recycling of used lithium-ion batteries

- LED chemical incompatibility test to see which chemicals LEDs can be used with

- Application of ARM9 hardware coprocessor on WinCE embedded motherboard

- What are the key points for selecting rotor flowmeter?

- LM317 high power charger circuit

- A brief analysis of Embest's application and development of embedded medical devices

- Single-phase RC protection circuit

- stm32 PVD programmable voltage monitor

- Introduction and measurement of edge trigger and level trigger of 51 single chip microcomputer

- Improved design of Linux system software shell protection technology

- What to do if the ABB robot protection device stops

- Keysight Technologies Helps Samsung Electronics Successfully Validate FiRa® 2.0 Safe Distance Measurement Test Case

- Innovation is not limited to Meizhi, Welling will appear at the 2024 China Home Appliance Technology Conference

- Innovation is not limited to Meizhi, Welling will appear at the 2024 China Home Appliance Technology Conference

- Huawei's Strategic Department Director Gai Gang: The cumulative installed base of open source Euler operating system exceeds 10 million sets

- Download from the Internet--ARM Getting Started Notes

- Learn ARM development(22)

- Learn ARM development(21)

- Learn ARM development(20)

- Learn ARM development(19)

- Learn ARM development(14)

- Sha Zhanyou's new monolithic switching power supply design and application technology

- Study Help Post

- stm32L011D3P6 program download problem

- LTC3631EMS8E 12V to 5V circuit schematic

- How to measure the exact time of OVP and UVP triggering with BQ30Z55

- TMS320DM642StudyReport

- W806 Lianshengde 9.9 yuan development board experience 3 --- littlevgl8.0 transplantation display success

- [Open Source] Test Program Introduction - Crazy Shell Development Board Series

- [2022 Digi-Key Innovation Design Competition] [PLC based on the Internet of Things] --- Design background and goals

- [NUCLEO-L452RE Review] +Serial Port Interrupt Receive

TLE2161IP

TLE2161IP

京公网安备 11010802033920号

京公网安备 11010802033920号