Introduction

ADC is a key component in the interface between analog systems and digital systems. It has long been widely used in communications, military and consumer electronics and other fields. With the rapid development of the computer and communications industries, the application of ADCs in portable devices has developed rapidly. Gradually develop towards high speed, high precision and low power consumption.

The currently dominant ADC types on the market mainly include: successive approximation type (SAR), Σ-Δ type, and pipeline type. The Σ-Δ type can achieve very high resolution, and the pipeline type can ensure high sampling rates. Both architectures are designed to meet vertical markets with specific needs. SAR ADC is a common structure for medium and high-resolution applications with sampling rates below 5MSPS. Since it essentially uses a binary search algorithm, the internal circuit can run at several MHz, and the sampling rate is mainly determined by the successive approximation algorithm.

This article designs an 8-channel 12-bit serial output ADC based on the 0.6μm BiCMOS process of SAIC. The conversion core circuit adopts a successive approximation structure, and on the basis of summarizing and improving the traditional structure, a composite of voltage scaling and charge scaling is used. This "5+4+3" segmented composite structure not only avoids the matching problem caused by large capacitors, but also reduces the linear error of the circuit itself due to the introduction of resistors. The comparator is implemented using The multi-pole cascade amplifier structure reduces the design complexity, and finally the overall layout design is realized based on the CSMC 0.6μm BiCMOS process.

|

system structure

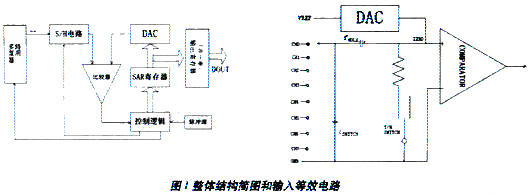

The SAR ADC circuit structure mainly consists of five parts, the sample and hold circuit, the comparator, the DAC, the successive approximation register and the logic control unit. The successive approximation in the conversion is completed by the control logic circuit according to the bisection principle. The working process is as follows: After starting, the control logic circuit first sets the highest position of the successive approximation register to 1 and other positions to 0, stores it in the successive approximation register, and then obtains a voltage value (about half of the full-scale output) after digital-to-analog conversion. This voltage value is compared with the input signal in a comparator, and the output of the comparator is fed back to the DAC and corrected before the next comparison. That is, the sample value of the input signal is subtracted from the initial output value of the DAC, and the remainder is quantized by the comparator. The quantized value then guides the control logic to increase or decrease the output of the DAC, and then subtracts the new DAC from the input sample value again. output value. This process is repeated until the realization of the last digit is completed. It can be seen that this data transformation is always driven by the clock of the logic control circuit, and the register is successively approached to continuously perform comparison and shift operations until the least significant bit is completed. (LSB) conversion, at this time, the values of each bit in the successive approximation register have been determined, and the conversion operation is completed.

Since this design is aimed at serial multi-channel conversion technology, this article is based on the basic structure of SAR ADC, adding a multiplexing module to the front end of the analog input, and adding a parallel-to-serial conversion circuit to the output back end.

In order to achieve fast and accurate conversion of signals, the important components in the SAR ADC are the sample and hold circuit, comparator and DAC. The equivalent input circuit is shown in Figure 1. During the acquisition of data, the selected channel is used as an input to charge the capacitor CHOLD, and the acquisition time After the end, the T/H switch is turned on, and the charge is maintained on CHOLD as a signal sample, which is compared with the analog signal generated in the DAC. The comparison result is input into the parallel/serial output register, and the digital bit is output under the control of the three-state bus.

Circuit design and implementation

The performance of the sample/hold circuit limits the speed and accuracy of the entire ADC. Double differential backplane sampling technology is used in the design. The double differential structure obtains excellent AC performance. In addition, the application of backplane sampling technology is also greatly Errors caused by charge injection, clock feedthrough, and limited bandwidth are reduced. Optimized overall performance. The comparator is implemented using three amplification cascade structures, which not only greatly improves the gain, but also reduces the design difficulty of the comparator and improves circuit performance. The following focuses on the design and implementation of the DAC.

The speed and resolution of the SAR ADC are mainly limited by the speed, resolution and linearity of the DAC in the feedback circuit. Accurately designing the DAC is the focus and key of this design. Traditional SAR ADCs mostly use simple resistor dividers or capacitor charges. The advantage of the resistor-divider converter is that it only needs to use one kind of resistor, which can easily ensure the manufacturing accuracy. Even if there is a large error in the resistor, non-monotonicity will not occur. However, an n-bit binary input resistor-dividing digital-to-analog converter requires 2n voltage-dividing resistors and the same number of analog switches. Therefore, as the number of bits increases, the number of required components will increase geometrically. This It is its shortcoming. It is relatively rare to use this structure alone to make a DAC, but it is commonly used in SAR ADCs below 8 bits. The advantage of capacitive charge type DAC is that it has higher accuracy, but the disadvantage is that it has a large area. It is sensitive to parasitic capacitance and needs to be connected to the clock, which increases the complexity of design and manufacturing.

The DAC designed in this article adopts a composite structure. Since this chip is a 12-bit precision ADC, the DAC is required to also reach 12-bit precision. Moreover, for converters with higher digits, considering the chip area and performance, the combined structure is relatively small. The advantages of a single structure are significant, so this article adopts a 5+3+4 composite structure, that is, the upper 5-bit MSB is implemented with a capacitor network, the middle 3 bits are implemented with an electronic network, and the lower 4-bit LSB is still implemented with a capacitor network. This design avoids differences. The shortcomings in structural implementation are combined with their respective advantages to better achieve the circuit design goals. The advantage of this DAC is that it has a certain monotonicity. Because the resistor string is essentially monotonic, and the three digital bits have only one resistance value, there is no resistance mismatch problem. The resistor string does not need to be precharged, and the conversion speed is faster than that of the capacitor array, but the chip occupies an area Larger, the capacitor network only needs to meet the capacitance accuracy requirements corresponding to 5 digits at most to achieve 12-bit conversion matching. Therefore, when allocating the number of bits per segment, this article makes a compromise between chip area and conversion speed. The DAC is simulated and its settling time is only 12ns.

Design Simulation

According to the circuit function and index requirements, Hspice is used to simulate the circuit in the Cadence environment, and the control logic is accurately controlled, and finally the 12-bit digital conversion result is achieved. Figure 2 shows the output waveform of selecting the 8th channel to convert the 2.5V voltage. The correct conversion of analog signals to digital signals is achieved. The operating temperature range of the 12-bit ADC is -55℃-125℃. The access conditions are VDD=5.0V, VSS=0V, VREF=4.096V, VAGND=0V, and finally based on CSMC The 0.6μm BiCMOS process has completed the layout design, with an area of 2.5×2.2mm2.

|

Conclusion

This article designed and implemented a 12-bit serial output ADC based on CSMC 0.6μm BiCMOS process. It adopts voltage scaling and charge scaling combined digital-to-analog converter technology. The comparator is implemented in the form of a multi-pole cascade amplifier. Through reasonable Timing control achieves better performance, the conversion rate is 7.5μs, the normal operating current is 2.8mA, the gain error is less than 2LSB, the linear error is less than 1LSB, and the final layout area is 2.5×2.2mm2. This converter is suitable for consumer electronics, It is a cost-effective choice for applications in automotive electronics and portable products.

Previous article:TNY256 single chip switching power supply and its application

Next article:High-precision DC voltage/current source design based on dual 12-bit DAC

- Popular Resources

- Popular amplifiers

-

Dual Radar: A Dual 4D Radar Multimodal Dataset for Autonomous Driving

Dual Radar: A Dual 4D Radar Multimodal Dataset for Autonomous Driving -

Multi-port and shared memory architecture for high-performance ADAS SoCs

Multi-port and shared memory architecture for high-performance ADAS SoCs -

Semantic Segmentation for Autonomous Driving: Model Evaluation, Dataset Generation, Viewpoint Comparison, and Real-time Performance

Semantic Segmentation for Autonomous Driving: Model Evaluation, Dataset Generation, Viewpoint Comparison, and Real-time Performance -

Basics of Machine Learning: From Getting Started to Job Hunting (Hu Huanwu)

Basics of Machine Learning: From Getting Started to Job Hunting (Hu Huanwu)

- MathWorks and NXP Collaborate to Launch Model-Based Design Toolbox for Battery Management Systems

- STMicroelectronics' advanced galvanically isolated gate driver STGAP3S provides flexible protection for IGBTs and SiC MOSFETs

- New diaphragm-free solid-state lithium battery technology is launched: the distance between the positive and negative electrodes is less than 0.000001 meters

- [“Source” Observe the Autumn Series] Application and testing of the next generation of semiconductor gallium oxide device photodetectors

- 采用自主设计封装,绝缘电阻显著提高!ROHM开发出更高电压xEV系统的SiC肖特基势垒二极管

- Will GaN replace SiC? PI's disruptive 1700V InnoMux2 is here to demonstrate

- From Isolation to the Third and a Half Generation: Understanding Naxinwei's Gate Driver IC in One Article

- The appeal of 48 V technology: importance, benefits and key factors in system-level applications

- Important breakthrough in recycling of used lithium-ion batteries

- Innolux's intelligent steer-by-wire solution makes cars smarter and safer

- 8051 MCU - Parity Check

- How to efficiently balance the sensitivity of tactile sensing interfaces

- What should I do if the servo motor shakes? What causes the servo motor to shake quickly?

- 【Brushless Motor】Analysis of three-phase BLDC motor and sharing of two popular development boards

- Midea Industrial Technology's subsidiaries Clou Electronics and Hekang New Energy jointly appeared at the Munich Battery Energy Storage Exhibition and Solar Energy Exhibition

- Guoxin Sichen | Application of ferroelectric memory PB85RS2MC in power battery management, with a capacity of 2M

- Analysis of common faults of frequency converter

- In a head-on competition with Qualcomm, what kind of cockpit products has Intel come up with?

- Dalian Rongke's all-vanadium liquid flow battery energy storage equipment industrialization project has entered the sprint stage before production

- Allegro MicroSystems Introduces Advanced Magnetic and Inductive Position Sensing Solutions at Electronica 2024

- Car key in the left hand, liveness detection radar in the right hand, UWB is imperative for cars!

- After a decade of rapid development, domestic CIS has entered the market

- Aegis Dagger Battery + Thor EM-i Super Hybrid, Geely New Energy has thrown out two "king bombs"

- A brief discussion on functional safety - fault, error, and failure

- In the smart car 2.0 cycle, these core industry chains are facing major opportunities!

- The United States and Japan are developing new batteries. CATL faces challenges? How should China's new energy battery industry respond?

- Murata launches high-precision 6-axis inertial sensor for automobiles

- Ford patents pre-charge alarm to help save costs and respond to emergencies

- New real-time microcontroller system from Texas Instruments enables smarter processing in automotive and industrial applications

- After connecting to UPS, some devices do not work

- 22 "Wanli" Raspberry Pi car - mobile phone remote control motor rotation

- [Raspberry Pi 4B Review] Install Libreelec system on Raspberry Pi 4 and install plug-ins to watch IPTV live broadcast

- Industrial Sensor Selection Method

- The same via can have different impedances???

- What simulation software is generally used when making switching power supplies?

- Design of 16-channel data acquisition system based on ADC0809 and 51 single-chip microcomputer

- usb device management

- EEWORLD University Hall----The working principle of high voltage isolation technology

- Today's new product sharing: Design of personalized car LED driver; single-cell lithium battery 3.7V mono audio amplifier IC solution

Dual Radar: A Dual 4D Radar Multimodal Dataset for Autonomous Driving

Dual Radar: A Dual 4D Radar Multimodal Dataset for Autonomous Driving

京公网安备 11010802033920号

京公网安备 11010802033920号