1. Introduction to DDS

The DDS signal generator uses direct digital synthesis (DDS) technology to improve the frequency stability and accuracy of the signal generator to the same level as the reference frequency, and can perform fine frequency adjustment in a wide frequency range. The signal source designed using this method can work in a modulation state, adjust the output level, and output various waveforms.

2. Principle

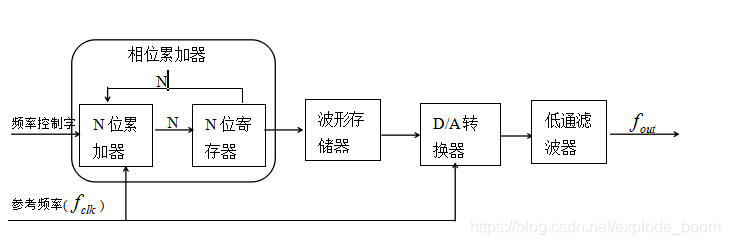

The theoretical basis of DDS signal generation is the "Nyquist sampling theorem". The theorem shows that when the sampling frequency is greater than or equal to twice the highest frequency of the analog signal, the original analog signal can be recovered from the discrete sequence distortion-free signal. The principle of DDS signal generation is to sample the analog signal. When a sampling process has occurred and the sampled value has been quantized, the original analog signal is reconstructed from the quantized value. The basic DDS structure is mainly composed of a phase accumulator, a waveform quantization data storage, and a D/A converter. Among them, the phase accumulator and the waveform quantization data storage are called digitally controlled oscillators, which are the digital parts of the DDS structure. The basic structure principle of DDS is shown in the figure below.

In the figure, the phase accumulator is composed of an N-bit adder and an N-bit accumulation register, which is an extremely important part of the DDS module. Driven by the reference frequency clock, the DDS module starts to work; when each reference clock comes, the accumulator accumulates the frequency control word FW and the value output by the register, and inputs the result of the addition into the register, and the accumulation register transmits the data generated when the previous reference clock acts to the accumulator by feedback. In this way, under the action of the clock, the frequency control word can be accumulated continuously. At this time, the data output by the phase accumulator is used as the address to search the amplitude table corresponding to the address in the waveform memory to complete the conversion from phase to amplitude. In the DDS module, the formula for the output frequency is:

It can be seen from the above formula that when the reference signal and the number of bits of the accumulator are given, the final output frequency of the signal is mainly determined by the frequency control word. Therefore, when the frequency control word changes, the output frequency also changes, thereby realizing the basic function of frequency modulation.

3. DDS code

module DDS(

input clk,

input rst_n,

input [31:0]fword,

input [10:0]pword,

output [11:0]DA

);

reg [31:0] r_fword;

reg [11:0] r_pword;

reg [31:0] cnt;

wire [11:0] rom_addr;

always@(posedge clk or negedge rst_n)begin

if(!rst_n) begin

r_fword <= 0;

r_pword <= 0;

end

else begin

r_fword <= fword;

r_pword <= pword;

end

end

always@(posedge clk or negedge rst_n)

if(!rst_n)

cnt <= 32'd0;

else

cnt <= cnt +r_fword;

assign rom_addr = cnt[31:20] + r_pword;

blk_mem_gen_0 blk_mem_gen_1 (

.clka(clk), // input wire clka

.addra(rom_addr), // input wire [11 : 0] addra

.douta(DA) // output wire [11 : 0] douta

);

endmodule

The blk_mem_gen_0 instantiation module is the "rom" IP core called in vivado, and the settings are shown in the following two figures.

The initialization coe file of ROM can be generated by waveform data generator or MATLAB, saved in the project directory, and the initialization file is selected as the generated coe file in ROM.

4. Test Files

`timescale 1ns/1ns

module DDS_tb;

reg clk;

reg rst_n;

reg [31:0] fword;

reg [10:0] pword;

wire [11:0] YES;

DDS DDS0 (

.clk (clk),

.rst_n (rst_n),

.fword (fword),

.pword (pword),

.YES YES)

);

initial clk = 1;

always #5 clk = ~clk;

initial begin

rst_n = 0;

fword = 42955;

pword = 256;

#201;

rst_n = 1;

end

endmodule

5. Simulation Results

In Vivado, click Run Simulation-Run Behavioral Simulation, select DA, and set it to simulate the signal, as shown in the figure below.

Click on the top to run

In the test file, the input clock is set to 100M, the frequency control word is 42955, and the phase control word is 256. The frequency calculated by the above output frequency calculation formula is =42955x100000000/2^32=1000.12Hz, and the period is 1ms. The waveform is measured and the period is about 1ms, as shown in the figure below.

6. Conclusion

The simulation results are consistent with the expected effect, proving that the module is correct. Interested readers can add the DAC module and low-pass filter module to the above part to get a DDS signal generator.

Previous article:Square wave sine wave (amplitude shift keying generator ASK) circuit design

Next article:DDS signal generator based on AD9833

- New IsoVu™ Isolated Current Probes: Bringing a New Dimension to Current Measurements

- Modern manufacturing strategies drive continuous improvement in ICT online testing

- Methods for Correlation of Contact and Non-Contact Measurements

- Keysight Technologies Helps Samsung Electronics Successfully Validate FiRa® 2.0 Safe Distance Measurement Test Case

- From probes to power supplies, Tektronix is leading the way in comprehensive innovation in power electronics testing

- Seizing the Opportunities in the Chinese Application Market: NI's Challenges and Answers

- Tektronix Launches Breakthrough Power Measurement Tools to Accelerate Innovation as Global Electrification Accelerates

- Not all oscilloscopes are created equal: Why ADCs and low noise floor matter

- Enable TekHSI high-speed interface function to accelerate the remote transmission of waveform data

- Intel promotes AI with multi-dimensional efforts in technology, application, and ecology

- ChinaJoy Qualcomm Snapdragon Theme Pavilion takes you to experience the new changes in digital entertainment in the 5G era

- Infineon's latest generation IGBT technology platform enables precise control of speed and position

- Two test methods for LED lighting life

- Don't Let Lightning Induced Surges Scare You

- Application of brushless motor controller ML4425/4426

- Easy identification of LED power supply quality

- World's first integrated photovoltaic solar system completed in Israel

- Sliding window mean filter for avr microcontroller AD conversion

- What does call mean in the detailed explanation of ABB robot programming instructions?

- STMicroelectronics discloses its 2027-2028 financial model and path to achieve its 2030 goals

- 2024 China Automotive Charging and Battery Swapping Ecosystem Conference held in Taiyuan

- State-owned enterprises team up to invest in solid-state battery giant

- The evolution of electronic and electrical architecture is accelerating

- The first! National Automotive Chip Quality Inspection Center established

- BYD releases self-developed automotive chip using 4nm process, with a running score of up to 1.15 million

- GEODNET launches GEO-PULSE, a car GPS navigation device

- Should Chinese car companies develop their own high-computing chips?

- Infineon and Siemens combine embedded automotive software platform with microcontrollers to provide the necessary functions for next-generation SDVs

- Continental launches invisible biometric sensor display to monitor passengers' vital signs

- Mobile TV 2006 attracts global mobile TV elites

- Master the core technology, do you know the domestic programming language Mulan?

- CPU Power Controllers: Performance Comparison of Single-Edge and Dual-Edge Architectures

- PKE System Design Using the PIC16F639

- Keil C51 MCU Programming Software and Instructions Learning Tutorial (Full Version)

- I also play around with logic analyzers occasionally. I work on hardware. What should I do after capturing these waveform data? Compare the logarithms...

- Disassembled a forehead thermometer

- Program Name: Practical Analog Circuit Design Technology-Section 1

- High-performance control technology for asynchronous motors without speed sensors

- Development Trends and Prospects of 3D Packaging

CMOS analog integrated circuit design and simulation examples

CMOS analog integrated circuit design and simulation examples Hspice Tutorial [Tsinghua University]

Hspice Tutorial [Tsinghua University]

京公网安备 11010802033920号

京公网安备 11010802033920号