In the field of measurement and instrumentation, it is often necessary to measure the pulse width of digital signals. This measurement usually uses the pulse counting method, that is, a high-frequency clock pulse is used to count the high or low level of the signal to be measured, and then the width of the signal to be measured is calculated based on the number of pulses, as shown in Figure 1. The signal to be measured is usually independent of the counting clock, and its rising and falling edges cannot fall exactly on the edge of the clock. Therefore, the maximum measurement error of this method is one clock cycle. For example, using a high-frequency clock of 80MHz, the maximum error is 12.5ns.

There are usually two ways to improve the accuracy of pulse counting method: increase the counting clock frequency and use time-amplitude conversion technology. The higher the clock frequency, the smaller the measurement error, but the higher the frequency, the higher the performance requirements of the chip. For example, when a measurement error of 1ns is required, the clock frequency needs to be increased to 1GHz. At this time, it is difficult for a general counter chip to work normally, and it will also bring many problems such as circuit board wiring, material selection, and processing. Although the time-amplitude conversion technology does not require the clock frequency, it is easily interfered by noise when the frequency of the signal to be measured is relatively high due to the use of analog circuits. Moreover, when the pulse width of the signal is required to be measured continuously, there are certain problems in the rapidity of the circuit response.

Different from the above two methods, this paper proposes another idea of using digital phase shifting technology to improve the accuracy of pulse width measurement and uses FPGA chips to implement the test system.

1 Measurement principle The

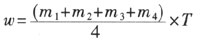

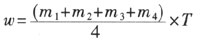

so-called phase shift refers to the fact that for two signals of the same frequency, one of them is used as the reference signal, and the other is moved ahead or behind the reference signal to form a phase difference. Digital phase shift usually uses a delay method, and the length of the delay determines the phase difference between the two digital signals. The measurement principle proposed in this paper is based on digital phase shifting technology. As shown in Figure 2, the original counting clock signal CLK0 is phase-shifted to obtain CLK90, CLK180, and CLK270, with a phase difference of 90°. These four clock signals are used to simultaneously drive four identical counters to count the signals to be measured. Assuming the clock frequency is f, the period is T, and the count numbers of the four counters are m1, m2, m3, and m4 respectively, the final pulse width measurement value is:

It can be seen that this method is actually equivalent to quadrupling the original counting clock and counting the signal to be measured at a clock frequency of 4f, thereby increasing the measurement accuracy to four times the original. For example, when the original counting clock is 80MHz, the equivalent counting frequency of the system is 320MHz. If the relative delay time error between the counting clocks is not considered, the maximum measurement error will be reduced to one-fourth of the original, only 3.125ns. At the same time, this method ensures that the maximum operating frequency of the entire circuit is still human and avoids a series of problems caused by the increase in clock frequency.

2 System Implementation

The most critical part of the system implementation is to ensure the relative delay accuracy of the clocks sent to each counter, that is, to ensure the phase difference between the counting clocks. Since the original clock frequency is usually relatively high (usually close to 100MHz) and the period is between 10 and 20ns, the delay time of the clock is only a few ns, and the use of ordinary delay line chips cannot meet the accuracy requirements; at the same time, in order to avoid the influence of the transmission delay between chips in the circuit board, the accuracy, stability and flexibility of the test system are guaranteed. This paper uses a field programmable gate array (FPGA) to implement the proposed measurement method. The system structure is shown in Figure 3. The crystal oscillator generates the original input clock, and the measured value of the pulse width is obtained after passing through the phase shift counting module. The measurement result is sent to the FIFO buffer to speed up the data processing speed, and finally the data transmission with the computer is completed through the PCI bus. Logic control is used to coordinate the timing between modules to ensure the normal operation of the system. In order to improve the flexibility and convenience of the test system, the system has established internal registers. By modifying the value of the register by software, the start and stop of the test system can be controlled, and the measurement of high level or low level can be selected. The phase shift counting module, FIFO buffer and logic control are all implemented in the FPGA chip, and the chip uses the SpartanII series of XILINX.

The SpartanII series is a high-performance, low-cost FPGA chip with a maximum operating frequency of 200MHz. Here, the XC2S15-6 (-6 is the speed grade) is selected. The chip provides four high-precision on-chip digital delay-locked loops (DLLs), which can ensure zero transmission delay and low clock skew of the clock signal in the chip

; at the same time, it can easily implement common control of the clock signal, such as phase shifting, frequency multiplication, and frequency division. In HDL programming, the symbol CLKDLL can be used to call the on-chip DLL structure, and its pin diagram is shown in Figure 4. The main pin descriptions are as follows:

CLKIN: Clock source input, with a frequency range of 25 to 100MHz.

CLKFB: Feedback or reference clock signal, which can only be fed back from CLK0 or CLK2X.

CLK[0︱90︱180︱270]: Clock output, with the same frequency as the input clock, but with a phase difference of 90°. It defines the attribute DUTY_CY-CLE_CORRECTION, which can be used to adjust the duty cycle of the clock. When the value is FALSE, the duty cycle of the output clock is consistent with the input clock. When the value is TRUE, the duty cycle is adjusted to 50%.

CLK2X: Clock source multiplied output, and the duty cycle is automatically adjusted to 50%.

CLKDV: Clock source divided output, the N division is controlled by the attribute CLKDV_DIVIDE, and N can be 1.5, 2, 2.5, 3, 4, 5, 8 or 16.

LOCKED: When the signal is low, it means that the delay phase-locked loop DLL has not locked the signal, and the above output clock signal has not reached the ideal signal; when it becomes high, it means that the phase-locked loop has completed the signal lock and the output clock signal is available. If the clock source input frequency is greater than 60MHz, the system lock time is about 20μs. [page]

The DLL function can be used to quickly and conveniently build a phase-shift counting module to implement the measurement method introduced in this article. The structure of the phase-shift counting module is shown in Figure 5. The four clock outputs with a phase difference of 90° obtained after the original clock is processed by CLKDLL are CLK0, CLK90, CLKl80 and CLK270, which are used as the counting clocks of four identical 16-bit counters respectively. The signal to be measured is connected to the enable end of the counter, and the start and stop of the four counters are controlled at the same time. With the counting results of each counter, the accumulated count number is obtained through the adder, and finally the signal pulse width value is calculated.

3 Simulation and accuracy analysis

Figure 6 shows the simulation results of Modelsim after the internal wiring of the FPGA chip. After RESET, the phase shift counting module is started to measure the signal to be measured. After completing a measurement, a READY signal is generated and the measurement results are output for subsequent use. The simulation results prove that the test system achieves the design goals.

The following is a further in-depth error analysis of the system. The sources of the system measurement pulse width error are mainly the system principle error TS, the clock phase shift error TP, the signal delay error Td and the counting clock jitter TC, as shown in Figure 7.

As mentioned above, when the 80MHz crystal clock is input, the system principle error Ts = 3.125ns. The clock phase shift error is the phase offset between the four clock signals from the CLKDLL. According to the parameters provided by the chip, its maximum TP is 200ps. The counting clock jitter refers to the deviation of the clock signal cycle itself output from the CLKDLL, and its maximum TC is 60ps. Since the number of counted clock cycles is large, its influence on the measurement error of the entire system after averaging can be ignored.

The signal delay error is the synchronization error of the four counter counts caused by the inconsistent transmission delay of each signal inside the chip. In order to analyze the error, the Timing Analyzer program provided by ISE 5.1 is used to further analyze the critical path. The results are shown in Table 1.

The first column in the table is the delay time from the count clock from CLKDLL to each counter, and the second column is the time from the HF signal used to control the start and stop of the counter to the four counters. Since the relative delay time between the count clocks is required, the third column gives the delay of the clock relative to the HF signal to the counter, which is the difference between the first and second columns. From this, the signal delay error Td=0.950ns is obtained.

Therefore, the system measurement error T is:

T=TS+TP+Td=4.275ns (2)

That is, the maximum error of pulse width measurement is ±4.275ns. Compared with the pulse counting method, the maximum measurement error is reduced to 34.2% of the original for the same 80MHz clock input.

This paper designs a high-precision pulse width measurement system based on digital phase shifting technology, which improves the measurement accuracy by several times compared with the pulse counting method. If the measurement accuracy of this method needs to be further improved, it can be improved in the following two aspects: (1) Continue to increase the crystal oscillator frequency and seek faster FPGA chips. The higher the crystal oscillator frequency, the smaller the system principle error. (2) Reduce the signal delay error. As can be seen above, the delay error of the signal has a large impact on the accuracy of the system. Reducing the difference in the signal delay from each counting clock and the signal to be measured to the counter can effectively improve the measurement accuracy. Since the delay time of the internal signal of the FPGA can be easily obtained, the delay error can be minimized by adjusting the placement and connection of each internal component during design, or by adding some gate circuits to increase the delay so that the delay time of each signal is as similar as possible.

Reference address:High-precision pulse width measurement system based on digital phase shifting

|

|

There are usually two ways to improve the accuracy of pulse counting method: increase the counting clock frequency and use time-amplitude conversion technology. The higher the clock frequency, the smaller the measurement error, but the higher the frequency, the higher the performance requirements of the chip. For example, when a measurement error of 1ns is required, the clock frequency needs to be increased to 1GHz. At this time, it is difficult for a general counter chip to work normally, and it will also bring many problems such as circuit board wiring, material selection, and processing. Although the time-amplitude conversion technology does not require the clock frequency, it is easily interfered by noise when the frequency of the signal to be measured is relatively high due to the use of analog circuits. Moreover, when the pulse width of the signal is required to be measured continuously, there are certain problems in the rapidity of the circuit response.

Different from the above two methods, this paper proposes another idea of using digital phase shifting technology to improve the accuracy of pulse width measurement and uses FPGA chips to implement the test system.

1 Measurement principle The

so-called phase shift refers to the fact that for two signals of the same frequency, one of them is used as the reference signal, and the other is moved ahead or behind the reference signal to form a phase difference. Digital phase shift usually uses a delay method, and the length of the delay determines the phase difference between the two digital signals. The measurement principle proposed in this paper is based on digital phase shifting technology. As shown in Figure 2, the original counting clock signal CLK0 is phase-shifted to obtain CLK90, CLK180, and CLK270, with a phase difference of 90°. These four clock signals are used to simultaneously drive four identical counters to count the signals to be measured. Assuming the clock frequency is f, the period is T, and the count numbers of the four counters are m1, m2, m3, and m4 respectively, the final pulse width measurement value is:

|

|

It can be seen that this method is actually equivalent to quadrupling the original counting clock and counting the signal to be measured at a clock frequency of 4f, thereby increasing the measurement accuracy to four times the original. For example, when the original counting clock is 80MHz, the equivalent counting frequency of the system is 320MHz. If the relative delay time error between the counting clocks is not considered, the maximum measurement error will be reduced to one-fourth of the original, only 3.125ns. At the same time, this method ensures that the maximum operating frequency of the entire circuit is still human and avoids a series of problems caused by the increase in clock frequency.

2 System Implementation

The most critical part of the system implementation is to ensure the relative delay accuracy of the clocks sent to each counter, that is, to ensure the phase difference between the counting clocks. Since the original clock frequency is usually relatively high (usually close to 100MHz) and the period is between 10 and 20ns, the delay time of the clock is only a few ns, and the use of ordinary delay line chips cannot meet the accuracy requirements; at the same time, in order to avoid the influence of the transmission delay between chips in the circuit board, the accuracy, stability and flexibility of the test system are guaranteed. This paper uses a field programmable gate array (FPGA) to implement the proposed measurement method. The system structure is shown in Figure 3. The crystal oscillator generates the original input clock, and the measured value of the pulse width is obtained after passing through the phase shift counting module. The measurement result is sent to the FIFO buffer to speed up the data processing speed, and finally the data transmission with the computer is completed through the PCI bus. Logic control is used to coordinate the timing between modules to ensure the normal operation of the system. In order to improve the flexibility and convenience of the test system, the system has established internal registers. By modifying the value of the register by software, the start and stop of the test system can be controlled, and the measurement of high level or low level can be selected. The phase shift counting module, FIFO buffer and logic control are all implemented in the FPGA chip, and the chip uses the SpartanII series of XILINX.

|

|

The SpartanII series is a high-performance, low-cost FPGA chip with a maximum operating frequency of 200MHz. Here, the XC2S15-6 (-6 is the speed grade) is selected. The chip provides four high-precision on-chip digital delay-locked loops (DLLs), which can ensure zero transmission delay and low clock skew of the clock signal in the chip

; at the same time, it can easily implement common control of the clock signal, such as phase shifting, frequency multiplication, and frequency division. In HDL programming, the symbol CLKDLL can be used to call the on-chip DLL structure, and its pin diagram is shown in Figure 4. The main pin descriptions are as follows:

|

|

CLKIN: Clock source input, with a frequency range of 25 to 100MHz.

CLKFB: Feedback or reference clock signal, which can only be fed back from CLK0 or CLK2X.

CLK[0︱90︱180︱270]: Clock output, with the same frequency as the input clock, but with a phase difference of 90°. It defines the attribute DUTY_CY-CLE_CORRECTION, which can be used to adjust the duty cycle of the clock. When the value is FALSE, the duty cycle of the output clock is consistent with the input clock. When the value is TRUE, the duty cycle is adjusted to 50%.

CLK2X: Clock source multiplied output, and the duty cycle is automatically adjusted to 50%.

CLKDV: Clock source divided output, the N division is controlled by the attribute CLKDV_DIVIDE, and N can be 1.5, 2, 2.5, 3, 4, 5, 8 or 16.

LOCKED: When the signal is low, it means that the delay phase-locked loop DLL has not locked the signal, and the above output clock signal has not reached the ideal signal; when it becomes high, it means that the phase-locked loop has completed the signal lock and the output clock signal is available. If the clock source input frequency is greater than 60MHz, the system lock time is about 20μs. [page]

The DLL function can be used to quickly and conveniently build a phase-shift counting module to implement the measurement method introduced in this article. The structure of the phase-shift counting module is shown in Figure 5. The four clock outputs with a phase difference of 90° obtained after the original clock is processed by CLKDLL are CLK0, CLK90, CLKl80 and CLK270, which are used as the counting clocks of four identical 16-bit counters respectively. The signal to be measured is connected to the enable end of the counter, and the start and stop of the four counters are controlled at the same time. With the counting results of each counter, the accumulated count number is obtained through the adder, and finally the signal pulse width value is calculated.

|

|

3 Simulation and accuracy analysis

Figure 6 shows the simulation results of Modelsim after the internal wiring of the FPGA chip. After RESET, the phase shift counting module is started to measure the signal to be measured. After completing a measurement, a READY signal is generated and the measurement results are output for subsequent use. The simulation results prove that the test system achieves the design goals.

|

|

The following is a further in-depth error analysis of the system. The sources of the system measurement pulse width error are mainly the system principle error TS, the clock phase shift error TP, the signal delay error Td and the counting clock jitter TC, as shown in Figure 7.

|

|

As mentioned above, when the 80MHz crystal clock is input, the system principle error Ts = 3.125ns. The clock phase shift error is the phase offset between the four clock signals from the CLKDLL. According to the parameters provided by the chip, its maximum TP is 200ps. The counting clock jitter refers to the deviation of the clock signal cycle itself output from the CLKDLL, and its maximum TC is 60ps. Since the number of counted clock cycles is large, its influence on the measurement error of the entire system after averaging can be ignored.

The signal delay error is the synchronization error of the four counter counts caused by the inconsistent transmission delay of each signal inside the chip. In order to analyze the error, the Timing Analyzer program provided by ISE 5.1 is used to further analyze the critical path. The results are shown in Table 1.

|

|

The first column in the table is the delay time from the count clock from CLKDLL to each counter, and the second column is the time from the HF signal used to control the start and stop of the counter to the four counters. Since the relative delay time between the count clocks is required, the third column gives the delay of the clock relative to the HF signal to the counter, which is the difference between the first and second columns. From this, the signal delay error Td=0.950ns is obtained.

Therefore, the system measurement error T is:

T=TS+TP+Td=4.275ns (2)

That is, the maximum error of pulse width measurement is ±4.275ns. Compared with the pulse counting method, the maximum measurement error is reduced to 34.2% of the original for the same 80MHz clock input.

This paper designs a high-precision pulse width measurement system based on digital phase shifting technology, which improves the measurement accuracy by several times compared with the pulse counting method. If the measurement accuracy of this method needs to be further improved, it can be improved in the following two aspects: (1) Continue to increase the crystal oscillator frequency and seek faster FPGA chips. The higher the crystal oscillator frequency, the smaller the system principle error. (2) Reduce the signal delay error. As can be seen above, the delay error of the signal has a large impact on the accuracy of the system. Reducing the difference in the signal delay from each counting clock and the signal to be measured to the counter can effectively improve the measurement accuracy. Since the delay time of the internal signal of the FPGA can be easily obtained, the delay error can be minimized by adjusting the placement and connection of each internal component during design, or by adding some gate circuits to increase the delay so that the delay time of each signal is as similar as possible.

Previous article:Frequency Calculator Tool Simplifies Mixed-Signal Test Setup

Next article:Real-time and non-real-time integrated applications in the measurement of multiple signals

- Popular Resources

- Popular amplifiers

Recommended Content

Latest Test Measurement Articles

- Seizing the Opportunities in the Chinese Application Market: NI's Challenges and Answers

- Tektronix Launches Breakthrough Power Measurement Tools to Accelerate Innovation as Global Electrification Accelerates

- Not all oscilloscopes are created equal: Why ADCs and low noise floor matter

- Enable TekHSI high-speed interface function to accelerate the remote transmission of waveform data

- How to measure the quality of soft start thyristor

- How to use a multimeter to judge whether a soft starter is good or bad

- What are the advantages and disadvantages of non-contact temperature sensors?

- In what situations are non-contact temperature sensors widely used?

- How non-contact temperature sensors measure internal temperature

MoreSelected Circuit Diagrams

MorePopular Articles

- LED chemical incompatibility test to see which chemicals LEDs can be used with

- Application of ARM9 hardware coprocessor on WinCE embedded motherboard

- What are the key points for selecting rotor flowmeter?

- LM317 high power charger circuit

- A brief analysis of Embest's application and development of embedded medical devices

- Single-phase RC protection circuit

- stm32 PVD programmable voltage monitor

- Introduction and measurement of edge trigger and level trigger of 51 single chip microcomputer

- Improved design of Linux system software shell protection technology

- What to do if the ABB robot protection device stops

MoreDaily News

- CGD and Qorvo to jointly revolutionize motor control solutions

- CGD and Qorvo to jointly revolutionize motor control solutions

- Keysight Technologies FieldFox handheld analyzer with VDI spread spectrum module to achieve millimeter wave analysis function

- Infineon's PASCO2V15 XENSIV PAS CO2 5V Sensor Now Available at Mouser for Accurate CO2 Level Measurement

- Advanced gameplay, Harting takes your PCB board connection to a new level!

- Advanced gameplay, Harting takes your PCB board connection to a new level!

- A new chapter in Great Wall Motors R&D: solid-state battery technology leads the future

- Naxin Micro provides full-scenario GaN driver IC solutions

- Interpreting Huawei’s new solid-state battery patent, will it challenge CATL in 2030?

- Are pure electric/plug-in hybrid vehicles going crazy? A Chinese company has launched the world's first -40℃ dischargeable hybrid battery that is not afraid of cold

Guess you like

- Design of Intelligent Motor Protector Based on DSP

- Happy Teacher's Day! Let's talk about the teacher you remember most when you were in school!

- Definition of waveform overshoot on sampling resistor in constant current source application

- How to generate such waveform using Verilog?

- Environmental Monitoring System

- Are only foreign companies exempt from overtime work?

- 【micropython】Improved reset to bootloader

- 06 Make GD32L233C expansion board

- The names, wavelengths, characteristics and application fields of each band in the electromagnetic spectrum

- [TI Course] How is the anti-interference ability of TI millimeter-wave radar?

715HC

715HC

京公网安备 11010802033920号

京公网安备 11010802033920号