0 Introduction

Among the various parameters of a digital receiver, frequency is one of the most important parameters, which can reflect the function and purpose of the receiver, as well as important indicators such as spectrum width. Traditional sequential frequency measurement technology generally performs continuous sampling of the frequency domain by scanning the receiver frequency band. This method is simple in principle and mature in technology, but the contradiction between its frequency intercept probability and resolution is difficult to resolve, and full-probability signal interception cannot be achieved. Multi-channel frequency detection technology belongs to instantaneous frequency measurement, and its architecture uses multiple frequency windows (multiple channels are connected and adjacent to each other) to cover the entire frequency band of the receiver. In this way, when the signal enters any window, the frequency value of the window can be detected. Therefore, this method can resolve the contradiction between frequency intercept probability and frequency resolution, and also provides a reference solution for achieving full-probability frequency capture.

1 Multi-channel model

When a real signal is sampled by A/D and then subjected to orthogonal down-conversion, two phase-orthogonal signals, I and Q, can be obtained, which constitute a complex signal. The schematic diagram of the channelization of the complex signal is shown in Figure 1.

The channels shown in Figure 1 are overlapping channels that cover the frequency range of the entire zero intermediate frequency signal. In general, multi-channels are often implemented using digital filter banks, but this method requires the design of M (M is the number of channels) bandpass filters with different center frequencies but completely identical other properties. This structural design is too complicated and also increases the speed of subsequent signal processing, which is extremely unfavorable for real-time processing. The low-pass implementation method of the digital filter bank is to first multiply each channel by a transformation factor, which is equivalent to moving the actual signal to zero intermediate frequency, and then obtain the frequency signal through LPF. This method can channelize the frequency band of the bandpass signal, but the new problem it brings is that when the LPF uses FIR filters to implement M filtering operations, it will occupy a large amount of hardware resources and the system efficiency is low. At present, this structure has been replaced by the efficient DFT polyphase filter bank structure.

Figure 2 shows a universal channelized efficient structure based on DFT polyphase filter bank. It can be seen from Figure 2 that before filtering, decimating the data by D times can reduce the amount of calculation in the filtering process. gn(m) is the polyphase component of the low-pass prototype filter hLP(n), and its order can be reduced to 1/D of the original, so DFT can be implemented by FFT. In fact, in this structure, the complexity and data rate of the system are greatly reduced, and the real-time processing capability is improved. [page]

2 Filter Design and Simulation

Each channel in the low-pass filter structure is formed by multiplying the prototype low-pass filter by the rotation factor. According to the requirements, Figure 3 shows the filter group formed by the 256-order prototype low-pass filter and its signal output simulation waveform. The effective bandwidth of the signal is 300MHz, divided into 32 channels, and the bandwidth of each channel is 9.375MHz. If a single-frequency signal with a frequency of ?=28.1MHz is input to this filter group, then, through theoretical calculation, it can be known that the signal should be output in the third channel. Figure 3 (b) shows the output simulation results of the 2nd, 3rd, and 4th channels. It can be seen that only the third channel has a relatively strong signal output, which is consistent with the theoretical calculation results.

3 Implementation plan

The FPGA chip selected in this design is Xilinx's Virtex-4SX55, which has rich clock resources, flexible use of arithmetic units, dedicated storage modules, and configurable logic, and is very suitable for the functional implementation of current signal processing systems. Therefore, according to the structure shown in Figure 2, a channelization solution based on a DFT polyphase filter bank can be obtained, and its specific implementation structure is shown in Figure 4.

The structure shown in Figure 4 consists of a delayer, a coefficient memory, a multiplier and an FFT. The delayer can delay the input data by 32 cycles, and the memory is used to store the filter coefficients. The implementation and simulation results of several main components of the structure are introduced below.

3.1 Implementation of Delay Device

This delayer uses the dedicated access module FIFO provided by FPGA to achieve 32-cycle delay, and its architecture is shown in Figure 5. In the figure, each delay unit is a FIFO module, and the data output characteristic of FIFO is first-in first-out. In this design, the output data of the first-stage delayer will be used as the input data of the next delayer, which is equivalent to the data of the first-stage FIFO being pressed into the second-stage FIFO in the order of first-in first-out. The full flags of the adjacent two stages are handshaked with the read enable signal to achieve delayed data output. In this way, designing 8 FIFOs of the same structure and serially cascading them can meet the design requirements of the structure.

[page]

3.2 Coefficient Storage Module

For a 256-order prototype low-pass filter, the 256 coefficients h(0), h(1), ..., h(255) can be divided into eight groups, each with 32 coefficients, and stored in eight memories. The coefficients stored in memory 0 are: h(0), h(1), ..., h(31); the coefficients stored in memory 1 are: h(32), h(33), ..., h(63); and so on. The memory can be implemented using logic (LUT) or a dedicated storage module Block RAM. When the target data in the FIFO and the coefficients in the memory are multiplied, the corresponding relationship between the two is shown in Figure 6 (taking memory No. 7 as an example).

When the last unit data of the 8 data memories is read out, the coefficients of the address unit 0 of the 8 coefficient memories will also be read out at the same time, and then multiplied and accumulated respectively, and finally output as y(0). Similarly, when the second data of the 8 data memories is read out, the coefficients of the address unit 1 of the 8 coefficient memories will also be read out at the same time, and then multiplied and accumulated respectively, and the final result will be output as y(1), and so on, to obtain the output of all y(2)~y(31). Finally, y(0)~y(31) is used as the input data of FFT to perform 32-point FFT operation.

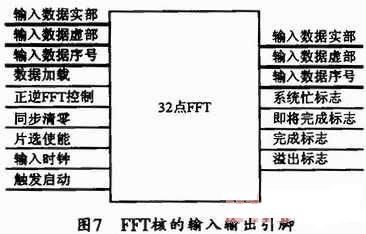

3.3 Implementation of FFT

The FFT transformation in the design can be implemented by calling the Xilinx IP core. FFT uses a pipeline structure that can process continuous data streams, but there is a delay of several cycles on the result. The input and output pin relationship of the FFT core is shown in Figure 7.

3.4 Simulation Results

The FPGA design software can use Active_HDL8.2 from ALDEC, and the designed module can be simulated using the Testbench file. When the Testbench file is read, the signal data generated by Matlab can be used as the excitation signal for FPGA simulation. The signal form uses a 28.1MHz single-frequency signal:

After the signal data is input into the system constructed in FIG. 4 , the simulation waveform shown in FIG. 8 can be obtained under ALDEC.

As can be seen from FIG8 , the simulation result has a signal output on channel 3, which is consistent with the result of Matlab simulation in FIG3 , thereby verifying the correctness of the module design.

4 Conclusion

This paper studies multi-channel frequency detection technology, and on the basis of traditional detection methods, combined with the characteristics of FPGA, constructs an efficient structure based on DFT polyphase filter bank channelization. This structure can solve the contradiction between frequency intercept probability and frequency resolution, and also provides a reference solution for achieving full probability frequency capture. After simulation and test verification, this solution can meet the detection index requirements, thus providing a design reference for multi-channel frequency detection technology.

Previous article:Design and implementation of intelligent cable test system

Next article:Moore's Law in Testing

Recommended ReadingLatest update time:2024-11-17 00:17

- Popular Resources

- Popular amplifiers

-

Analysis and Implementation of MAC Protocol for Wireless Sensor Networks (by Yang Zhijun, Xie Xianjie, and Ding Hongwei)

Analysis and Implementation of MAC Protocol for Wireless Sensor Networks (by Yang Zhijun, Xie Xianjie, and Ding Hongwei) -

MATLAB and FPGA implementation of wireless communication

MATLAB and FPGA implementation of wireless communication -

Intelligent computing systems (Chen Yunji, Li Ling, Li Wei, Guo Qi, Du Zidong)

Intelligent computing systems (Chen Yunji, Li Ling, Li Wei, Guo Qi, Du Zidong) -

Summary of non-synthesizable statements in FPGA

Summary of non-synthesizable statements in FPGA

- Keysight Technologies Helps Samsung Electronics Successfully Validate FiRa® 2.0 Safe Distance Measurement Test Case

- From probes to power supplies, Tektronix is leading the way in comprehensive innovation in power electronics testing

- Seizing the Opportunities in the Chinese Application Market: NI's Challenges and Answers

- Tektronix Launches Breakthrough Power Measurement Tools to Accelerate Innovation as Global Electrification Accelerates

- Not all oscilloscopes are created equal: Why ADCs and low noise floor matter

- Enable TekHSI high-speed interface function to accelerate the remote transmission of waveform data

- How to measure the quality of soft start thyristor

- How to use a multimeter to judge whether a soft starter is good or bad

- What are the advantages and disadvantages of non-contact temperature sensors?

- Innolux's intelligent steer-by-wire solution makes cars smarter and safer

- 8051 MCU - Parity Check

- How to efficiently balance the sensitivity of tactile sensing interfaces

- What should I do if the servo motor shakes? What causes the servo motor to shake quickly?

- 【Brushless Motor】Analysis of three-phase BLDC motor and sharing of two popular development boards

- Midea Industrial Technology's subsidiaries Clou Electronics and Hekang New Energy jointly appeared at the Munich Battery Energy Storage Exhibition and Solar Energy Exhibition

- Guoxin Sichen | Application of ferroelectric memory PB85RS2MC in power battery management, with a capacity of 2M

- Analysis of common faults of frequency converter

- In a head-on competition with Qualcomm, what kind of cockpit products has Intel come up with?

- Dalian Rongke's all-vanadium liquid flow battery energy storage equipment industrialization project has entered the sprint stage before production

- Allegro MicroSystems Introduces Advanced Magnetic and Inductive Position Sensing Solutions at Electronica 2024

- Car key in the left hand, liveness detection radar in the right hand, UWB is imperative for cars!

- After a decade of rapid development, domestic CIS has entered the market

- Aegis Dagger Battery + Thor EM-i Super Hybrid, Geely New Energy has thrown out two "king bombs"

- A brief discussion on functional safety - fault, error, and failure

- In the smart car 2.0 cycle, these core industry chains are facing major opportunities!

- The United States and Japan are developing new batteries. CATL faces challenges? How should China's new energy battery industry respond?

- Murata launches high-precision 6-axis inertial sensor for automobiles

- Ford patents pre-charge alarm to help save costs and respond to emergencies

- New real-time microcontroller system from Texas Instruments enables smarter processing in automotive and industrial applications

- [Sipeed LicheeRV 86 Panel Review] VII. Compiling d1-h_nezha-...

- Counting TI's star products in T-BOX: Automotive Ethernet | Section 1 DP83TC811S-Q1: Automotive Ethernet makes your T-BOX...

- ADAFRUIT PYBADGE LC CAN RUNNING MAKECODE ARCADE, CIRCUITPYTHON AND ARDUINO

- STSPIN32F0 FOC control board drives DJI model aircraft motor/single resistor/schematic diagram/code/debugging instructions and other information are open source

- EEWORLD University Hall----Live Replay: The new Infineon MOSFET based on Source-down technology effectively improves power density, which is visible to the naked eye

- Keil registration machine 2032

- March 19 live broadcast review: Introduction to ST MEMS sensor development kit (including video, presentation documents, Q&A summary)

- Recruiting AE (Application Engineer) Manager - Motor Drive Direction 20-25K/month*14

- Help Arteli grow, tell us your story with Arteli

- How do I use TINA-TI to simulate a circuit that may contain non-TI components?

Analysis and Implementation of MAC Protocol for Wireless Sensor Networks (by Yang Zhijun, Xie Xianjie, and Ding Hongwei)

Analysis and Implementation of MAC Protocol for Wireless Sensor Networks (by Yang Zhijun, Xie Xianjie, and Ding Hongwei)

京公网安备 11010802033920号

京公网安备 11010802033920号