As data rates increase, the need for clock jitter analysis increases. In high-speed serial data links, clock jitter affects data jitter in transmitters, transmission lines, and receivers. Clock quality assurance measurements are also evolving. The emphasis is on establishing a direct correlation between clock performance and system performance in terms of bit error rate. We will review the role of the reference clock and the impact of clock jitter on data jitter, and discuss new measurement techniques used in the Agilent E5001A Precision Clock Jitter Analysis application running on the E5052B Signal Source Analyzer (SSA), which provides outstanding capabilities to measure ultra-low random jitter (RJ) and real-time jitter spectrum analysis of RJ and periodic jitter (PJ) components to improve design quality. We will also discuss the real-time measurement capabilities of this new technology that can accelerate the design verification process.

The Role of Reference Clocks in High-Speed Serial Applications

Figure 1 shows the main components of a reference clock. The transmitter typically serializes a set of low-rate parallel signals into a serial data stream. The transmission channel through which the signals propagate includes backplanes and cables. The receiver interprets the incoming serial data, reconstructs its clock signal, and usually de-serializes it into a parallel data stream. In many descriptions such as this one, the reference clock is considered a component rather than a key player. However, in high-rate serial data systems, the reference clock is used as a key component. Usually the reference clock oscillates at a frequency much lower than the data rate and is then multiplied in the transmitter. The transmitter uses the reference clock to define the timing of logic transitions in the serial data stream. The reference clock is characteristic of the transmitted data. At the receiver, two different situations occur. If the reference clock has not been distributed, the receiver recovers a clock from the data stream, for example, using a phase-locked loop ( PLL ), and uses this clock to locate the sampling point in time. If the reference clock has been distributed, the receiver uses the data signal and the reference clock to locate the sampling point.

Effect of Clock Jitter on Transmitter Data Jitter

The reference clock is the fundamental source of system timing. It provides the time-base of the transmitter. In distributed and non-distributed clock systems, the characteristics of the reference clock are reproduced in the receiver clock recovery circuit. Now, we need to understand how clock jitter propagates in the transmitter of the system.

To define the timing of the logic transitions, the transmitter must multiply the reference clock by an appropriate factor to achieve the data rate. For example, for a 100 MHz reference clock and a 5 Gb/s output signal, the transmitter will use a PLL to increase the reference clock by a factor of 50. The PLL multiplier both amplifies the clock jitter and introduces its own jitter, primarily RJ jitter from the PLL voltage-controlled oscillator ( VCO ). The effect of increasing the frequency by a factor of n is to amplify the phase noise power to carrier ratio by a factor of n2, so jitter increases rapidly.

The PLL multiplier in the transmitter has a finite frequency response, typically on the order of seconds, as shown in Figure 3. The non-uniform frequency response raises an interesting question: What is the effect of clock jitter? If the PLL is good and has zero bandwidth, all clock jitter can be filtered out, providing a jitter-free timebase for the transmitter. Of course, zero bandwidth means infinite lock time, so there is a compromise. But the narrower the PLL bandwidth, the less jitter there is in the reference clock going into the data. To determine if the clock is operating at the desired BER in the system, the jitter spectrum must be carefully measured.

Real World Jitter Sources

There are many sources of jitter in real-world high-speed data circuits, as shown in Figure 4. As mentioned earlier, clock signals are often distributed to multiple ICs, and the clock frequency can be multiplied and/or divided. Assuming that the reference clock from the crystal oscillator has lower jitter, the multiplied or divided output clock will become unclean due to additive noise from the IC or interference from other devices.

A major source of contamination is switching power supply noise with a typical switching frequency of 100 kHz to 1 MHz. This switching power supply noise can enter the clock signal line, which is PJ jitter in the lower left of the figure.

Other sources of periodic jitter components can be interference in the data or clock lines, and inter-modulation products can enter the clock line, which is also considered a component of PJ jitter. As long as the PJ components are far away from the clock frequency, a bandpass filter (or low-pass filter) can be inserted to suppress these jitters. The problem is that when the periodic jitter is close to the clock frequency, high-Q filters are difficult to implement at high frequencies. For RJ jitter of the reference clock, a clock divider circuit will add broadband noise, causing the RJ jitter of the output clock signal to increase.

To diagnose the problem, the clock jitter must be characterized in its actual location in the circuit and/or under operating conditions.

Analyzing the characteristics of clock jitter through phase noise measurement technology

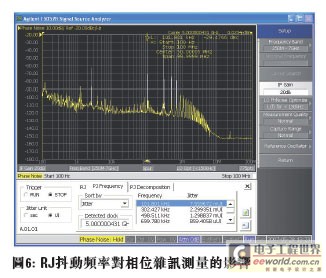

Full analysis of clock signals requires femtosecond (f [fai] second) accuracy, which can only be achieved with phase noise measurement techniques. Phase noise analysis provides two key measurements: S (t), which contain everything from clock phase information to the bandwidth limit of the phase noise measurement. [fai] and RJ jitter analysis with a phase noise analyzer can achieve two important goals. The first is to integrate the RJ power-series characteristics to find the RJ jitter spectrum, that is, to extract the width of the corresponding RJ Gaussian distribution from the desired bandwidth. Second, analyze the main causes of S jitter. (Figure 5) PJ components will be seen as spurs in the phase noise spectrum. Knowledge of the PJ frequency can help diagnose faults. Knowing the PJ rms of each PJ frequency also helps to understand the contribution of each PJ component to the overall clock jitter, so as to examine how much the total jitter will be affected if the main PJ component is removed. (Figure 6)

Real-time jitter measurement with advanced architecture

Unlike conventional jitter measurement examples, the E5052B SSA with E5001A software provides real-time jitter analysis for phase noise measurements. The instrument uses a PLL with reference source. It automatically detects the clock frequency, and the built-in reference source automatically adjusts to the clock frequency within a few milliseconds and measures the noise signal from the phase detector that maintains the PLL. The noise signal captured with a 250 MSa/s

ADC

supports 100 MHz jitter bandwidth measurement, covering the analysis range of OC-192 jitter. Real-time FFT dynamically acquires frequency domain data, increasing the speed of measurement. For example, it only takes 0.3 seconds to measure a bandwidth from 1 kHz to 100 MHz.

Jitter noise benchmark using cross-correlation technology

The E5052B jitter measurements have very low resolution and noise floor, typically femtoseconds of RJ jitter noise floor at 10Gbps. Typical high-performance (real-time or sampling) oscilloscopes have jitter noise floors in excess of hundreds of femtoseconds due to limited dynamic range ADCs and relatively large residual jitter in internal interfering timebases. The E5052B maintains a wide dynamic range by eliminating the phase noise of the fundamental frequency of the larger carrier signal through detection. Even at residual jitter below its internal timebase, the E5052B uses a unique cross-correlation technique between two independent internal measurement channels to extend the jitter measurement limit (Figure 7). Using this cross-correlation technique, the E5052B can achieve jitter noise floors that are 100 to 1,000 times lower than today’s high-performance oscilloscopes (Figure 8).

Simulating PLL response in real time

Figure 9 shows an example of the effect of applying the PLL response function directly to the clock phase noise signal. It can be seen how different parts of the spectrum are suppressed, allowing analysis of application-related jitter. The E5052B's real-time jitter analysis of phase noise measurements accelerates the design process. Any PLL response function can be ported to the E5052B SSA, allowing users to easily and quickly simulate the PLL response from device to device.

Conclusion

For high-speed serial data applications, the main goal of clock jitter analysis is to determine the impact of reference clock jitter on the system bit error rate. The most accurate method is to use the worst-case transmitter (and receiver) transmit function for the application and measure the clock RJ jitter and PJ jitter results. The E5001A Precision Clock Jitter Analysis software running on the E5052B changes the characteristics of traditional jitter measurement products, not only providing comprehensive analysis of clock jitter with femtosecond accuracy, but also providing easy-to-use and real-time jitter analysis capabilities, which will help accelerate the design verification process.

(Author of this article: Akihiko Oginuma, Senior Product Manager, Component Test Division Kobe, Electronic Measurements Group, Agilent Technologies)

Previous article:Solve yield issues with embedded memory test and repair

Next article:A new method for tolerance test of high-speed serial signal receiving end based on digital synthesis technology

- Keysight Technologies Helps Samsung Electronics Successfully Validate FiRa® 2.0 Safe Distance Measurement Test Case

- From probes to power supplies, Tektronix is leading the way in comprehensive innovation in power electronics testing

- Seizing the Opportunities in the Chinese Application Market: NI's Challenges and Answers

- Tektronix Launches Breakthrough Power Measurement Tools to Accelerate Innovation as Global Electrification Accelerates

- Not all oscilloscopes are created equal: Why ADCs and low noise floor matter

- Enable TekHSI high-speed interface function to accelerate the remote transmission of waveform data

- How to measure the quality of soft start thyristor

- How to use a multimeter to judge whether a soft starter is good or bad

- What are the advantages and disadvantages of non-contact temperature sensors?

- Innolux's intelligent steer-by-wire solution makes cars smarter and safer

- 8051 MCU - Parity Check

- How to efficiently balance the sensitivity of tactile sensing interfaces

- What should I do if the servo motor shakes? What causes the servo motor to shake quickly?

- 【Brushless Motor】Analysis of three-phase BLDC motor and sharing of two popular development boards

- Midea Industrial Technology's subsidiaries Clou Electronics and Hekang New Energy jointly appeared at the Munich Battery Energy Storage Exhibition and Solar Energy Exhibition

- Guoxin Sichen | Application of ferroelectric memory PB85RS2MC in power battery management, with a capacity of 2M

- Analysis of common faults of frequency converter

- In a head-on competition with Qualcomm, what kind of cockpit products has Intel come up with?

- Dalian Rongke's all-vanadium liquid flow battery energy storage equipment industrialization project has entered the sprint stage before production

- Allegro MicroSystems Introduces Advanced Magnetic and Inductive Position Sensing Solutions at Electronica 2024

- Car key in the left hand, liveness detection radar in the right hand, UWB is imperative for cars!

- After a decade of rapid development, domestic CIS has entered the market

- Aegis Dagger Battery + Thor EM-i Super Hybrid, Geely New Energy has thrown out two "king bombs"

- A brief discussion on functional safety - fault, error, and failure

- In the smart car 2.0 cycle, these core industry chains are facing major opportunities!

- The United States and Japan are developing new batteries. CATL faces challenges? How should China's new energy battery industry respond?

- Murata launches high-precision 6-axis inertial sensor for automobiles

- Ford patents pre-charge alarm to help save costs and respond to emergencies

- New real-time microcontroller system from Texas Instruments enables smarter processing in automotive and industrial applications

- 【GD32E503 Review】 + littlegl ported to GD32E503V-EVAL

- EEWORLD University ---- Deep Learning Course (NYU, Spring 2020) Yann Lecun

- Discover the world's most in-demand medical power supplies

- Great God Tesla ~AC~

- VICOR invites you to participate in the High Performance Power Conversion Seminar (venues: Beijing, Shenzhen, Shanghai, etc.)

- [TI recommended course] #Engineer It series course #Lesson 1 Loop bandwidth in phase-locked loop applications

- EEWORLD University ---- RS-485 Overview

- PicoVGA (1) VGA/TV driver library for Pico

- How to set up the serial port of 51 microcontroller to communicate with PC

- Step-by-step considerations for designing wide-bandwidth, multichannel systems

Signal Integrity Revealed: Dr. Yu\'s SI Design Notes

Signal Integrity Revealed: Dr. Yu\'s SI Design Notes High-Speed Digital Interface Principles and Test Guide

High-Speed Digital Interface Principles and Test Guide

京公网安备 11010802033920号

京公网安备 11010802033920号