As one of the most important diagnostic methods in traditional Chinese medicine, pulse diagnosis is characterized by ambiguity and uncertainty, and has become a hot topic in the modernization of traditional Chinese medicine in recent years. With the rapid progress of electronic and computer technology, the design of pulse diagnosis equipment combines embedded technology, FPGA technology, IP core technology, and integrates electronic technology, signal processing methods and other subject knowledge under the guidance of basic theories of traditional Chinese medicine. It has important practical significance and good market prospects to build a flexible, efficient, scalable, reliable, low-power, portable pulse acquisition instrument.

1 Overall design of the instrument

The early design goal of the embedded pulse acquisition instrument is the acquisition, storage, display, simple processing, communication, etc. of pulse signals. In the later stage, the collected signals should be processed to obtain pulse characteristics and make a diagnosis for the patient. When selecting FPGA, not only should we consider whether the current functions are sufficient and the price is moderate, but also consider the upgrading of products. Therefore, the designed system selects Alt-era's Cyclone II series EP2C35F484C8 as the core chip. The structural composition of the embedded pulse acquisition instrument with FPGA chip as the core is shown in Figure 1. As can be seen from Figure 1, the hardware is mainly composed of six modules, including power supply, display, memory, pulse acquisition, FPGA, and communication.

2 Main peripheral circuit design

Since the VGA controller IP core is used inside the FPGA, the 10-bit high-speed video DAC chip of Analog Instruments is selected.

The SRAM uses the IDT71V416 device of IDT, and two IDT71V416 devices are used to form a 32-bit memory to match the bus of the 32-bit CPU of NiosⅡ. For the control of SRAM, the SRAM controller core provided by Altera is selected, and its control signal is automatically generated by SoPC. SDRAM provides temporary storage space for data and stacks in the system. After the system is started, the program code is transferred to SDRAM to run to increase the running speed of the system. The system uses HYNIX's 64 MB SDRAM, model HY57V561620HT. It provides an LVTTL interface and is divided into 4 BANKs, each with a capacity of 4 M×16 b. The state of BA0 and BA1 determines which BANK is selected. The design of FLASH memory uses AMD's AM29LV128M device. The number of data bits can be freely selected as 16 bits or 8 bits, but the highest bit is the mode bit. The design is completed using IP core, which has relatively superior performance.

2.1 Design of communication module

Use very common serial port communication. RS 232 serial bus has the characteristics of simple structure, low cost, rich hardware and software support, and easy installation. Although the speed of RS 232 is a little slower, it is still sufficient for the acquisition of signals with a frequency less than 100 Hz. MAXIM's max3232 is used as the serial port conversion chip, with a power supply voltage of 3~5V and a speed of up to 1 Mb/s, which has good performance.

2.2 Design of pulse acquisition module

The pulse acquisition module includes sensors, instrument amplifiers, sample holders, A/D converters, etc., and is the key part of the pulse acquisition instrument.

The sensor of the pulse acquisition instrument determines the quality of the acquisition. The design uses a hard surface pressure sensor, model HK2000G pulse sensor of Huake Company. By using this sensor to design the system reasonably, the collected pulse signal can better meet the required standards.

The instrument amplifier AD620 of ADI is selected to amplify the collected pulse signal. AD620 is very suitable for pressure sensing applications. The design system needs to collect three pulse signals. In order to save the cost of analog-to-digital conversion and filtering of the pulse signal, an analog multiplexer is designed at the front end of the signal to perform multiplexing functions. When the pulse signal is weak, in order to introduce less noise, the AD7501 analog switch is used.

The A/D converter uses the AD678 data output with a sample-and-hold, high-precision reference power supply, internal clock and three-state buffer. It is an ADC with a 12-bit resolution and a conversion time of 5μs. It has the characteristics of simple external structure, easy use and high precision. [page]

3 Key circuit design of FPGA module

3.1 Design of pulse sampling controller

In order to simplify the design, the FPGA design of pulse acquisition control adopts the control circuit part outside the SoPC system, and then connects to the SoPC through the PIO of the SoPC. From the composition of pulse signal sampling, it can be seen that the pulse acquisition is connected to the FPGA only by the data line interface and the control line, and the three pulse signals and the three signals share one ADC.

Since the frequency of the pulse signal is relatively low, mostly below 100 Hz, the sampling frequency of the pulse signal of each channel is set to about 1 kHz to meet the sampling needs, that is, the three channels need to be cycled once at a time interval of 1 ms. Each channel goes through four steps: data acquisition initialization, start acquisition, data output, latch, etc., and the calculation time for each step is about 83μs. In other words, if each step can be completed within 83μs, an external clock with a cycle of 83μs can be used to control the state flip. The conversion time of AD678 is 5μs, and the operation time of NIOSⅡ is at the ns level, so the operation needs of each step can be fully completed within 83μs. The acquisition control part is divided into two parts, one part realizes the 83μs timing, and the other part is the acquisition state machine design. The 83μs is realized by the external clock frequency division method, and the conversion of the acquisition state machine is controlled by the output of the 83μs timing part. In the design of the state machine, the three parts of Cun, Guan, and Chi need to be cycled once, and each part includes 5 steps of sampling initialization, starting conversion, conversion end, and data storage. The specific source code is as follows:

[page]

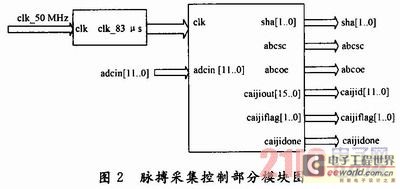

After the comprehensive acquisition part is fully compiled, it consists of two parts, as shown in Figure 2.

3.2 SoPC hardware design based on NiosⅡ

Using Altera's QuartusⅡ software and SoPCBuilder development tools, you can easily customize a complete system from hardware to software. The following modules need to be designed inside the FPGA: NiosⅡ, SRAM controller, SDRAM controller, EPCS controller, FLASH controller, timer, VGA controller, RS 232 controller, pulse acquisition controller, etc. Except for the pulse acquisition controller, which has no ready-made IP core available and needs to develop control timing, other controllers use the IP core provided by Altera.

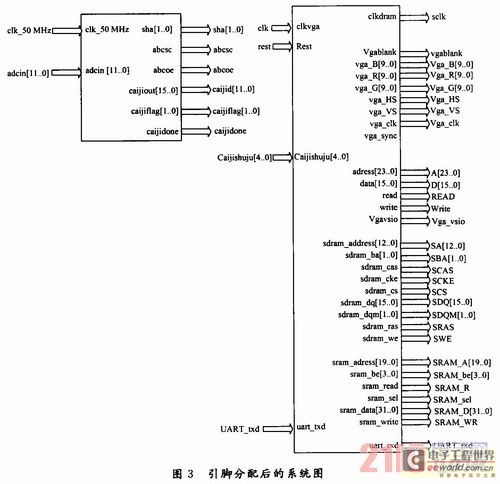

After the SoPC system is generated, a schematic window is established under QuartusⅡ, and the designed NiosⅡ system is called to connect with the control of the pulse acquisition system designed by yourself. After the design is completed, the pins are locked and the complete compilation is performed. The completed circuit is shown in Figure 3. After

compilation, it is configured to the FPGA in the system. The subsequent work is the transplantation of the embedded operating system and the development of embedded applications, at which time the hardware platform will be used.

4 Conclusion

The overall scheme of the embedded pulse acquisition instrument was designed, and the hardware circuit design of the pulse acquisition instrument based on FPGA was completed. According to the characteristics of pulse acquisition, the pulse acquisition circuit was designed, and the SoPC system of pulse acquisition was constructed using IP core. The designed pulse acquisition instrument has the characteristics of low cost, low power consumption, small size, easy expansion, easy use, high stability, high reliability, and easy system maintenance.

Previous article:How to use the tensile machine measurement and control system

Next article:Pressure measurement and control system of MPXM2010 and its precision improvement method

Recommended ReadingLatest update time:2024-11-16 23:58

- Popular Resources

- Popular amplifiers

-

Analysis and Implementation of MAC Protocol for Wireless Sensor Networks (by Yang Zhijun, Xie Xianjie, and Ding Hongwei)

Analysis and Implementation of MAC Protocol for Wireless Sensor Networks (by Yang Zhijun, Xie Xianjie, and Ding Hongwei) -

MATLAB and FPGA implementation of wireless communication

MATLAB and FPGA implementation of wireless communication -

Intelligent computing systems (Chen Yunji, Li Ling, Li Wei, Guo Qi, Du Zidong)

Intelligent computing systems (Chen Yunji, Li Ling, Li Wei, Guo Qi, Du Zidong) -

Summary of non-synthesizable statements in FPGA

Summary of non-synthesizable statements in FPGA

- Keysight Technologies Helps Samsung Electronics Successfully Validate FiRa® 2.0 Safe Distance Measurement Test Case

- From probes to power supplies, Tektronix is leading the way in comprehensive innovation in power electronics testing

- Seizing the Opportunities in the Chinese Application Market: NI's Challenges and Answers

- Tektronix Launches Breakthrough Power Measurement Tools to Accelerate Innovation as Global Electrification Accelerates

- Not all oscilloscopes are created equal: Why ADCs and low noise floor matter

- Enable TekHSI high-speed interface function to accelerate the remote transmission of waveform data

- How to measure the quality of soft start thyristor

- How to use a multimeter to judge whether a soft starter is good or bad

- What are the advantages and disadvantages of non-contact temperature sensors?

- Innolux's intelligent steer-by-wire solution makes cars smarter and safer

- 8051 MCU - Parity Check

- How to efficiently balance the sensitivity of tactile sensing interfaces

- What should I do if the servo motor shakes? What causes the servo motor to shake quickly?

- 【Brushless Motor】Analysis of three-phase BLDC motor and sharing of two popular development boards

- Midea Industrial Technology's subsidiaries Clou Electronics and Hekang New Energy jointly appeared at the Munich Battery Energy Storage Exhibition and Solar Energy Exhibition

- Guoxin Sichen | Application of ferroelectric memory PB85RS2MC in power battery management, with a capacity of 2M

- Analysis of common faults of frequency converter

- In a head-on competition with Qualcomm, what kind of cockpit products has Intel come up with?

- Dalian Rongke's all-vanadium liquid flow battery energy storage equipment industrialization project has entered the sprint stage before production

- Allegro MicroSystems Introduces Advanced Magnetic and Inductive Position Sensing Solutions at Electronica 2024

- Car key in the left hand, liveness detection radar in the right hand, UWB is imperative for cars!

- After a decade of rapid development, domestic CIS has entered the market

- Aegis Dagger Battery + Thor EM-i Super Hybrid, Geely New Energy has thrown out two "king bombs"

- A brief discussion on functional safety - fault, error, and failure

- In the smart car 2.0 cycle, these core industry chains are facing major opportunities!

- The United States and Japan are developing new batteries. CATL faces challenges? How should China's new energy battery industry respond?

- Murata launches high-precision 6-axis inertial sensor for automobiles

- Ford patents pre-charge alarm to help save costs and respond to emergencies

- New real-time microcontroller system from Texas Instruments enables smarter processing in automotive and industrial applications

- ADC/DCA chip manufacturers

- [RVB2601 Creative Application Development] — Some thoughts on unpacking and CDK installation

- This is how I became an unpaid garbage collector day by day. . .

- [Analysis of the topic of the college electronic competition] —— 2022 Provincial TI Cup F Topic "Signal Modulation Measurement Device"

- Electrochemical sensor signal processing circuit issues

- [2022 Digi-Key Innovation Design Competition] Desktop Robot Dog Material Unboxing

- EEWORLD University Hall----Live Replay: TI Ultrasonic Gas Flow Measurement Innovation Solution

- Cooperate to develop 8-bit MCU chip

- SPWM Program for DSP28035

- Problem with CCS installation

Analysis and Implementation of MAC Protocol for Wireless Sensor Networks (by Yang Zhijun, Xie Xianjie, and Ding Hongwei)

Analysis and Implementation of MAC Protocol for Wireless Sensor Networks (by Yang Zhijun, Xie Xianjie, and Ding Hongwei)

京公网安备 11010802033920号

京公网安备 11010802033920号