Understanding the three levels of circuit integration in one article

Levels of Integration

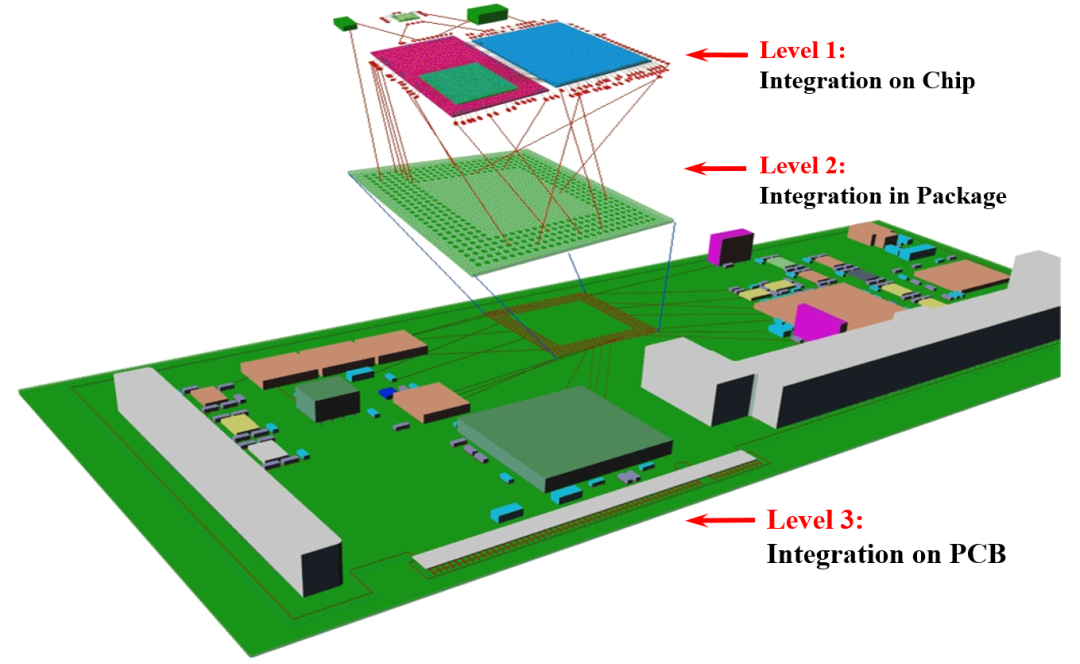

The integration of electronic systems is mainly divided into three levels: on-chip integration, in-package integration, and PCB board-level integration, as shown in the following figure:

The basic unit integrated on the chip is the transistor, which we call a functional cell. A large number of functional cells are integrated together to form a chip.

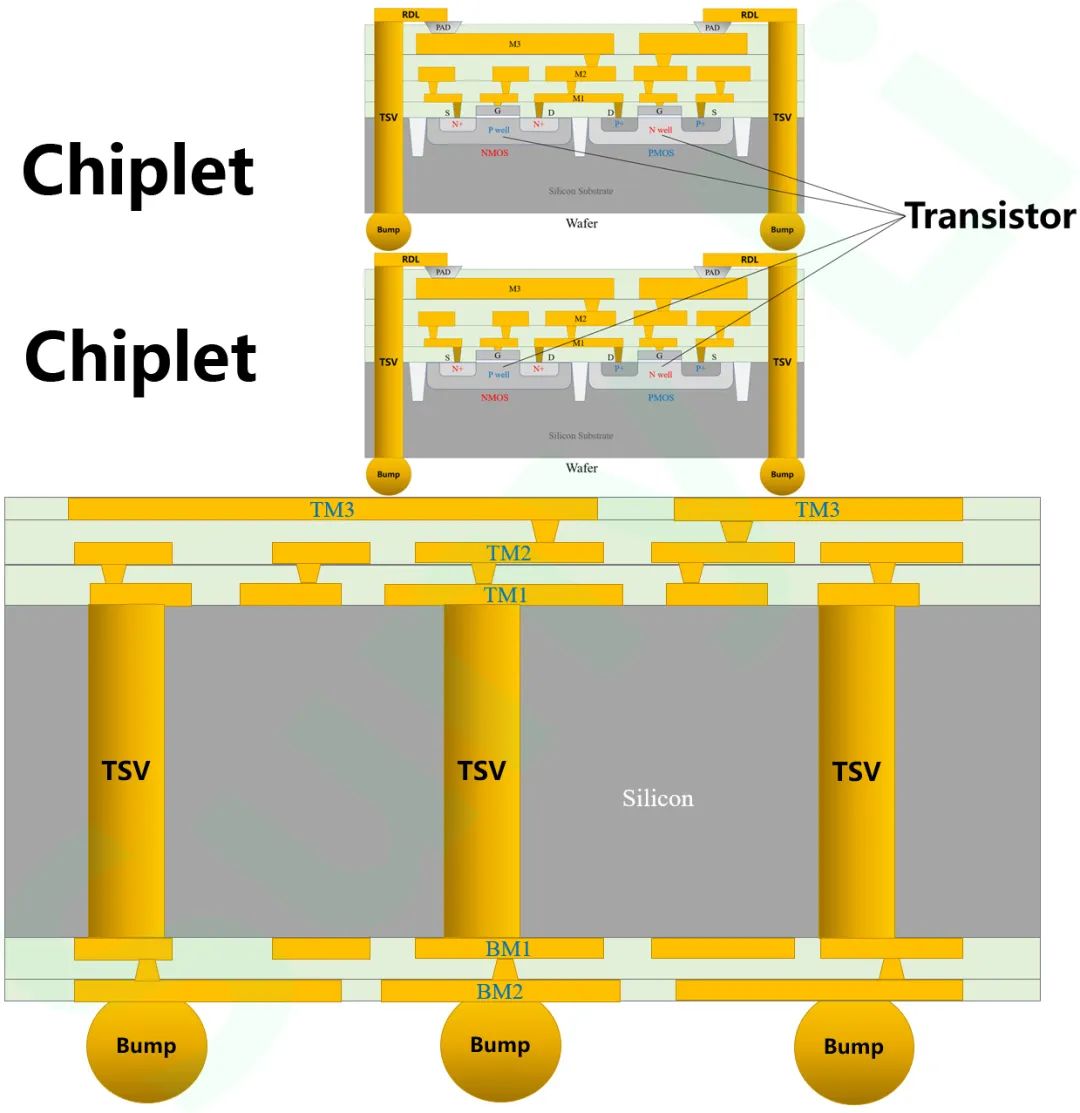

The basic unit integrated in the package is the bare chip or chiplet completed in the previous step, which we call the functional unit (Function Unit). These functional units are integrated in the package to form SiP.

The basic unit integrated on the PCB is the package or SiP completed in the previous step, which we call a microsystem. These microsystems are integrated on the PCB into a larger system.

It can be seen that the levels of integration are carried out step by step. The functions of each level of integration are constantly improved on the basis of the previous level, and the scale is constantly expanded.

At the PCB level, the functions of the electronic system have become relatively complete, and the scale has been enlarged to a level suitable for human control. Together with other components, it constitutes the system that people use most often - the common system, such as the mobile phones or computers we use every day.

On-chip integration

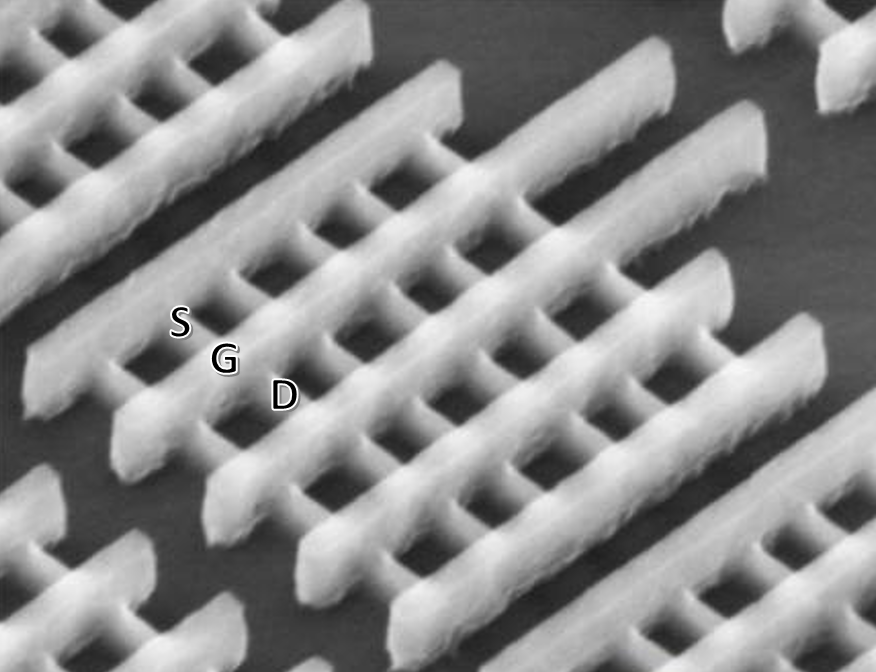

The transistor on a chip is called a functional cell because it is the smallest functional unit that cannot be divided.

The number of functional cells has also become an important indicator of the advancement of the system. The number of cells in the human body is 40 to 60 trillion. If the system wants to become a truly intelligent system like a human, the number of functional cells it contains may also reach the same level.

In order to integrate more

functional cells

, transistors can only be made smaller and smaller. The size of transistors today may be only one billionth of the size of the original transistors

when

they were first invented

, but their basic functions have not changed.

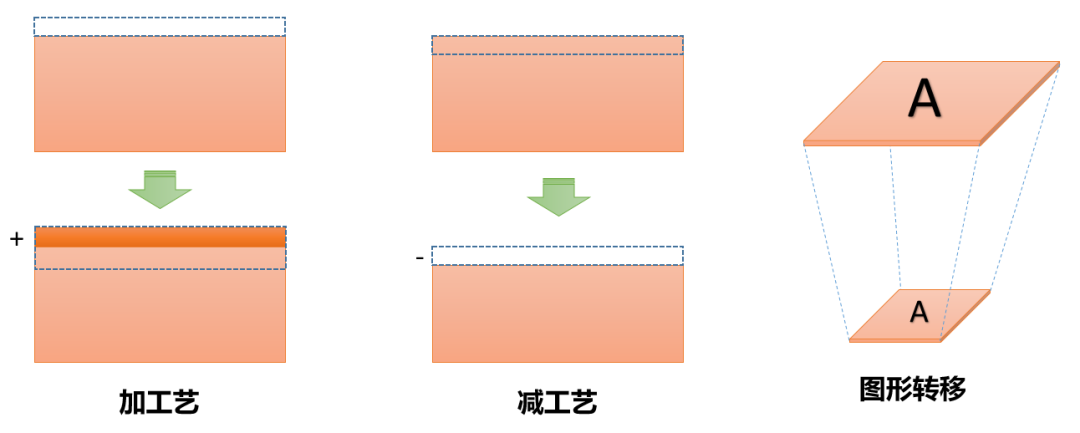

To integrate on a chip, we must first create functional cells and integrate them together. How are these transistors, which serve as functional cells, created and integrated together? From a very simple perspective, we need to understand three types of materials and three types of processes.

Conductors, semiconductors, insulators

Although there are many materials on the chip, the materials used in modern integrated circuits almost exhaust the periodic table. All materials can be divided into three categories: conductors, semiconductors, and insulators.

Conductors are responsible for transmitting electrons, and insulators are responsible for isolating electrons. The most important of these is naturally semiconductors, because they are variable. Sometimes they become conductors (on), allowing electrons to pass through, and sometimes they become insulators (off), blocking electrons from passing through. Moreover, this change is controllable by designing a special structure and applying current or voltage.

In conductors, the conduction band overlaps with the valence band, and there is no band gap, so electrons can easily move and form a current under an external electric field; in semiconductors, a small number of electrons can jump to the conduction band and form a current under an external electric field; in insulators, electrons cannot cross the band gap and therefore cannot form a current.

Integration in package

Not all chips or core particles need to be integrated in the package. Single chips can also be directly packaged and applied on PCB boards. However, as Moore's Law becomes increasingly ineffective, in-package integration is gaining more and more attention. Concepts such as SiP, advanced packaging, chiplet, heterogeneous integration, 2.5D, and 3D are becoming the focus of the industry, and in-package integration has finally ushered in its spring.

Integration on PCB

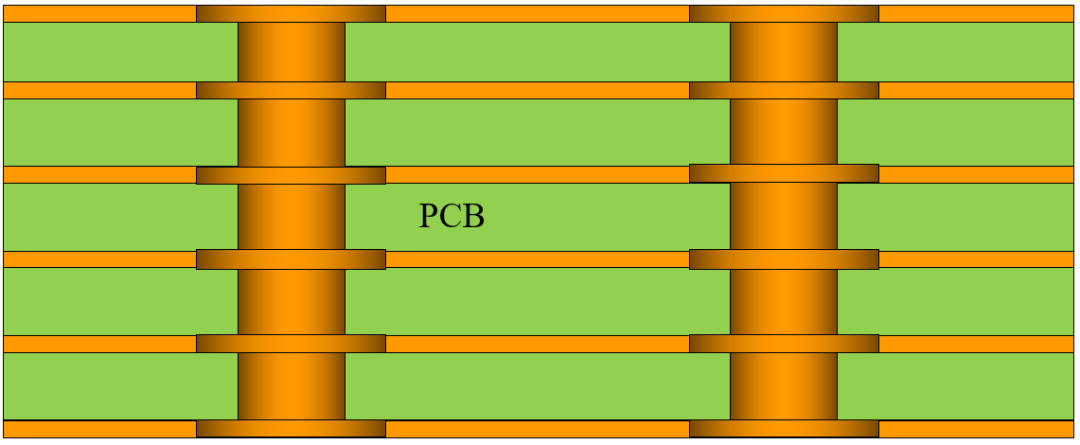

In terms of the history of electronic integration, integration on PCB should be the earliest to appear. PCB appeared 11 years earlier than packaging and 22 years earlier than integrated circuits.

Before the advent of PCBs, components were directly connected with wires, which was not only very messy but also difficult to improve integration density.

Although PCB has the earliest history compared with integrated circuits and packages, the development of integrated technology on PCB is relatively slow due to the constraints of package size and package pin density. From the initial single-sided board to double-sided board and multi-layer board, the assembly process has also developed from plug-in type to surface mount SMT, and the assembly density is getting higher and higher.

Today, components are basically installed on double-sided PCBs, and the number of board layers can reach dozens. High-density HDI boards, rigid-flexible boards, microwave circuit boards, embedded device boards, etc. are widely used.

Like the integration within the package, the integration on the PCB does not use the characteristics of semiconductors, so the materials used are mainly divided into two categories: conductors and insulators. The main purpose of integration is to integrate the microsystem modules completed at the previous level (integration within the package) again and interconnect them electrically, and together with other components, form a normal system, such as our commonly used mobile phones and computers.

Integrated links

Integrated links on chip

-

Device manufacturing (front-end process)

-

Metal interconnection (back-end process)

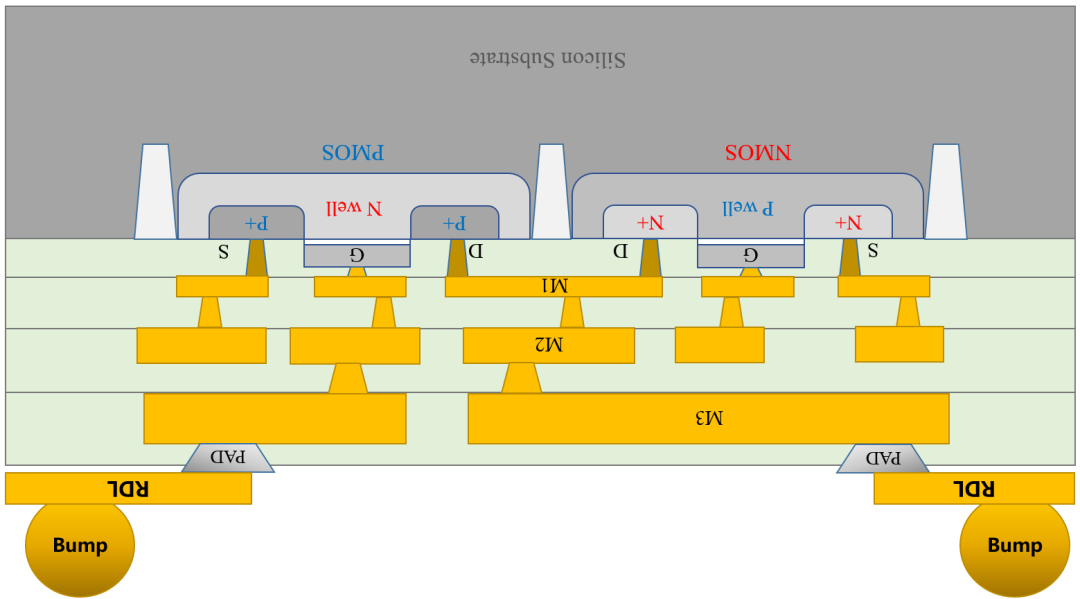

After the transistor layer is manufactured, contact holes are made through metals such as tungsten to connect the transistor and the first layer of wiring, and then electrical interconnection is carried out through multi-layer metal wiring and vias. Early chips used aluminum wiring, and now chips mostly use copper wiring.

The manufacture of multi-layer metal wiring used to connect devices such as transistors mainly includes the deposition of dielectrics between interconnect lines, the formation of metal lines, and the formation of lead pads, which is generally called the back-end of line (BEOL).

The conductors used in metal interconnects include metals such as tungsten, copper, and aluminum, while the insulators include silicon oxide, silicon nitride, high dielectric constant films, low dielectric constant films, polyimide, and the like.

The figure below shows a photo of the metal interconnect lines on the chip under a microscope. It can be seen that there are multi-layer wiring structures. The current process can support more than 10 layers of metal wiring.

The more advanced the integrated circuit technology is, the smaller the structure size is, and various effects emerge one after another. In order to solve these effects and produce functioning transistors, more and more types of elements are used, which is almost a movement to exhaust the periodic table.

The figure below shows the schematic diagram of the structure of the front-end process FEOL and the back-end process BEOL. Transistors are first manufactured on a silicon substrate, and then they are connected through metal interconnects and led out to the chip's PAD.

Integrated links in the package

-

RDL and TSV fabrication on chip

However, the current TSV technology is becoming increasingly powerful. It is said that up to one million TSVs can be etched in an area of 1mm², which can fully meet the needs of high-density interconnection.

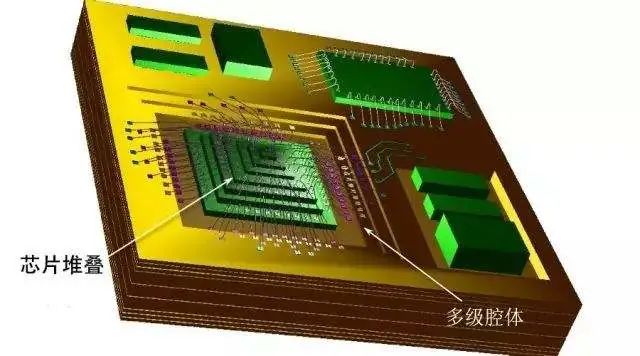

The figure below is a schematic diagram of TSV on the chip. Through TSV, the upper and lower surfaces of the chip can be connected through metal conductors, preparing for chip stacking.

It is extremely difficult to make TSV on a chip, and only leading foundries can do it. This type of TSV is usually called 3D TSV.

In order to further improve the integration level, people have invented a method of making TSV on a silicon substrate interposer, which is called 2.5D TSV.

-

RDL and TSV fabrication on Interposer

Interposer is called silicon transfer board, interposer, which can provide higher interconnection density than ordinary substrate.

The following figure shows a typical silicon adapter board , with 3 metal layers on the top and 2 metal layers on the bottom, connected by silicon vias in the middle. We call it a 3+2 structure.

-

Interconnection fabrication on Substrate

Next, we need to make the packaging substrate. There are many types of packaging substrate materials, which can be divided into organic substrates and ceramic substrates.

-

Device assembly and packaging

Next, we assemble the Chiplet, Inteposer, and Substrate and process them using advanced packaging technology to form a complete advanced package.

The result of integration within the package has the functions of the system and is small in size. We can call it SiP or microsystem.

Integrated links on PCB

-

Fabrication of PCB interconnection lines

-

Component assembly on PCB

Full picture from transistor to PCB

(Readers are advised to save this picture, because this picture may be the first in the industry to show the 5-level circuit integration from transistor to PCB , drawn by hand by Suny Li. Because it is a schematic diagram, it is not drawn strictly according to the scale. In fact, the size is enlarged by about 1,000,000 times from transistor to PCB)

Recommended Reading

Add WeChat and reply " join group"

Invite you to join the technical exchange group!

Domestic chips|Automotive electronics|Internet of Things|New energy|Power supply|Industry|Embedded...

Reply to any content you want to search in

the

official

, such as problem keywords, technical terms, bug codes, etc.,

and you can easily get relevant professional technical content feedback

. Go and try it!

If you want to see our articles more often, you can go to our homepage, click the "three dots" in the upper right corner of the screen, and click "Set as Star".

京公网安备 11010802033920号

京公网安备 11010802033920号