The Time Appliance Project (TAP) is Facebook's latest open source system for sub-microsecond network time synchronization, which aims to provide very accurate timing and time synchronization across data centers in a cost-effective manner.

Data centers require synchronized time between servers, databases, and services to facilitate a wide range of applications such as electronic transactions, voice and video, and wireless sensor networks.

Recently, Facebook released Time Card, an open source x86 PCIe interface card designed to provide precise synchronization to tens of nanoseconds. The Time Device project includes all the hardware on the Time Card.

Facebook's time card/time device solution. Image courtesy of Ahmad Byagowi

At the heart of the card's design is u-blox's RCB-F9T timing board. u-blox's ZED-F9T multi-band timing module is also considered a key technology in Facebook's latest hardware project.

Facebook launched TAP in partnership with Open Compute with the goal of fully open sourcing the project and solving many of the problems associated with proprietary time devices.

Learn more about Time Appliance hardware

The Time Appliance project is available as a GIT repository and includes hardware files, software files, bill of materials, and details about the Precision Time Protocol (PTP) profiles developed within OCP.

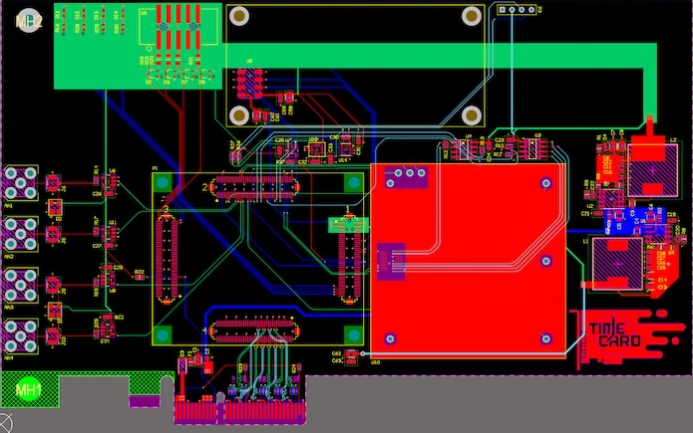

The time card itself, which forms part of the time device project interface, was built in Altium Designer. It is not a high-density design. However, as the design is intended to interface with relatively high-frequency GNSS systems, signal integrity and EMC data would be a welcome addition to the GIT file.

The PCB is a 62 mil thick six-layer board using two ground reference planes on layers 2 and 5. Layers 3 and 4 are orthogonally routed to avoid significant effects of broadside coupling.

Time card PCB layout (reference planes disabled) detailing the layout design and density. Image from Facebook design files

Building the Time Appliance Project

The Time Appliance is built using three main hardware components:

GNSS timing source (RCB-F9T board from u-blox)

Miniaturized Rubidium Atomic Clock (Microchip's MAC-SA5X)

System-on-Module FPGA (Alinx's Artix-7 AC7100B SoM)

Time Card prototype. Image courtesy of Facebook

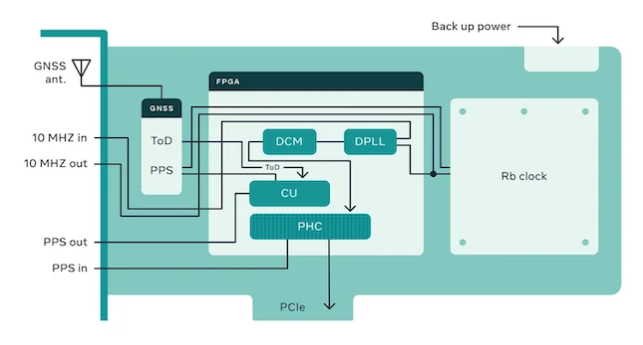

The FPGA system receives two main signals from the GNSS: a pulse per second (PPS) reference signal and a time of day (ToD) signal. The system is clocked by a rubidium oscillator or an external 10 MHz.

After filtering and processing the two synchronization signals, the resulting reference signal is output to the PCI bridge to the x86 system network interface card (NIC).

High-level block diagram of the Time Appliance FPGA. Image courtesy of Facebook

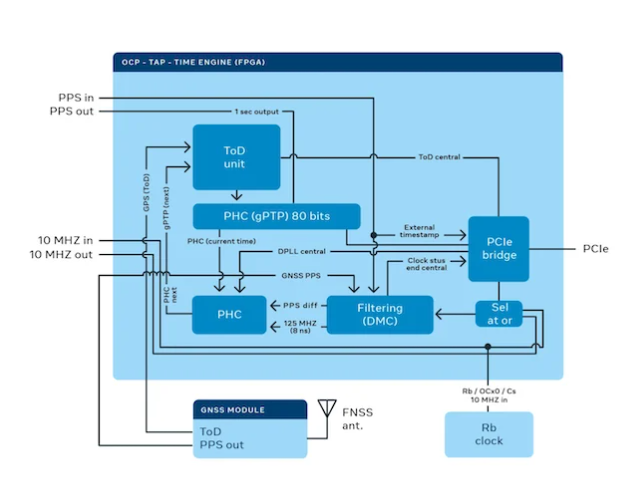

Digging deeper into the FPGA subsystem, Facebook outlines the filtering of the GNSS input signal (DCM).

FPGA digital filtering subsystem. Image courtesy of Facebook

Ultimately fed into the ToD unit, these filtered signals represent the accumulated increments of 8 nanosecond digital values. The goal is to take a snapshot of the incremental digital counts using the GNSS signal to achieve an ideal 1 second PPS.

The system has built-in redundancy, allowing the MAC to take over for a period of time in the absence of GNSS signals; specifically, the incremental digital count should be maintained within 1 microsecond over a 24-hour period to achieve the defined time loss accuracy.

The card is designed to interface with any x86 host system that has a hardware timestamping capable NIC, turning it into a “time device.” Synchronization of the system is protocol agnostic, allowing use of the Network Time Protocol (NTP), Precision Time Protocol, or other alternative synchronization protocols.

Why did Facebook choose to open source TAP?

TAP is not the first open source project Facebook has released to the wider community. In 2011, Facebook publicly released the design of its state-of-the-art data center and launched the Open Compute Project Foundation with other industry members.

Facebook has recognized the difficulties of using proprietary systems: long development times to patch security holes, closed-system software with limited configurability, hardware that is not user-serviceable, and high costs.

The time card is a relatively cost-effective timing card that can be built using COTS components and PCB design, lowering the entry barrier to the sub-microsecond synchronization market.

All in all, as an open source project, there is much more information available to interested designers, including hardware, software, or available protocol stacks.

Previous article:

Next article:最后一页

Recommended ReadingLatest update time:2024-11-16 14:43

- Popular Resources

- Popular amplifiers

-

A review of deep learning applications in traffic safety analysis

A review of deep learning applications in traffic safety analysis -

ESP32 steuert Roboterauto Open-Source-Code mit Arduino IDE and PlatformIO Autonomes Fahren GPS, Acce

ESP32 steuert Roboterauto Open-Source-Code mit Arduino IDE and PlatformIO Autonomes Fahren GPS, Acce -

CVPR 2023 Paper Summary: Video: Low-Level Analysis, Motion, and Tracking

CVPR 2023 Paper Summary: Video: Low-Level Analysis, Motion, and Tracking -

ICCV2023 Paper Summary: Self-, Semi-, Meta-, Unsupervised Learning

ICCV2023 Paper Summary: Self-, Semi-, Meta-, Unsupervised Learning

- Wi-Fi 8 specification is on the way: 2.4/5/6GHz triple-band operation

- Three steps to govern hybrid multicloud environments

- Microchip Accelerates Real-Time Edge AI Deployment with NVIDIA Holoscan Platform

- Keysight Technologies FieldFox handheld analyzer with VDI spread spectrum module to achieve millimeter wave analysis function

- Qualcomm launches its first RISC-V architecture programmable connectivity module QCC74xM, supporting Wi-Fi 6 and other protocols

- Microchip Launches Broadest Portfolio of IGBT 7 Power Devices Designed for Sustainable Development, E-Mobility and Data Center Applications

- Infineon Technologies Launches New High-Performance Microcontroller AURIX™ TC4Dx

- Rambus Announces Industry’s First HBM4 Controller IP to Accelerate Next-Generation AI Workloads

- NXP FRDM platform promotes wireless connectivity

- Innolux's intelligent steer-by-wire solution makes cars smarter and safer

- 8051 MCU - Parity Check

- How to efficiently balance the sensitivity of tactile sensing interfaces

- What should I do if the servo motor shakes? What causes the servo motor to shake quickly?

- 【Brushless Motor】Analysis of three-phase BLDC motor and sharing of two popular development boards

- Midea Industrial Technology's subsidiaries Clou Electronics and Hekang New Energy jointly appeared at the Munich Battery Energy Storage Exhibition and Solar Energy Exhibition

- Guoxin Sichen | Application of ferroelectric memory PB85RS2MC in power battery management, with a capacity of 2M

- Analysis of common faults of frequency converter

- In a head-on competition with Qualcomm, what kind of cockpit products has Intel come up with?

- Dalian Rongke's all-vanadium liquid flow battery energy storage equipment industrialization project has entered the sprint stage before production

- Allegro MicroSystems Introduces Advanced Magnetic and Inductive Position Sensing Solutions at Electronica 2024

- Car key in the left hand, liveness detection radar in the right hand, UWB is imperative for cars!

- After a decade of rapid development, domestic CIS has entered the market

- Aegis Dagger Battery + Thor EM-i Super Hybrid, Geely New Energy has thrown out two "king bombs"

- A brief discussion on functional safety - fault, error, and failure

- In the smart car 2.0 cycle, these core industry chains are facing major opportunities!

- The United States and Japan are developing new batteries. CATL faces challenges? How should China's new energy battery industry respond?

- Murata launches high-precision 6-axis inertial sensor for automobiles

- Ford patents pre-charge alarm to help save costs and respond to emergencies

- New real-time microcontroller system from Texas Instruments enables smarter processing in automotive and industrial applications

- 【ST NUCLEO-G071RB Review】TIM-PWM

- [NXP Rapid IoT Review] Hello World project reads sensor values that are always 0

- A few questions for help

- MSP430AFE2xx series of metering analog front-end 16-bit MCU

- A brief tutorial on DSP interrupt settings

- Request a free ZVS buck regulator evaluation board

- Is there any chip that can convert analog signal (potentiometer and DC voltage) into PWM dimming signal?

- Infrared thermometer

- The difference between ordinary diode and Zener diode

- FPGA controls the DSP power-on reset procedure.

A review of deep learning applications in traffic safety analysis

A review of deep learning applications in traffic safety analysis CVPR 2023 Paper Summary: Video: Low-Level Analysis, Motion, and Tracking

CVPR 2023 Paper Summary: Video: Low-Level Analysis, Motion, and Tracking

京公网安备 11010802033920号

京公网安备 11010802033920号