Introduction

The DS80C400 evaluation board includes the TINIm400 reference circuit board and TINIs400 socket board, which provides an excellent platform for evaluating the TINI operating environment and developing TINI-based applications using the DS80C400 network microcontroller. One drawback of the TINIm400/TINIs400 combo board is its limited general-purpose IO (GPIO) pin count. The TINIs400 socket board only contains a few pins that can be conveniently used as GPIO; most of the IO pins on the socket board are spread across the board and are used for other functions (e.g., J27 is an I2C pin and J4 is an external interrupt pin).

This application note demonstrates step-by-step how to configure the hardware and develop software using a Complex Programmable Logic Device (CPLD) to provide an additional 32 GPIO pins for the TINIs400 socket board.

Hardware Setup

The first step in expanding TINI's IO capabilities is to install four additional devices on the TINIs400 socket board: a CPLD, a power regulator, and two headers. The TINIs400 socket board sold by Dallas Semiconductor does not have these devices installed, but has pads and traces reserved for adding these devices. These devices are not installed on the board because many applications do not require extended IO performance or require custom board designs.

Page 7 of the TINIs400 circuit schematic 1 details the components necessary to extend TINI IO performance. This circuit uses a Xilinx XC2C64 CoolRunner-II CPLD in a 100-pin VQFP package.

Both the XC2C64 and the larger XC2C128 have been tested on the TINI hardware platform, which also supports other device sizes with the same pinout and the same package. There are three plugs related to CPLD, two of which are required to be installed. The specific instructions are as follows:

J30 JTAG programming connector. Program the XC2C64 CPLD through the JTAG interface. The J30 connector provides pins for the JTAG signals TMS, TCK, TDI, and TDO. See the CPLD Programming section below for a more detailed discussion.

J28 expansion IO connector. This connector provides access to 32 pins of the XC2C64 device. Programming the CPLD will provide a read/write interface to these pins.

J29 extra IO connector. This connector provides 16 additional connections to the XC2C64, which are not used in this design.

In addition to the J30 and J28 headers, the following components need to be installed:

U2 MAX1792EUA18 regulator

U12 Xilinx CPLD

capacitors C40 to C57. These capacitors are only required if using a CPLD, the TINIs400 socket board obtained from Dallas Semiconductor should have these capacitors installed. If the installation location is incorrect or missing, it may not be noticed during other TINI development.

CPLD configuration

CPLD is a programmable logic device. Think of it as programmable hardware with very flexible internal logic that allows many functions to be implemented with simple reprogramming. A 32-bit flip-flop can be implemented with CPLD to store the logic level of the CPLD output pin. Verilog, a hardware description language (HDL), is used to describe the functions to be implemented by the CPLD. The tools provided by Xilinx can convert Verilog source code into binary form for configuring CPLD.

On the TINIs400 circuit board, the XC2C64 is connected to the memory bus of the TINI microcontroller DS80C400. This connection allows TINI programs to access the CPLD by reading and writing specific addresses. Therefore, the CPLD must be programmed to respond correctly when the address line selects the CPLD; the CPLD must latch the data bus signal being written, and the port input must be driven when the CPLD is read.

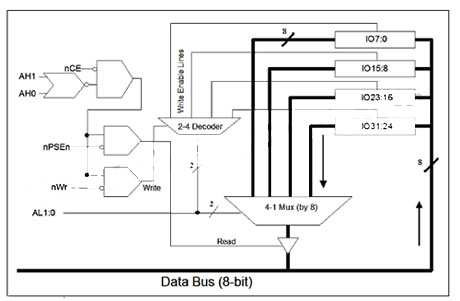

Figure 1. CPLD functional block diagram |

Figure 1 is a functional block diagram that needs to be implemented by CPLD. The modules in the upper right part of the figure (IO7:0, IO15:8, IO23:16, IO31:24) represent flip-flops that store output level values. Each of these 8-bit register sets is connected to the data bus. When enabled via the appropriate address line and write strobe signal (nWr), the contents of the data bus are latched into the register. The input level of the IO pin is detected and sent to the 4:1 multiplexer. At this time, the low-order address selects the 8-bit value and passes it to the data bus. If the CPU requests a read (enabled by the address line and nPSEN signal), the output of the multiplexer is enabled and drives the data bus.

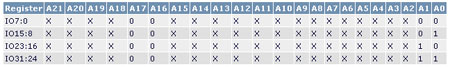

Although 10 address lines (not including chip enable) are connected to the CPLD, this example application uses only four of them. A17:A16 high address line is used together with chip enable 6. When address bits A17:A16 are low and nCE6 is active (low), CPLD is selected, but CPLD has no effect until the read or write signal is active. The other two address bits, A1:A0, are used to select one of the four 8-bit registers as the target address for a write operation or the source address for a read operation. This addressing scheme means that many addresses enable access to the four 8-bit registers. Table 1 summarizes the flexibility of this addressing scheme.

Table 1. Address line values that can activate the CPLD register

|

Since the TINI library and working firmware configure DS80C400 to correspond to 2MB space for each chip enable end, and the address range of DS80C400 is 24 bits (16MB), the eight chip enable ends correspond to the high 3 bits of the address. To activate chip enable 6, the upper 3 bits of the 24-bit address must be 110b.

Although Table 1 indicates that multiple addresses can activate the register, we only used the following register addresses:

地址C00000h IO7:0

地址C00001h IO15:8

地址C00002h IO23:16

地址C00003h IO31:24

Verilog编码

有六个Verilog文件用来实现CPLD的32位GPIO功能。本应用笔记的源代码中包含了这些文件,并附带提供Xilinx WebPACK(参见下文的讨论)工程文件。本工程的Verilog源文件包括:

Buffer8.v:8位缓冲器,用来连接TINI到四个8位寄存器的数据总线。

Mux2x8.v:2:1多路复用器,用来选择两条8位总线中的一条。

OneO4e.v:2-4译码器,输出一个取决于低地址位的有效信号。

Reg8OD.v:8位伪开漏极触发器阵列,用来存储输出值。

TSBuffer8.v:8位三态缓冲器,用来驱动数据总线输入值。

CPLD.v:模块间的顶层连接。

最应引起注意的Verilog源文件是CPLD.v。它包含输入、输出和节点的定义,并且给出在其它文件中定义的实例化模块。该源文件也是提取写脉冲和读脉冲的地方:

assign Reset = ~nRstOut; // make a hi-active Reset

assign IOBank = ~nCE6 & ~|AH; // decode the I/O bank

assign ReadT = IOBank & ~nPSEn; // qualify Read strobe

assign WriteT = IOBank & ~nWr; // qualify Write strobe

然后将信号ReadT作为三态缓冲器的使能信号,使用检测到的输入值驱动DS80C400的数据总线:

// Tri-State data bus to TINI needs this buffer

TSBuffer8 U4(ReadT, DataToTINI, D);

信号WriteT送入四个8位寄存器组作为时钟信号。

// 4 8-bit pseudo-open-drain output drivers

Reg8Out U6(Reset, ~WriteT, Enable[0], DataFromTINI, UIO[ 7: 0]);

Reg8Out U7(Reset, ~WriteT, Enable[1], DataFromTINI, UIO[15: 8]);

Reg8Out U8(Reset, ~WriteT, Enable[2], DataFromTINI, UIO[23:16]);

Reg8Out U9(Reset, ~WriteT, Enable[3], DataFromTINI, UIO[31:24]);

另一个重要的源文件(虽然不是Verilog文件)是CPLD.ucf。该文件给出了CPLD.v中声明的信号名称和XC2C64器件实际引脚之间的映射关系。地址线和几个IO引脚的定义如下:

NET "AL<1>" LOC = "P30";

NET "AL<0>" LOC = "P32";

NET "AH<1>" LOC = "P37";

NET "AH<0>" LOC = "P39";

NET "UIO<5>" LOC = "P43";

NET "UIO<6>" LOC = "P49";

NET "UIO<7>" LOC = "P50";

NET "UIO<8>" LOC = "P52";

NET "UIO<9>" LOC = "P53";

注意,这些引脚定义直接来自TINIs400电路原理图的第7页。例如,从电路图可以看出:地址线3-0 (A[3:0])连接到引脚28、29、30和32。如以上清单所示,我们定义了两条最低地址线信号(AL<1>和AL<0>),它们被映射至CPLD的引脚30和32。

CPLD编程

用于CPLD编程的工程文件包含在本应用笔记的源代码CPLD目录内。可以使用Xilinx的免费Webpack工具来构建并编程CPLD。本应用笔记中的应用实例是用6.3.03i版本开发的。只要支持CoolRunner 2 CPLD系列,Xilinx工具的最新版本应该也适合本设计。

硬件连接

我们使用Avnet Avenue JTAG编程电缆来连接计算机的并口和CPLD的JTAG引脚。许多CPLD或FPGA评估套件均提供JTAG编程电缆。本文使用的编程电缆如图2所示。

图2. Avnet Avenue JTAG编程电缆 |

图3为编程电缆和TINIs400插座板之间所需的连接。对信号做了标记,因此也可以用其他编程电缆。TINIs400插座板要求VCC为3.3V。

图3. JTAG编程器与TINIS400插座板的连接关系。J30上未标注的引脚没有连接。 |

载入工程时,点击File菜单并选择Open Project。浏览本应用笔记的源文件并选择parallel32.npl。现在已经打开工程并准备构建。接下来说明如何配置一个全新的工程。也可以跳过这一节,直接浏览后面的部分了解如何编程CPLD。

遵照以下指导说明,根据应用笔记提供的源代码创建一个新工程。

Select New Project from the File menu.

Select the directory where you want to create a new project and enter the project name. A new directory named with the project name will be created. Make sure the Top Level Module Type is HDL. Click Next to continue.

Select the device and package required for the project in the next menu. Device family selection CoolRunner 2 CPLDs. Then select the device from the list given - it can be XC2C64, XC2C128 or other similar devices. The package is VQ100, which is the package certified by TINIs400 socket board. See Figure 4 for other configuration options used in this application note. After completing the configuration, click Next to continue.

Figure 4. Configuring the device and design flow for a new project |

The next window asks for all new files to be created in the new project. Since all source files have been provided, click Next and no new files will be added.

The next window asks for adding any existing source files. Click the Add Source button to add all Verilog files provided by the source code (see the Verilog Encoding section above for the file list) and the CPLD.ucf file. Once added, the program will ask: File.v is which source type The suffix is ambiguous as to type (File.v is which file type, the suffix type is ambiguous). Select Verilog Design File and click OK (see Figure 5). After all input files have been classified, click Next to continue.

Figure 5. Determining the file type of the input source file |

The next window summarizes basic information about the new project. Review the information and click Finish.

As long as the UCF file is added in step 5 above, the program will ask to associate the file to the content it affects. Select the CPLD in the list and click OK.

At this point, project creation and configuration are completed. Now you can edit, build, and synthesize your design.

Device Programming

Follow the instructions below to synthesize the CPLD project and program the XC2C64 device. Make sure the programming cable is connected as described in the Hardware Connections section above.

CPLD programming:

Select the Module View tab in the Project View (usually in the upper left part of the window). Select the main file CPLD.v in Module View.

In the Process View window (usually in the lower part of the Project View window), expand the Implement Design branch and double-click Generate Programming File. This will run all the processes needed to convert the Verilog source code into binary files (used for programming the CPLD). When a process is run, a marker describing the results of the execution will appear to the left of the process. A green checkmark means the process ended successfully without errors or warnings. A yellow exclamation point means the process ended successfully, but with a warning message. The red X means that the process did not end successfully and an error occurred.

Once the program ends and the programming files are successfully generated, double-click Configure Device (IMPACT).

A window will appear showing Configure Devices. Select the Boundary Scan Mode option and click Next.

In the next window (Boundary-Scan Mode Selection), select Automatically connect to cable and identify Boundary Scan chain and click Finish.

If the device is connected correctly, iMPACT will pop up a window saying "There was one device detected in the boundary-scan chain. iMPACT will now direct you to associate a programming or BSDL file with this device....". Click OK.

A file dialog window should be opened in the current project directory (if it is not opened in this directory, its correct location should be found). Double-click to select CPLD.jed in this window.

Right-click on the Xilinx chip diagram and select Program.

Make sure Erase Before Programming and Verify is selected and nothing else is selected. Click OK.

At this time, the programming status progress bar will appear. After a few seconds (less than 20 seconds), programming will be completed and the CPLD configuration will be completed.

When designing your own CPLD function, when the DS80C400 is not communicating with the CPLD, you should ensure that the CPLD code releases the address, control and data signals to a high-impedance state. Ignoring this is a common mistake and can lead to strange behavior, such as the board being held in reset or randomly rebooting. When such a problem occurs, simply erasing the CPLD can prevent the problem.

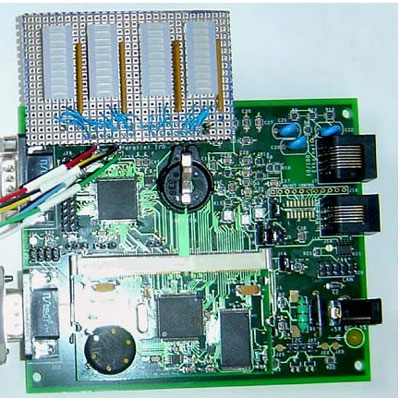

The debugging circuit board

can demonstrate TINI's IO expansion performance simply with the help of 32 LEDs. The demo board uses four sets of LEDs and four resistor rows to indicate the status of each CPLD IO pin. The LED board (mounted on TINIs400) is shown in Figure 6.

Figure 6. TINIs400/TINIm400 with debug IO board installed |

The schematic for this simple circuit board is included in the source code of this application note. Note that the resistance values are recommended values; a resistance value that is too high will result in a darker display, and a resistance value that is too low will consume too much TINI power supply current and abort the execution process.

After the software interface

is implemented as a simple memory interface, software access to the extended IO pins becomes quite simple, and will be implemented in assembly language (embedded in Java applications as native functions).

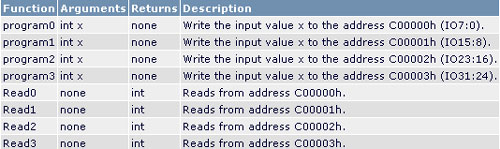

Table 2 shows the Java native functions defined to implement interface functions.

Table 2. Java functions used by the TINI-CPLD interface

|

Note that you can also use two functions to accomplish the same job: program(int address, int x) and read(int address). However, in this application we choose to allocate one function per address, which allows the application to extract different addresses as functional registers. The assembler code and read functions for each program are fairly simple. The code only requires loading the data pointer at the correct address and then activating the memory bus with a movx instruction.

Native_program0:

clr a ; request first parameter

lcall NatLib_LoadPrimitive ; load parameter into r3:r0

mov dptr, #0C00000h ; point to memory mapped peripheral

mov a, r0 ; move low byte of source into accumulator

movx @dptr, a ; write to memory mapped peripheral

clr a ; indicate no error condition

ret ;

...

Native_read0:

mov dptr, #0C00000h ; point to memory mapped peripheral

movx a, @dptr ; read from memory mapped peripheral

mov r0, a ; move into low byte of result

clr a ; indicate no error condition

mov r1, a ; unsigned extend to 32-bits

mov r2, a ; unsigned extend to 32-bits

mov r3, a ; unsigned extend to 32-bits

ret ;

Application Example

The application example is in the javacode folder of the source code. The application writes incremental values to four groups of LEDs. This value is updated every 500ms, so it is easy to know whether the application is running correctly.

Because the application includes native functions and Java code, the build process is more complex than a pure Java program. The source code contains build batch files, but requires some modifications for the system you develop, as detailed below:

c:\work\tini\tini1.16

ative\bin\win32\macro -Ic:\work\tini\tini1.16

ative\lib\ cpld.a51Change

directory so that it points to the macro precompilation processor and native library ( native library) contains the location on your hard drive where the files are stored. These projects are part of the standard TINI SDK and can be downloaded from ftp.dalsemi.com/pub/tini/index.html.

c:\work\tini\tini1.16

ative\bin\win32\a390 -f 1.16 -p 400 -l cpld.mpp

changes the directory so that it points to the address of the a390 assembler. They are stored in the same directory as the macro precompiler processor.

del *.class

deletes a previously existing class from the current directory.

javac -bootclasspath C:\work\tini\tini1.16\bin\tiniclasses.jar demo.java

does not consider the TINI class file and builds the source file demo.java. Change directories to point to TINI's API classes, which are part of the TINI SDK.

java -classpath C:\work\tini\tini1.16\bin\tini.jar;%classpath% TINIConvertor -n cpld.tlib -f . -o demo.tini -d C:\work\tini\tini1.16\ bin\tini.db

combines the local library to build the TINI executable file to implement the interface with CPLD. The Java code only needs to call the function.

System.loadLibrary("cpld.tlib")

In order to access the extended IO pins of CPLD, you need to change the directory again so that it points to the tini.jar tool file and tini.db class database included with the TINI SDK.

Conclusion

The combination of TINI and CPLD provides a simple interface that can expand IO performance and is highly flexible. However, when using programmable logic devices, their functions are not limited to expansion IO. CPLDs can be used to implement many logic functions and state machines. Used in conjunction with the TINI network stack, Java virtual machine, and operating system, CPLD makes the TINI system highly configurable and flexible.

Previous article:Image acquisition and processing system based on ADSP-TS201S

Next article:Image acquisition and processing system based on ADSP-TS201S

- Huawei's Strategic Department Director Gai Gang: The cumulative installed base of open source Euler operating system exceeds 10 million sets

- Analysis of the application of several common contact parts in high-voltage connectors of new energy vehicles

- Wiring harness durability test and contact voltage drop test method

- Sn-doped CuO nanostructure-based ethanol gas sensor for real-time drunk driving detection in vehicles

- Design considerations for automotive battery wiring harness

- Do you know all the various motors commonly used in automotive electronics?

- What are the functions of the Internet of Vehicles? What are the uses and benefits of the Internet of Vehicles?

- Power Inverter - A critical safety system for electric vehicles

- Analysis of the information security mechanism of AUTOSAR, the automotive embedded software framework

Professor at Beihang University, dedicated to promoting microcontrollers and embedded systems for over 20 years.

Professor at Beihang University, dedicated to promoting microcontrollers and embedded systems for over 20 years.

- Innolux's intelligent steer-by-wire solution makes cars smarter and safer

- 8051 MCU - Parity Check

- How to efficiently balance the sensitivity of tactile sensing interfaces

- What should I do if the servo motor shakes? What causes the servo motor to shake quickly?

- 【Brushless Motor】Analysis of three-phase BLDC motor and sharing of two popular development boards

- Midea Industrial Technology's subsidiaries Clou Electronics and Hekang New Energy jointly appeared at the Munich Battery Energy Storage Exhibition and Solar Energy Exhibition

- Guoxin Sichen | Application of ferroelectric memory PB85RS2MC in power battery management, with a capacity of 2M

- Analysis of common faults of frequency converter

- In a head-on competition with Qualcomm, what kind of cockpit products has Intel come up with?

- Dalian Rongke's all-vanadium liquid flow battery energy storage equipment industrialization project has entered the sprint stage before production

- Allegro MicroSystems Introduces Advanced Magnetic and Inductive Position Sensing Solutions at Electronica 2024

- Car key in the left hand, liveness detection radar in the right hand, UWB is imperative for cars!

- After a decade of rapid development, domestic CIS has entered the market

- Aegis Dagger Battery + Thor EM-i Super Hybrid, Geely New Energy has thrown out two "king bombs"

- A brief discussion on functional safety - fault, error, and failure

- In the smart car 2.0 cycle, these core industry chains are facing major opportunities!

- The United States and Japan are developing new batteries. CATL faces challenges? How should China's new energy battery industry respond?

- Murata launches high-precision 6-axis inertial sensor for automobiles

- Ford patents pre-charge alarm to help save costs and respond to emergencies

- New real-time microcontroller system from Texas Instruments enables smarter processing in automotive and industrial applications

- How to understand these four statements in STM32F103RCT6? The return statement should be declared before the main function, right?

- MSP430 JTAG interface and BSW interface

- NXP launches new MCX series, high performance with NPU, to replace LPC and Kinetis?

- Share the disassembly of IPP-5002

- [Raspberry Pi Pico Review] --- Getting Started

- The 2019 STM32 National Tour Seminar is about to start. Register now to win three gifts

- Problems of overcurrent and overvoltage protection in voltage doubler rectifier circuit

- When installing 32-bit dependent libraries in 64-bit Ubuntu, "libc6:i386 (!= 2.19-0ubuntu6.6) but 2.19...

- Popular science information on the entire process of chip design and production

- [Rivet RVB2601 Creative Application Development] 1. Routine Experience - Music Player

usb_host_device_code

usb_host_device_code Deep Learning Projects Using TensorFlow 2

Deep Learning Projects Using TensorFlow 2

京公网安备 11010802033920号

京公网安备 11010802033920号