"Open source" can mean many things in hardware design: open specifications, free designs, designs where patent/copyright protection has expired...

Therefore, the value of open source hardware varies. Many original open source hardware projects are small and have limited impact on the chip design business. Although RISC-V is not the first open source hardware project, it may be the largest in terms of fame and impact on the industry.

It can be said that RISC-V has changed the rules of the game.

Research on open source chips began as an academic project at the University of California, Berkeley, which produced the first reduced instruction set computer (RISC) CPU: RISC-1. One of the founders of the architecture was David Patterson, who wrote a seminal research paper on RISC. RISC-1 later became Sun Micro's SPARC processor. In the 1980s, RISC showed how viable companies could be built around a new processor architecture.

RISC-V was originally designed as a teaching and research tool. The instruction set design is clean, simple, and modern, without IP entanglements. The open approach allows researchers to build chips, extend the architecture, and explore new instructions. And it is also simple enough that graduate students can design it.

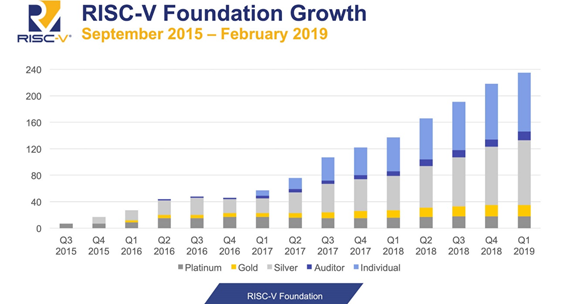

The university group put RISC in the public domain very loosely, which allowed others to start using it. As a result, an ecosystem of academics and researchers built up around RISC-V. The Berkeley team then formed a foundation to formalize the development and seek community participation. They introduced RISC to the public at the 2014 Hot Chips conference, when a desktop display was launched. Since then, the project has snowballed into an international movement.

Today, the foundation has been renamed RISC-V International and its headquarters has moved to Geneva, Switzerland, symbolizing a neutral position. Calista Redmond, CEO of RISC-V International, describes RISC-V as an open standard architecture. The organization also claims that no specific CPU is an open source design. Instead, it is an instruction set and behavioral specification that is developed to a certain point and then frozen.

RISC-V acts as a building block on which companies can add extensions. It's up to the implementer to release their CPU core as open source, charge for use of the core, or both.

The standard is open, but CPU designs based on it are not necessarily open or free. As an example of open design, Western Digital developed the SweRV core for use inside its flash array storage controllers. It then opened up the core sources.

Therefore, RISC-V offers low-cost entry, as well as a clearer architecture and more flexibility.

Although the RISC-V instruction set is fragmented, the basic architecture is sufficient for standardized software development. The instruction set can also benefit from broad community participation, with 50 committees working on various aspects of the design and ecosystem.

Another advantage of the RISC-V open specification is that it eliminates the need for architecture licensing, as users need to use arm or MIPS IP when designing their own CPU cores. Although arm does provide some free development cores, designers still have to use arm-designed cores and pay royalties. Most commercial chips still use licensed cores.

Even if designers are willing to license a pre-made CPU, they have more IP options.

For example, Taiwan's Andes Technology Corp. has developed RISC-V cores that are available for licensing. Some RISC pioneers formed SiFive to develop licensed, open source and customizable CPUs, although its business model is based on design services and providing IP with commercial features such as tracing, debugging and security options. Just like companies that profit from Linux distributions (including Red Hat and SUSE), design companies can also profit from RISC-V by providing customized and supported CPU IP.

Technological sovereignty

Technological sovereignty is another emerging IP issue, especially with the rise of the Tech Cold War. In the case of RISC-V, no single country controls the IP. Therefore, there is no way to prevent someone from using the instruction set simply based on a trade dispute.

Currently, the RISC-V ecosystem has also become a focus for other open source designs. For example, an organization called libreSoC is developing an open source GPU based on RISC-V. Its goal is to achieve a hybrid of CPU, VPU and GPU.

In fact, RISC-V is not the first open source hardware repository. Its predecessor was the Open Core website, which allowed developers to "view, download, reuse and share portal software designs." Projects included actual circuit designs, but most were obscure academic projects or discontinued IP known as "left-over-wear" or "abandoned ware." These cores lacked strong, scalable community support and could only be used as a reference by hobbyists and academics.

Other open CPU architectures include IBM Power and Sun Microsystems/Oracle SPARC.

The OpenSPARC project started in 2005. The site distributes RTL for the SPARC T1/T2 cores released under the GNU General Public License. They are small multi-threaded cores good for throughput computing.

Another was the LEON CPU core developed for the European Space Agency. The 32-bit SPARC V8 core was available under two different licenses. Once Oracle ended SPARC development, interest in the architecture waned.

In 2013, IBM founded the Open Power Foundation with partners Google, Tyan, Nvidia and Mellanox. The original goal was to provide an alternative to Intel's dominance in server and high-performance computing processors. But the project had a major limitation: IBM was initially the only supplier of power chips. Later, a Chinese company, Suzhou Hongxin, developed a power processor. When ARM servers and AMD Epyc processors entered the market to challenge Intel, interest in the project waned. Although progress has been slow, it continues.

In September 2020, IBM launched the A2O Power processor core, an out-of-order follow-up to the A2I core. A2O is a 64-bit CPU with significant single-threaded performance, a 4-GHz clock speed, and is based on a 7nm process. The OpenPOWER project has also promoted related interface standard projects such as OpenCAPI and OMI (Open Memory Interface). Currently, the A2O processor core has been open sourced as a POWER ISA core for embedded use in SoC designs. A2O has better single-threaded performance than its predecessor and supports 2-way SMT, PowerISA 2.07, and modular design.

On a 7nm process, IBM estimates that the A2O processor core will be able to run at 3.0GHz/0.25 Watts or 4.2GHz/0.85 Watts. However, this core was originally designed for a 45nm process and consumes 1.49 Watts at 2.30GHz.

Still, the impact of OpenSPARC and OpenPOWER was limited. Even with "open" access to the architecture, the original companies were slow to cede control to the design community. The OpenPOWER design was robust, but lacked a complete platform, such as a floating point unit. In addition, they were still highly dependent on IBM for support.

Recently, the Linux Foundation launched an initiative called the CHIPS Alliance to pave the way for an open source hardware ecosystem. The CHIPS Alliance refers to common hardware for interfaces, processors, and systems. In December, the CHIPS Alliance announced plans to join forces with RISC-V International to standardize an open, unified memory consistency bus for data-intensive applications.

Diversity

To succeed, open source IP needs a strong, diverse community support. It also requires an open ecosystem that values contributions to the architecture while providing a clearinghouse for new developments. In this way, open source IP projects can eventually compete with licensed cores and proprietary architectures.

The RISC-V project meets most of these requirements and has great promise. OpenPOWER also has potential but will require broader support to reach critical mass for market acceptance.

Still, the long-term success of RISC-V is not inevitable, and Arm, the world's leading IP provider, is not going away anytime soon. If Arm's acquisition by Nvidia passes antitrust review, Arm's business model could change significantly. But Nvidia has promised not to change Arm's business model.

It is still possible that ARM will adopt a hybrid IP licensing model, but expansion may be limited to large architecture licensees like Apple.

Meanwhile, RISC-V will continue to attract more investment and talent. The initial success of the open source architecture was primarily in microcontrollers. As its performance improves to the tiers of application and data center processors, it will have to compete with an entrenched and widespread ARM ecosystem.

Previous article:Renesas Launches Precision Clock Protocol Clock Manager Software to Improve Time Synchronization Accuracy

Next article:BlackBerry releases QNX Hypervisor 2.2, with richer features and greater flexibility

Recommended ReadingLatest update time:2024-11-23 07:28

- "Cross-chip" quantum entanglement helps build more powerful quantum computing capabilities

- Why is the vehicle operating system (Vehicle OS) becoming more and more important?

- Car Sensors - A detailed explanation of LiDAR

- Simple differences between automotive (ultrasonic, millimeter wave, laser) radars

- Comprehensive knowledge about automobile circuits

- Introduction of domestic automotive-grade bipolar latch Hall chip CHA44X

- Infineon Technologies and Magneti Marelli to Drive Regional Control Unit Innovation with AURIX™ TC4x MCU Family

- Power of E-band millimeter-wave radar

- Hardware design of power supply system for automobile controller

Professor at Beihang University, dedicated to promoting microcontrollers and embedded systems for over 20 years.

Professor at Beihang University, dedicated to promoting microcontrollers and embedded systems for over 20 years.

- Intel promotes AI with multi-dimensional efforts in technology, application, and ecology

- ChinaJoy Qualcomm Snapdragon Theme Pavilion takes you to experience the new changes in digital entertainment in the 5G era

- Infineon's latest generation IGBT technology platform enables precise control of speed and position

- Two test methods for LED lighting life

- Don't Let Lightning Induced Surges Scare You

- Application of brushless motor controller ML4425/4426

- Easy identification of LED power supply quality

- World's first integrated photovoltaic solar system completed in Israel

- Sliding window mean filter for avr microcontroller AD conversion

- What does call mean in the detailed explanation of ABB robot programming instructions?

- STMicroelectronics discloses its 2027-2028 financial model and path to achieve its 2030 goals

- 2024 China Automotive Charging and Battery Swapping Ecosystem Conference held in Taiyuan

- State-owned enterprises team up to invest in solid-state battery giant

- The evolution of electronic and electrical architecture is accelerating

- The first! National Automotive Chip Quality Inspection Center established

- BYD releases self-developed automotive chip using 4nm process, with a running score of up to 1.15 million

- GEODNET launches GEO-PULSE, a car GPS navigation device

- Should Chinese car companies develop their own high-computing chips?

- Infineon and Siemens combine embedded automotive software platform with microcontrollers to provide the necessary functions for next-generation SDVs

- Continental launches invisible biometric sensor display to monitor passengers' vital signs

- [Erha Image Recognition Artificial Intelligence Vision Sensor] 5. Erha Sensor Serial Port Communication Test

- EEWORLD University Hall----Live Replay: TI's Latest Application of Millimeter-Wave Radar in the Automotive Field

- 12~18GHz broadband power low noise solid state amplifier

- Changes in car rear lighting design

- A collection of essential basic knowledge for electronic engineers

- Last day! Live broadcast with prizes | RSL15 - ON Semiconductor's more efficient, smarter and safer BLE 5.2 Bluetooth chip

- Studying the road to electric motor driving-1

- TI blog post: The principle of BLDC square wave sensorless control using ADC sampling and integration

- EEWORLD University - Tektronix will teach you the oscilloscope usage skills you don't know

- LM2776 charge pump cannot start

Design of TurMass Wireless Data Transmission Unit Based on RISC-VSoC

Design of TurMass Wireless Data Transmission Unit Based on RISC-VSoC

京公网安备 11010802033920号

京公网安备 11010802033920号