Here, taking advantage of the FPGA’s flexible expansion, ability to realize system on chip (SoC), and availability of multiple IP cores, an intelligent sensor system capable of controlling multi-channel analog switches , A/D conversion, fast data processing and transmission, error correction, and temperature compensation is designed ; at the same time, the sensor is integrated with the data acquisition and processing control system , making the system more compact and improving the system’s ability to adapt to industrial sites.

1 System performance and components

1.1 Smart sensor system performance requirements

Sensor pressure measurement range: 0~5 MPa; system accuracy: ±0.1%FS; 1 channel analog voltage input (pressure signal) greater than 250 sampies/channel/s; serial RS 232C interface output.

1.2 Main components and performance of the system

Select devices based on the accuracy requirements of the system:

FPGA chip Altera 's CycloneⅡEP2C5 is selected , and its logic unit has 4608 LEs, 26 M4K RAM blocks, and 142 user I/O pins.

Pressure sensor Uses PDCR130W, pressure range 0~7 MPa, working voltage DC 10~30 VDC, output 0~10V, accuracy ±0.05%FS, operating temperature range -40~+125℃, temperature effect ±0.015%FS/℃.

Temperature sensor Uses high-precision integrated temperature sensor LM335 , with a sensitivity of 10 mV/K, an accuracy of 1°C, and a temperature range of -40~+100°C.

A/D converter Select the 12-bit A/D converter AD1* with built-in sample-and-hold function, with a conversion time of 10 μs, 0~10 V unipolar input or ±5 V bipolar input, and 12-bit parallel output.

Multi-channel analog switch A four-to-one multi-channel analog switch AD7502 is used , and its pin is set to the enable signal EN=1; the A1A0 pin is the channel selection signal.

The output level conversion interface system uses the MAX232 chip to complete the conversion between TTL and RS 232C levels.

2 System error correction method

2.1 Correction Methods for Zero Drift and Gain Error

In the smart meter , the error correction formula of the error model is:

Where: b1 and b0 are error correction factors. The error correction circuit model is shown in Figure 1, where x is the measured signal; y is the system output; ε, k, i are unknown quantities that affect the system.

The error correction process is:

When S1 is closed, x=0, and according to the error correction formula, equation (2) is obtained for system zero point calibration;

When S2 is closed, x = E (standard voltage), and formula (3) is obtained for system gain error correction;

Combining equations (2) and (3), we can get the error correction factor:

When actual measurement is performed, S3 is closed, and the corrected output signal y can be obtained by using the calculated error correction factor and the error correction formula (1). function ImgZoom (Id) // Reset the image size to prevent the table from breaking { var w = $ (Id). width; var m = 650; if (w

2.2 Sensor temperature compensation method

For pressure sensors , the ambient temperature has a great influence on their measurement results. In order to eliminate the error caused by temperature, the sensor signal needs to be temperature compensated. The sensor temperature is compensated by measuring the working temperature of the sensor. The temperature error correction model of the sensor is:

In the formula: y is the measured value; yc is the measured value after temperature compensation; △φ is the difference between the actual working temperature of the sensor and the standard measurement temperature; a0 is the sensor scale change coefficient caused by the correction temperature change, and a1 is the sensor zero drift change coefficient caused by the correction temperature. These two coefficients reflect the temperature characteristics of the sensor.

2.3 Random error elimination method

The system uses arithmetic mean digital filtering method to eliminate the random error of the system. By taking the arithmetic mean of N consecutive sampling values, the mathematical expression is:

Suitable for filtering signals with random interference.

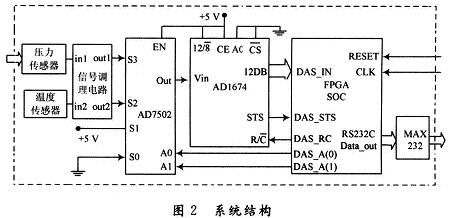

System hardware structure design

According to the error correction and temperature compensation method of the system, the hardware connection structure of the system is shown in Figure 2. In Figure 2, the four input channels of the analog multiplexer AD7502 are: A1A0=00, S0 is selected, and the S0 channel is grounded for zero drift calibration; A1A0=01, S1 is selected, and the S1 channel is connected to +5 V (50% of the maximum input voltage of AD1674 ) for gain error correction; A1A0=10, S2 is selected, and the S2 channel is connected to the temperature measurement signal for temperature compensation of the sensor; A1A0=11, S3 is selected, and the S3 channel is connected to the pressure measurement signal. The channel selection signals A0 and A1 are controlled by the DAS_A0 and DAS_A1 pins in the FPGA chip.

The A/D converter AD1674 in the system adopts independent working mode, and its control pins are set as follows: CE and 12/8 are connected to high level; CS and A0 are connected to low level. At this time, AD1674 is set to 12-bit A/D conversion and 12-bit data output, and its conversion is completely controlled by R/C, as shown in Figure 2. When R/C=0, the 12-bit A/D conversion is started; when the A/D conversion is completed, the status signal STS=0, otherwise STS=1; when R/C=1, the 12-bit A/D conversion data is read. The R/C signal is controlled by the DAS_RC of the FPGA chip. The entire system is controlled by a system-on-chip (SoC) based on FPGA. Among them, the DAS_STS, DAS_RC, DAS_IN, and DAS_A pins in the FPGA chip are user-customized logic, that is, the external interface of the DAS control unit , which is used to control the working timing conversion of AD1674 and the channel selection of AD7502.

3.1 Implementation of SoC Structure

SoPC design consists of components such as CPU , memory interface, standard peripherals and user-customized logic unit modules. Altera's SoPCBuilder tool provides a large number of IP cores for calling, which can easily configure embedded NoisⅡ processor soft core, on-chip RAM and RS 232 controller, extended off-chip memory, user-customized logic units on a single FPGA chip, and automatically assign addresses to each peripheral of the system, connect the system bus , and determine the device priority. Its internal structure is shown in Figure 3.

function ImgZoom(Id) // Resize the image to prevent it from breaking the table { var w = $(Id).width; var m = 650; if (w

3.2 Implementation of data acquisition control unit

The data acquisition system (DAS) control unit is the core of the whole system. Its input ports and functions are as follows: DAS_STS is used to receive the STS status signal of AD1674; DAS_IN (12 bits) is used to receive the parallel 12-bit conversion output of AD1674; CLK, RST are used as system clock and RESET signals. The output port DAS_RC is connected to the R/C terminal of AD1674 to control the start and reading of the A/D converter; DAS_A is used to control the A1A0 channel selection signal of AD7502; DAS_OUT (the number of the channel is 16 bits) is used as the 16-bit output data of the DAS control unit.

The finite state machine (FSM) of the DAS control unit has 4 states, namely St0, St1, St2, and St3. St0 is to select the channel, start the A/D conversion, and enter the St1 state; St1 is to wait for the conversion to end. If the conversion is completed, it will enter the St2 state, otherwise it will remain in the St1 state; St2 is to send a read data signal and enter the St3 state; St3 is to output the conversion data; select other channels and return to the St0 state. The DAS control unit is developed using the VHDL language, and part of the program code is shown below:

The simulation of the DAS control unit is shown in Figure 4. The figure shows that the control unit operates correctly.

3.3 Smart sensor system software workflow

The error correction and temperature compensation in the system are completed by the system software control. The system software is developed by the software development tool (SDK) in the SoPC Builder tool . The system software flow is shown in Figure 5.

The system is initialized and the DAS control unit is started after power-on. Each channel is selected and the random error of each channel is eliminated. Then, the error correction factor is calculated in real time based on the corrected values of channel 0 and channel 1. The zero drift calibration and gain error are corrected in real time according to the error correction formula (1). Then, the operating temperature of the sensor is obtained based on the measurement, and the difference with the standard temperature is calculated. The temperature variation coefficient of the sensor is obtained by looking up the table. Finally, the measured pressure data is corrected according to the temperature compensation formula (5) and the data is output.

4 Conclusion

In the process of system design, we make full use of the characteristics of FPGA construction system flexibility and the combination of software and hardware development. On the basis of meeting the system performance, we reasonably allocate the software and hardware functions and simplify the system design. FPGA puts the system that was previously implemented by discrete chips into a single chip. This single-chip system design greatly improves the stability and reliability of the system, and at the same time improves the system's ability to resist industrial site interference.

Previous article:Design of Elevator Controller System Based on FPGA

Next article:Implementation of VLIW Microprocessor Based on FPGA

Recommended ReadingLatest update time:2024-11-17 02:58

- Popular Resources

- Popular amplifiers

-

Analysis and Implementation of MAC Protocol for Wireless Sensor Networks (by Yang Zhijun, Xie Xianjie, and Ding Hongwei)

Analysis and Implementation of MAC Protocol for Wireless Sensor Networks (by Yang Zhijun, Xie Xianjie, and Ding Hongwei) -

MATLAB and FPGA implementation of wireless communication

MATLAB and FPGA implementation of wireless communication -

Intelligent computing systems (Chen Yunji, Li Ling, Li Wei, Guo Qi, Du Zidong)

Intelligent computing systems (Chen Yunji, Li Ling, Li Wei, Guo Qi, Du Zidong) -

Summary of non-synthesizable statements in FPGA

Summary of non-synthesizable statements in FPGA

- Huawei's Strategic Department Director Gai Gang: The cumulative installed base of open source Euler operating system exceeds 10 million sets

- Analysis of the application of several common contact parts in high-voltage connectors of new energy vehicles

- Wiring harness durability test and contact voltage drop test method

- Sn-doped CuO nanostructure-based ethanol gas sensor for real-time drunk driving detection in vehicles

- Design considerations for automotive battery wiring harness

- Do you know all the various motors commonly used in automotive electronics?

- What are the functions of the Internet of Vehicles? What are the uses and benefits of the Internet of Vehicles?

- Power Inverter - A critical safety system for electric vehicles

- Analysis of the information security mechanism of AUTOSAR, the automotive embedded software framework

Professor at Beihang University, dedicated to promoting microcontrollers and embedded systems for over 20 years.

Professor at Beihang University, dedicated to promoting microcontrollers and embedded systems for over 20 years.

- Innolux's intelligent steer-by-wire solution makes cars smarter and safer

- 8051 MCU - Parity Check

- How to efficiently balance the sensitivity of tactile sensing interfaces

- What should I do if the servo motor shakes? What causes the servo motor to shake quickly?

- 【Brushless Motor】Analysis of three-phase BLDC motor and sharing of two popular development boards

- Midea Industrial Technology's subsidiaries Clou Electronics and Hekang New Energy jointly appeared at the Munich Battery Energy Storage Exhibition and Solar Energy Exhibition

- Guoxin Sichen | Application of ferroelectric memory PB85RS2MC in power battery management, with a capacity of 2M

- Analysis of common faults of frequency converter

- In a head-on competition with Qualcomm, what kind of cockpit products has Intel come up with?

- Dalian Rongke's all-vanadium liquid flow battery energy storage equipment industrialization project has entered the sprint stage before production

- Allegro MicroSystems Introduces Advanced Magnetic and Inductive Position Sensing Solutions at Electronica 2024

- Car key in the left hand, liveness detection radar in the right hand, UWB is imperative for cars!

- After a decade of rapid development, domestic CIS has entered the market

- Aegis Dagger Battery + Thor EM-i Super Hybrid, Geely New Energy has thrown out two "king bombs"

- A brief discussion on functional safety - fault, error, and failure

- In the smart car 2.0 cycle, these core industry chains are facing major opportunities!

- Rambus Launches Industry's First HBM 4 Controller IP: What Are the Technical Details Behind It?

- The United States and Japan are developing new batteries. CATL faces challenges? How should China's new energy battery industry respond?

- Murata launches high-precision 6-axis inertial sensor for automobiles

- Ford patents pre-charge alarm to help save costs and respond to emergencies

- [Program source code] Freescale MAPS-K64 development board program example

- Award-winning online seminar | The industry's most powerful MPS multi-phase controller power solution helps the Internet/IoT take off

- The value of the second brother has increased. How to raise pigs scientifically and build an injectable radio tracking system

- MicroPython upgraded to v1.12

- I would like to ask, how is the transformer in a single-tube transformer-coupled amplifier magnetically reset?

- Sensor materials for learning at home: the hottest collection of EE sensor materials

- [RVB2601 Creative Application Development] Unboxing

- A brief description of the stack structure in the ZigBee standard

- Guess: What is the origin of the code name of the open source "Wanli" Raspberry Pi car that went viral yesterday?

- E103-W01-BF Unboxing and Brief Introduction

Analysis and Implementation of MAC Protocol for Wireless Sensor Networks (by Yang Zhijun, Xie Xianjie, and Ding Hongwei)

Analysis and Implementation of MAC Protocol for Wireless Sensor Networks (by Yang Zhijun, Xie Xianjie, and Ding Hongwei)

京公网安备 11010802033920号

京公网安备 11010802033920号