|

Direct digital synthesizer is a new frequency synthesis technology using digital technology. It generates signals of various frequencies by controlling the step size of frequency and phase increments. It has a series of advantages; high frequency resolution; it can achieve fast frequency switching; it can maintain phase continuity when the frequency changes; it is easy to realize numerical control modulation of frequency, phase and amplitude, etc. Currently, DDS can be implemented using dedicated chips or programmable logic chips [1]. The signal waveforms, functions and control methods generated by dedicated DDS chips are fixed and often cannot meet specific needs [2]. Programmable logic devices have the characteristics of large device scale, fast working speed and programmable hardware. They have a short development cycle and are easy to upgrade, so they are very suitable for implementing DDS. 1 How DDS works The structural principle diagram of DDS is shown in Figure 1. DDS uses a numerically controlled oscillator to generate sine waves with controllable frequency, phase and amplitude [3]. The circuit includes a phase accumulator, phase modulator, sinusoidal ROM lookup table, reference clock source, D/A converter, etc. The first three are the digital parts in the DDS structure and have the function of numerically controlled frequency synthesis.

| |||

| The core of the DDS system is the phase accumulator, which completes the phase accumulation process. Under the control of the reference clock, the frequency control word is accumulated by the accumulator to obtain the corresponding phase data. The phase modulator receives the phase output of the phase accumulator and is mainly used for phase modulation of the signal. The output data is used as a sampling address to find Address the sine ROM lookup table to complete the phase-amplitude conversion and output different amplitude codes; then pass through the D/A converter to obtain the corresponding staircase wave; finally, smooth the staircase through the low-pass filter to obtain the frequency control word Determined by the continuous transformation of the output sine wave.

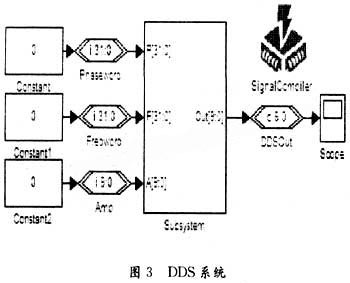

2 Design based on DSP Builder and DDS 2.1 Introduction to DSP Builder DSP Builder is a system-level tool for DSP development launched by Altera Corporation in the United States. As a Simulink toolbox of Matlab, it allows the design of DSP systems using FPGA to be completely modeled and system-level simulated through the Simulink graphical interface. The design model can Directly convert to VHDL hardware description language, and automatically call EDA design software such as Quartus II to complete synthesis, netlist generation, device adaptation and even FPGA configuration download, making the system description and hardware implementation organically integrated into one, fully embodying the modern electronics Characteristics and advantages of technical automation development. 2.2 DSP Builder design principle and parameter settings The DDS system based on DSP Builder is shown in Figure 2 and Figure 3. The DDS subsystem Subsystem has three inputs, namely Freqword (32-bit frequency control word), Phaseword (32-bit phase control word), and Amp (10-bit amplitude control word); one output, the 10-bit DDSOut output. The two Parallel Adder Subtractors are phase accumulator and phase modulator respectively, and the LUT is a sinusoidal ROM lookup table. Set the simulation stop time of Simulink to 5 and the simulation step Fixed Step Size to le-3. Figure (4) corresponds to the output waveform of the DDS system when the frequency, phase and amplitude control words are 4000000, 0 and 10 (parameter 1) respectively. Figure 5 corresponds to the frequency, phase and amplitude control words are 9000000, 500000000 and 15 (parameter 2) respectively. ) is the output waveform of the DDS system.

3.1 FPGA implementation of DDS Matlab/Simulink compiles the designed DDS system, and can directly generate QuartusⅡ project files by calling the SignalCompiler tool of DSP Builder, and then calls QuartusⅡ to complete synthesis, netlist generation and adaptation, until the FPGA configuration download process is completed.

Use QuartusⅡ to simulate the project files generated by DSP builder. For the DDS system with different parameter settings, the simulation waveforms are shown in Figure 6 and Figure 7.

4 Conclusion The method of using programmable logic chips to design DDS is usually to use a combination of VHDL language input and schematic diagram method to design the entire signal generation circuit. This method usually requires the use of many modules, is highly comprehensive, and has high requirements for designers. This article uses DSP Builder, the interface tool between QuartusⅡ and Matlab/Simulink, to design the entire DDS system. DSP Builder has a friendly development environment, is highly interactive with QuartusⅡ, and is easy to use. Designers only need to briefly understand the VHDL description language to directly call the established Matlab and Simulink design processes, conduct modeling and system-level simulation through the Simulink graphical interface, and then call Quartus II for synthesis, netlist generation and Adaptation, and finally completes the configuration download process to the FPGA. The entire design idea is flexible, the graphical interface is simple and intuitive, and the development cycle is short. The simulation results show that the design scheme is correct in principle and effective. Using FPGA to implement DDS is more flexible than a dedicated DDS chip. As long as the data and control parameters in the ROM in the FPGA are changed, DDS can generate arbitrary modulation waveforms with high resolution and considerable flexibility. Embedding DDS design into a system composed of FPGA chips will not increase the system cost much, while the price of purchasing dedicated chips is many times that of the former. Therefore, using FPGA to design a DDS system is very cost-effective. |

Previous article:A DSP-based software phase-locked loop model and implementation

Next article:DDS design based on DSP Builder and its FPGA implementation

- Huawei's Strategic Department Director Gai Gang: The cumulative installed base of open source Euler operating system exceeds 10 million sets

- Analysis of the application of several common contact parts in high-voltage connectors of new energy vehicles

- Wiring harness durability test and contact voltage drop test method

- Sn-doped CuO nanostructure-based ethanol gas sensor for real-time drunk driving detection in vehicles

- Design considerations for automotive battery wiring harness

- Do you know all the various motors commonly used in automotive electronics?

- What are the functions of the Internet of Vehicles? What are the uses and benefits of the Internet of Vehicles?

- Power Inverter - A critical safety system for electric vehicles

- Analysis of the information security mechanism of AUTOSAR, the automotive embedded software framework

Professor at Beihang University, dedicated to promoting microcontrollers and embedded systems for over 20 years.

Professor at Beihang University, dedicated to promoting microcontrollers and embedded systems for over 20 years.

- Innolux's intelligent steer-by-wire solution makes cars smarter and safer

- 8051 MCU - Parity Check

- How to efficiently balance the sensitivity of tactile sensing interfaces

- What should I do if the servo motor shakes? What causes the servo motor to shake quickly?

- 【Brushless Motor】Analysis of three-phase BLDC motor and sharing of two popular development boards

- Midea Industrial Technology's subsidiaries Clou Electronics and Hekang New Energy jointly appeared at the Munich Battery Energy Storage Exhibition and Solar Energy Exhibition

- Guoxin Sichen | Application of ferroelectric memory PB85RS2MC in power battery management, with a capacity of 2M

- Analysis of common faults of frequency converter

- In a head-on competition with Qualcomm, what kind of cockpit products has Intel come up with?

- Dalian Rongke's all-vanadium liquid flow battery energy storage equipment industrialization project has entered the sprint stage before production

- Allegro MicroSystems Introduces Advanced Magnetic and Inductive Position Sensing Solutions at Electronica 2024

- Car key in the left hand, liveness detection radar in the right hand, UWB is imperative for cars!

- After a decade of rapid development, domestic CIS has entered the market

- Aegis Dagger Battery + Thor EM-i Super Hybrid, Geely New Energy has thrown out two "king bombs"

- A brief discussion on functional safety - fault, error, and failure

- In the smart car 2.0 cycle, these core industry chains are facing major opportunities!

- The United States and Japan are developing new batteries. CATL faces challenges? How should China's new energy battery industry respond?

- Murata launches high-precision 6-axis inertial sensor for automobiles

- Ford patents pre-charge alarm to help save costs and respond to emergencies

- New real-time microcontroller system from Texas Instruments enables smarter processing in automotive and industrial applications

- Domestic MCU

- STM32F767 ADC self-calibration problem

- EEWORLD University ---- Digi-Key: Accelerated Application of Graph Algorithms in Deep Learning

- Echo Cancellation - How to solve the serious problem of sound swallowing during dual talk in WebRTC AEC algorithm

- [TI millimeter wave radar evaluation]_2_1243Problems encountered in BOOST debugging

- FPGA Timing Constraints Practice: Sorting Out the Clock Tree

- A constant and adjustable output power electronic cigarette power supply solution based on TPS61022

- Sales of new energy vehicles have skyrocketed, how should we deal with used batteries?

- E-ON China Online Cloud Sharing Laboratory——"Microcomputer Principles and Applications"

- Improving Power Supply Network Efficiency Using Fixed Ratio Converters

Dual Radar: A Dual 4D Radar Multimodal Dataset for Autonomous Driving

Dual Radar: A Dual 4D Radar Multimodal Dataset for Autonomous Driving Digilent Vivado library

Digilent Vivado library

京公网安备 11010802033920号

京公网安备 11010802033920号