With the development of large-scale integrated circuits and high-speed digital signal processors, signal processing in the communications field is increasingly implemented in the digital domain. Software phase locking technology is a research . The phase-locked technology used in software radio receivers is based on the implementation of digital signal processing technology on general programmable . Since the functions of this type of phase-locked loop are mainly implemented through software programming, it can be called It is a software phase-locked loop ( software PLL) [1] .

Although the basic algorithm idea used by software phase-locked loops has not changed much compared with analog phase-locked loops and digital phase-locked loops, their implementation methods are completely different. This article will establish the Z-domain model of the software phase-locked loop and analyze the delay estimation , acquisition speed and software phase-locked loop model issues under multi-rate conditions in the software phase-locked loop [1] .

1 Basic model of software phase-locked loop

Based on the analog phase-locked loop, the Z-domain model of the software phase-locked loop is established using the connection between digital and analog systems, taking the second-order type-2 phase-locked loop as an example. Literature [2] gives the basic model and principle of phase-locked loop in detail.

If the basic components of the phase-locked loop are implemented in the form of software programming, the basic components of the software phase-locked loop can be obtained, as shown in Figure 1.

Firstly, starting from the S-domain model of the analog phase-locked loop, the Z-domain model of the software phase-locked loop is obtained (for the S-domain model please refer to the literature [ 2]). Since bilinear transformation is an important method to connect analog systems and digital systems, with the characteristics of simple transformation and clear expressions [ 3] , this paper chooses the bilinear transformation method as one of the two methods between analog phase-locked loopsbasis for conversion.

Equation (1) is the complex frequency domain expression of the bilinear transformation method:

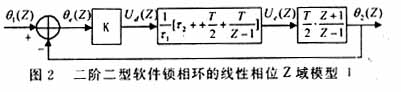

where: T is the sampling time interval connecting the digital system and the analog system, and 1/T represents the sampling frequency. According to this conversion relationship , the digital complex frequency domain expressions corresponding to each part of the S domain model are converted, and the complex frequency domain model shown in Figure 2 can be obtained.

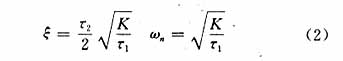

In practical applications, second-order linear systems are often described by the damping factor ξ and the undamped oscillation frequency ω n . In the second-order type-2 phase- locked loop, the corresponding relationship between τ 1 , τ 2 , K and ξ, ω n

is as follows: On the basis of equation (1) and equation (2), perform equivalent transformation on Figure 2, Another linear phase Z-domain model , as shown in Figure 3.

In model I, the parameters τ 1 , τ 2 and K are closely related to the resistors, capacitors and voltage-controlled oscillators that implement the circuit function . The software phase-locked function is realized by multipliers, adders and registers, so it is more practical to use Model II to characterize the linear phase Z-domain model of the software phase-locked loop.

2 Mathematical model of software phase-locked loop

The Z-domain model of the digital phase detector is as follows:

One of the methods to realize the digital phase detector is to use the orthogonal decomposition of the signal. Figure 4 is the principle block diagram of this method.

Among them: LPF represents low-pass filtering, and A is the constant gain brought by the low-pass filter. Therefore, the output of the phase detector:

After inverse Z transformation, the time domain expression of the digital loop filter is obtained:

Through inverse Z transformation, the time domain expression of the numerically controlled oscillator is obtained:

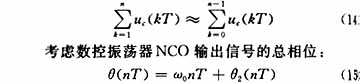

The variable u c (nT) has a small value and does not change will be too fast, so Equation (14) is established:

Combining Equation (11), Equation (12) and Equation (13), the expression of the NCO output signal is obtained: If the

numerically controlled oscillator is described in terms of digital frequency, it is called its digital center The frequency is ω 0 T and the digital offset frequency is ω n 2 ·u c (nT) ·T. Therefore, the sensitivity and digital sensitivity of the numerically controlled oscillator are ·T respectively . 3 Software phase-locked loop under multi-rate conditions In digital receivers, sampling rate conversion problems under multi-rate conditions are often encountered. The so-called multi-rate system refers to the existence of 2 or more sampling rates in a digital system [4] . The mixers that make up the software phase-locked loop phase detector usually work at the system sampling frequency. Under the premise of satisfying the Nyquist sampling law, the system sampling rate of a digital receiver is generally as high as several 10 M. As for the arctangent table that is part of the digital phase detector, since the data after mixing has been extracted multiple times, the operating frequency has dropped to a level similar to the signal baud rate. Data extraction also reduces the computational complexity of the DSP. The processing speed of the loop filtering completed is approximately equal to the signal baud rate. In addition, since the numerically controlled oscillator in the software phase-locked loop needs to provide the mixer with the same rate of orthogonal carrier, its operating rate is equal to that of the mixer, and interpolation is required to adjust the rate. In order to make reasonable use of the limited computing resources of the DSP, the working rate of the loop filter is always reduced as much as possible while meeting the synchronization needs , which is commonly referred to as the loop frequency. The loop frequency is an important parameter of the software phase-locked loop. It also determines the calculation amount and acquisition speed of the phase-locked loop algorithm. If the loop frequency is too high, it will bring additional computational burden. If the loop frequency is too low, it cannot meet the needs of capture speed. In applications, the system baud rate is usually used as the loop frequency. The linear phase Z-domain model corresponding to this extended model is shown in Figure 5. ![]()

Among them: D represents data extraction, and I represents data interpolation. Anti-aliasing filtering must be performed before data is extracted. FIR filters that can be used for anti-aliasing filtering include CIC filters, half-band filters, etc.

In practical situations, zero-order preserving interpolation requires almost no additional computation, so it is often used. In fact, the loop frequency f L can always keep up with the rate of change of the loop filter output signal. In other words, sampling the loop filter output signal at a rate of f L retains all its information, so zero-order maintaining interpolation will not have much [ 4] .

Combined with the basic principles of the software phase-locked loop mentioned above, let's use Matlab simulation to observe the system response of the software phase-locked loop. This article uses the frequency step signal as input to observe the system response of the software phase-locked loop to further verify a series of software phase-locked loop models established in this article.

The system sampling frequency is set to 1 MHz, the simulation time is 0.1 s, the signal center frequency is 125 kHz, the starting phase is -π/4, the input frequency step is 100 Hz, the starting point is 0.02 s, and the decimation factor is 8. Under normal circumstances, it is expected that the loop works in an under- damped state, and the damping factor ξ =0.707 is taken. ω n is determined by 2πΔF (fast capture bandwidth) [2] , and is taken as 2π*40, 2π*50, and 2π*100 respectively . The phase error response curve, NCO bias frequency curve and phase curve of the frequency step signal are simulated, as shown in Figure 6.

It can be seen from Figure 6 that the phase error of the software phase-locked loop is 0 in the interval [0, 0.02] and is in a locked state. At t=0.02 s, the input signal frequency produces a step of 100 Hz, causing the software phase-locked loop to enter the acquisition process. Due to the correction effect of the software phase-locked loop, when ω n =2π*50, the system re-enters the synchronization state at t=0.05 s, and the phase error is still 0. It can be seen from the phase error response curve that the phase-locked loop can track the frequency . It also shows that although the phase-locked loop phase detection error is 0, its output The signal is not 0, and the 100 Hz bias frequency generated by this control signal ensures that the NCO output is synchronized with the input signal. When the fast capture bandwidth changes, the capture speed of the phase-locked loop also changes. The wider the fast capture bandwidth, the faster the capture speed.

4 DSP implementation of software phase-locked loop

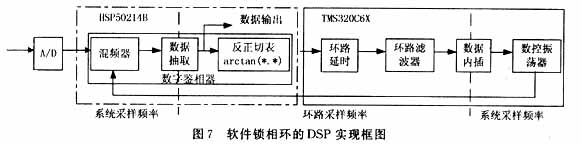

In the implementation of wideband digital receiver, the universal programmable down-converter HSP50214B is used for digital down-conversion. In the entire feedback loop that implements carrier synchronization and symbol synchronization software phase-locked loop, the numerically controlled oscillator and phase detector are completed by HSP50214B, and the loop filtering is completed in TMS320C6X. The DSP implementation block diagram is shown in Figure 7.

Loop delay is a factor that should be taken seriously. There are two main reasons for software phase-locked loop loop delay:

(1) Delay caused by the FIR filter in the loop;

(2) Additional delay caused by data waiting for processing.

In a digital receiver, two levels of coarse synchronization and fine synchronization are used. The coarse synchronization loop has a large delay and a slow response speed; the fine synchronization loop has a small delay and a fast response speed. Coarse synchronization ensures that the effective signal falls within the passband of the filter. Fine synchronization can obtain greater accuracy based on coarse synchronization. Capture belt and timing belt. In addition, several sampling points are discarded to eliminate unnecessary loop delays.

It can be seen that the software phase-locked loop has the advantage of flexible processing. It gets rid of complex hardware circuit design and solves many problems encountered in analog loops. At present, as DSP functions become more and more powerful and the working speed becomes higher and higher, necessary conditions are created for the development of software phase locking technology.

references

[1]Best RLPhase locked loops design simulation and application [M]. 3rd EditionMcGraw Hill, 1997

[2]Zhang JueshengPhase locked technology[M]. Xi’an: Xi’an University of Electronic Science and Technology Press, 1994

[3 ] Ding Yumei Digital Signal Processing [M]. Xi'an: Xi'an University of Electronic Science and Technology Press, 1995 [

4 ] Zong Kongde Multiple Sampling Rate Signal Processing [M]. Beijing Tsinghua University Press, 1996

[ 5] HARRIS Company, The principle and application of HSP50214B

[6]John Proakis GDigital communications[M]. Beijing: Electronic Industry Press , 1999

Previous article:The voltage space vector pulse width modulation wave is generated by the DSP chip

Next article:DDS design based on DSP Builder and its FPGA implementation

- Popular Resources

- Popular amplifiers

- Huawei's Strategic Department Director Gai Gang: The cumulative installed base of open source Euler operating system exceeds 10 million sets

- Analysis of the application of several common contact parts in high-voltage connectors of new energy vehicles

- Wiring harness durability test and contact voltage drop test method

- Sn-doped CuO nanostructure-based ethanol gas sensor for real-time drunk driving detection in vehicles

- Design considerations for automotive battery wiring harness

- Do you know all the various motors commonly used in automotive electronics?

- What are the functions of the Internet of Vehicles? What are the uses and benefits of the Internet of Vehicles?

- Power Inverter - A critical safety system for electric vehicles

- Analysis of the information security mechanism of AUTOSAR, the automotive embedded software framework

Professor at Beihang University, dedicated to promoting microcontrollers and embedded systems for over 20 years.

Professor at Beihang University, dedicated to promoting microcontrollers and embedded systems for over 20 years.

- Innolux's intelligent steer-by-wire solution makes cars smarter and safer

- 8051 MCU - Parity Check

- How to efficiently balance the sensitivity of tactile sensing interfaces

- What should I do if the servo motor shakes? What causes the servo motor to shake quickly?

- 【Brushless Motor】Analysis of three-phase BLDC motor and sharing of two popular development boards

- Midea Industrial Technology's subsidiaries Clou Electronics and Hekang New Energy jointly appeared at the Munich Battery Energy Storage Exhibition and Solar Energy Exhibition

- Guoxin Sichen | Application of ferroelectric memory PB85RS2MC in power battery management, with a capacity of 2M

- Analysis of common faults of frequency converter

- In a head-on competition with Qualcomm, what kind of cockpit products has Intel come up with?

- Dalian Rongke's all-vanadium liquid flow battery energy storage equipment industrialization project has entered the sprint stage before production

- Allegro MicroSystems Introduces Advanced Magnetic and Inductive Position Sensing Solutions at Electronica 2024

- Car key in the left hand, liveness detection radar in the right hand, UWB is imperative for cars!

- After a decade of rapid development, domestic CIS has entered the market

- Aegis Dagger Battery + Thor EM-i Super Hybrid, Geely New Energy has thrown out two "king bombs"

- A brief discussion on functional safety - fault, error, and failure

- In the smart car 2.0 cycle, these core industry chains are facing major opportunities!

- The United States and Japan are developing new batteries. CATL faces challenges? How should China's new energy battery industry respond?

- Murata launches high-precision 6-axis inertial sensor for automobiles

- Ford patents pre-charge alarm to help save costs and respond to emergencies

- New real-time microcontroller system from Texas Instruments enables smarter processing in automotive and industrial applications

- Low-cost intelligent fire and burglar alarm system based on single chip microcomputer

- Share negative pressure power supply design

- The role and principle analysis of single chip microcomputer crystal oscillator

- Application of Finite State Machine in Embedded Software

- [Goodbye 2021, Hello 2022] Repairing the plank road in the open, crossing the Chen Cang in secret

- 4-bit flashing light based on FPGA-simple design method

- I was cheated! How much profit can I get from this USB microphone?

- Conversion between CAD, word, and excel?

- STM32MP157A-DK1 Discovery Kit

- Magnetic field data collected by the LIS2DML array board

Dual Radar: A Dual 4D Radar Multimodal Dataset for Autonomous Driving

Dual Radar: A Dual 4D Radar Multimodal Dataset for Autonomous Driving CVPR 2023 Paper Summary: Transparency, Fairness, Accountability, Privacy, Ethics in Vision

CVPR 2023 Paper Summary: Transparency, Fairness, Accountability, Privacy, Ethics in Vision

京公网安备 11010802033920号

京公网安备 11010802033920号