Distributed amplifiers can provide a wide frequency range and high gain. For a period of time, their design usually used transmission lines as input and output matching circuits. With the development and maturity of gallium arsenide (GaAs) microwave monolithic integrated circuits, many types of amplifier circuits have been proposed to improve efficiency, output power, and reduce noise figure, but distributed amplifiers are still the mainstream design for broadband circuits (such as optical communication circuits). Understanding the design of gallium arsenide microwave monolithic integrated circuit GaAs MMIC distributed amplifiers will be of great help to many broadband circuit applications.

Johns Hopkins University has offered a MMIC design course since 198? and has students tape out on TriQuint's production line. A distributed amplifier designed by Craig Moore (who served as a teaching assistant for the course from 198? to 2003) is a classic design example for the course. The design even went through low-temperature environment experiments and showed a lower noise figure at low temperatures of liquid nitrogen. The amplifier uses TriQuint's 0.5μm GaAs MESFET process, and its gain is slightly lower than the new circuit based on 0.5μm GaAs pseudo high electron mobility transistor PHEMT. The new version of the 0.5μm GaAs PHEMT distributed amplifier and some other circuits are used as examples in the new course in 2006. This article will introduce

the design method of

the broadband amplifier

and the results of simulation and actual measurement.

Figure 1: Block diagram of a distributed amplifier circuit using microstrip transmission lines.

Distributed amplifiers use broadband transmission lines to inject input signals into a group of active devices (as shown in Figure 1), while another parallel transmission line is used to collect the output signals of each active device and add them together. Each stage provides equivalent gain, but the gain is distributed over a wide frequency range. Compared with cascaded designs, the total gain is the sum of the gains of each stage, rather than the product of the gains of each stage. However, when lumped parameter elements are used to approximate distributed transmission lines (as shown in Figure 2), the shunt capacitance of the lumped parameter transmission line to ground is replaced by the parasitic capacitance of the transistor. The equivalent transmission line of the lumped parameter element acts as a low-pass filter, and its cutoff frequency is inversely proportional to the parasitic capacitance of the transistor. Therefore, the size of the transistor directly determines the upper limit of the operating frequency of the circuit. The various parameters that must be considered in the design include: the number of amplifier stages, the size of the active device, the process type of the device (if there are multiple types), and the DC bias of each stage. More stages means a larger gain-bandwidth product, but it also introduces greater power consumption. Once the size of the transistor is determined, simulation software can be used to optimize various parameters such as gain, reflection coefficient, output power, and noise figure.

Figure 2: Block diagram of a distributed amplifier circuit using lumped element components (where CGS and CDS represent gate capacitance and drain capacitance, respectively).

Since distributed amplifiers have many applications, the requirements for various performance indicators are very flexible, and broadband gain is one of the most important indicators. In the design example of Craig Moore, an enhancement-type PHEMT device is used because the enhancement-type device only needs a set of positive voltage power supply. In order to provide the same performance as the circuit of the 0.5μm GaAs MESFET process adopted by TriQuint Semiconductor in 198?, the design adopts the 0.5μm GaAs PHEMT process and uses a 3-level transistor amplification topology. In order to adapt to battery-powered applications, 3.3V voltage is selected. Of course, in order to meet different customer needs, the operating voltage and current can be easily adjusted in a large range. Under the power supply of 1.5V and 14mA, the simulation results show that only 2dB gain is lost, and the performance changes are also small when the gate voltage changes from 1.5V to 5.0V and the drain current changes between 14~35mA. In order to achieve the best gain and matching performance, Agilent's computer-aided engineering software ADS is used for linear simulation to determine the appropriate inductance value and PHEMT size.

Figure 3: Simulation results of matching, gain, noise figure, and stability factor of the PHEMT distributed amplifier.

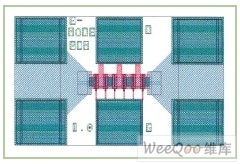

Through ideal simulation calculations, the design uses a 6×30μm enhanced PHEMT device. Craig Moore's 198? design adds some additional matching components to the drain of the MESFET tube to ensure that the effective output capacitance is the same as the gate input capacitance. At this time, the input and output lumped parameter transmission lines will be symmetrical, and their phase delays will be the same. The article also compares this input and output transmission line symmetric matching scheme with another scheme where the drain capacitance is independently optimized (the drain inductance and gate are asymmetric). For this simple 3-level PHEMT design, the phase shift difference between the gate and drain input lines is very small, so a simpler asymmetric scheme is used here. If the phase difference between the input and output transmission lines is large, this scheme cannot effectively combine the gains of each level. The next step is to use the inductor, resistor, capacitor and interconnect line models provided by TriQuint to replace the ideal components for a more realistic simulation. Figure 3 shows the gain, matching, stability factor and noise figure of the desired final amplifier circuit. The simulation adopts a 30mA and 3.3V DC bias design to limit its power consumption to less than 100mW and achieve a compromise between output power and third-order intermodulation cutoff point. Figure 4 is the layout of the circuit, which also includes two test model tubes with probe access terminals: one is the 6×30μm enhancement-mode PHEMT used in the design, and the other is a common 6×50μm depletion-mode PHEMT.

Figure 4: Layout of a three-stage distributed amplifier (including an enhancement-mode test modeling transistor with a gate width of 180 μm and a depletion-mode test modeling transistor with a gate width of 300 μm).

In a typical distributed amplifier, half of the power is absorbed by the 50-ohm load of the output transmission line. In order to improve the output efficiency, people usually use some techniques, such as the tapered transmission line method. This design uses 50-ohm input and output lines. In order to reduce the consumption of DC power, the 50-ohm termination load at one end of the transmission line is connected in series with a larger capacitor (25pF) and then grounded through a through hole. This can not only ensure the grounding of the RF signal, but also achieve the effect of DC isolation. The DC supply current with a larger drain only flows through the low-impedance inductor element, rather than the 50-ohm termination load (as shown in Figure 5), which can effectively reduce the power consumption on the 50-ohm termination resistor. The size of the drain inductance is also an important design parameter here. The inductance directly affects the low-frequency roll-off speed of the circuit near 1GHz. If the capacitance is increased, the roll-off speed will be reduced, but at the same time, the series resistance will increase, thereby increasing the DC power consumption, and the larger inductance will also increase the layout area.

Before submitting to the production line for tape-out, each design must also undergo a strict design rule check DRC (design-rule check). Since the first MMIC design course in 198?, Johns Hopkins University has used ICED (ICEDitor) software and the DRC rules provided by TriQuint for design rule checking. In addition, the "Layout Versus Schematic" LVS (Layout Versus Schematic) tool is also used to further compare whether the netlist extracted from ADS conforms to the actual electrical connection in the ICED software. Sometimes, although the design can pass the DRC check, there are still some fatal errors, and only the LVS tool can find these problems. The new version of ADS already has a built-in connectivity check function that can eliminate some connectivity errors, but external LVS detection is still necessary.

Figure 5: The DC equivalent circuit of the distributed amplifier circuit. It can be seen that the current flowing through the inductor L35 causes only a small voltage drop.

Figure 6: Measured output power and efficiency results.

Table 1: Measured results of various indicators of the PHEMT distributed amplifier under 3.3V voltage and 25mA current bias.

Figure 6 and Table 1 are the actual test results of the entire circuit. It can be seen that under a 3.3V 24mA DC power supply, the circuit achieves a 10% power added gain PAE (Power Added Effeciency) and an output power of +10dBm. The measured and simulated values of the noise figure are also very close (Figure 7). In the 5 to 6GHz frequency band, the noise figure is only 2dB, which is an excellent performance in a circuit with a 10-octave bandwidth of 1 to 10GHz. Many other devices are placed on the 54-mil-square chip, including a 6×30μm enhanced PHEMT test model tube used in the design. This model tube was tested at 3V and 3.3 V voltages and 8 to 9mA currents, and its S parameters were used for secondary simulation of the circuit. Figure 8 is the layout of the PHEMT model tube. Figures 9 and 10 are comparisons of the measured and simulated data of the test tube. Due to the different reference planes used in the test, the parasitic parameters of the test model tube are slightly different from those of the transistors used in the actual circuit. These huge differences lead to some differences between the test values and the re-simulation results (using ADS and Sonnet software) in the high frequency band. For a single 6×30μm model tube, the actual measured value and the ADS simulation value using the TOM model are very close.

Figure 7: Gain and noise figure measured with a noise analyzer, compared with the results of ADS simulation.

Figure 8: Layout of the enhanced PHEMT test model tube with a gate width of 6×30μm.

Figure 9: Comparison of the measured (blue) forward transmission parameter S21 of the enhanced PHEMT test model tube and the simulation result (red).

MMIC modeling is very complex, for example, whether the effect of interconnects can be ignored during simulation. Ignoring interconnects can greatly simplify the design, and below 2.4GHz, the effect of interconnects is small. Usually these interconnecting microstrip lines are modeled when their length exceeds several times the substrate thickness, which rarely happens in actual MMIC design. Typical microstrip line models generally overestimate their length (i.e. inductance) effects. In addition, consider whether an electromagnetic simulation is needed to ensure that parasitic parameters ignored in the original design will not have too much impact. Unless the designer really wants to compress the layout area, it is generally not a problem to use 3 to 5 times the line width (rather than 3 to 5 times the substrate thickness) as the component spacing.

Although the measured values and simulation results of the individual 6*30μm PHEMT model tubes are very consistent, the high-end roll-off characteristics that are closer to the measured values are indeed obtained by bringing the measured data of the transistor into the circuit for secondary simulation. The designer once again used Sonnet's electromagnetic simulation software to perform electromagnetic simulation on the entire design with a resolution of 5 square microns and a substrate thickness of 100μm. For Sonnet software, the circuit area is relatively large, so it must be divided into two sub-blocks for analysis. Using the Sonnet electromagnetic simulation results plus the measured transistor parameters, the various indicators of the entire circuit are consistent with the actual test values. The simulation results of Sonnet software are also consistent with the secondary simulation results of ADS (Figures 12, 13, and 14). Note that the gain and matching are similar in shape in the high frequency band (around 10GHz), but there are still slight differences. Although these differences are small, it is still necessary to find explanations for these differences. Students in the MMIC discipline at Johns Hopkins University can learn more from these differences. Finding the source of these differences is more conducive to increasing their design experience. Using TriQuint's production line for tape-out and letting students participate in the testing of finished products made the course more practical and received unanimous praise from everyone. Johns Hopkins University also expressed its sincere gratitude to TriQuint, Agilent (formerly EEsof) and Applied Wave Research for their strong support.

Figure 10: Comparison of the measured (blue) S21 and S22 of the 6×30μm gate width enhanced PHEMT test model tube and the simulation results (red).

Figure 11: The layout used for electromagnetic simulation using Sonnet software. The circuit is divided into two blocks, and the resolution used to analyze each block is 2.5μm.

Figure 12: Comparison of measured transistor data and ADS software target results (light blue) and Sonnet simulation results (red).

The distributed MMIC amplifier using PHEMT devices shows flat broadband gain in the frequency range of 1~10GHz, and its noise figure is smaller than the previous MESFET solution. As expected by the design, the PHEMT device with a gate length of 0.5μm achieved ideal gain and noise performance under the power supply conditions of 3~3.3V and 28~32mA, with a power consumption of only 100mW, and a certain adjustment space in the bias range (which can be adjusted between 20 and 175mW). The results of re-simulation using the model tube parameters into ADS and Sonnet software are also consistent with the measured results. The measured output power, DC bias and noise figure indicators are also consistent with the simulation results. In the distributed amplifier, the method of using lumped elements or distributed transmission lines at the input and output feeder ends to absorb the capacitance of the transistor can be widely used in other MMIC processes and designs.

Figure 13: Comparison of measured, ADS-simulated (red) and Sonnet-simulated (magenta) input reflection coefficient S11.

Figure 14: Comparison of measured output reflection coefficient S22 (red), ADS simulation (blue), and Sonnet simulation (magenta)

Previous article:Digital setting, comparator with reference voltage of 0.1~9.9V

Next article:Design of a new deep submicron current sensitive amplifier technology

- High signal-to-noise ratio MEMS microphone drives artificial intelligence interaction

- Advantages of using a differential-to-single-ended RF amplifier in a transmit signal chain design

- ON Semiconductor CEO Appears at Munich Electronica Show and Launches Treo Platform

- ON Semiconductor Launches Industry-Leading Analog and Mixed-Signal Platform

- Analog Devices ADAQ7767-1 μModule DAQ Solution for Rapid Development of Precision Data Acquisition Systems Now Available at Mouser

- Domestic high-precision, high-speed ADC chips are on the rise

- Microcontrollers that combine Hi-Fi, intelligence and USB multi-channel features – ushering in a new era of digital audio

- Using capacitive PGA, Naxin Micro launches high-precision multi-channel 24/16-bit Δ-Σ ADC

- Fully Differential Amplifier Provides High Voltage, Low Noise Signals for Precision Data Acquisition Signal Chain

- Innolux's intelligent steer-by-wire solution makes cars smarter and safer

- 8051 MCU - Parity Check

- How to efficiently balance the sensitivity of tactile sensing interfaces

- What should I do if the servo motor shakes? What causes the servo motor to shake quickly?

- 【Brushless Motor】Analysis of three-phase BLDC motor and sharing of two popular development boards

- Midea Industrial Technology's subsidiaries Clou Electronics and Hekang New Energy jointly appeared at the Munich Battery Energy Storage Exhibition and Solar Energy Exhibition

- Guoxin Sichen | Application of ferroelectric memory PB85RS2MC in power battery management, with a capacity of 2M

- Analysis of common faults of frequency converter

- In a head-on competition with Qualcomm, what kind of cockpit products has Intel come up with?

- Dalian Rongke's all-vanadium liquid flow battery energy storage equipment industrialization project has entered the sprint stage before production

- Allegro MicroSystems Introduces Advanced Magnetic and Inductive Position Sensing Solutions at Electronica 2024

- Car key in the left hand, liveness detection radar in the right hand, UWB is imperative for cars!

- After a decade of rapid development, domestic CIS has entered the market

- Aegis Dagger Battery + Thor EM-i Super Hybrid, Geely New Energy has thrown out two "king bombs"

- A brief discussion on functional safety - fault, error, and failure

- In the smart car 2.0 cycle, these core industry chains are facing major opportunities!

- The United States and Japan are developing new batteries. CATL faces challenges? How should China's new energy battery industry respond?

- Murata launches high-precision 6-axis inertial sensor for automobiles

- Ford patents pre-charge alarm to help save costs and respond to emergencies

- New real-time microcontroller system from Texas Instruments enables smarter processing in automotive and industrial applications

- Failed experience of using BlueNRG-1 to make a BLE chicken-eating tool

- Exploiting software vulnerabilities! 19-year-old boy remotely hacked into Tesla

- Gizwits GoKit 3 Hardware Manual

- TMS320C6678 ZYNQ Dual-core ARM Communication Case Development Manual - matrix_multiply Case

- Monochrome screen upgrade: How to quickly upgrade the DWIN T5UIC1 color screen

- Intelligent management tools used by power operation and maintenance personnel

- Precautions for using C/C++ language to write programs based on TMS320 series DSP

- [Automatic clock-in walking timing system based on face recognition] K210 MAIXBIT uses QR code recognition as user information

- Several types of Bluetooth antennas are summarized. Which one is more familiar with Bluetooth signals? Which type of Bluetooth is used for the same chip...

- 【NXP Rapid IoT Review】+2. NXP Rapid IOT APP Connection Test

ZigBee® Network Protocols and Applications

ZigBee® Network Protocols and Applications 5G New Radio (5G NR) Reference Book

5G New Radio (5G NR) Reference Book

京公网安备 11010802033920号

京公网安备 11010802033920号