Figure 1 Typical signal conditioning chain

When designing an analog front end, follow these seven steps:

1) Describes the electrical output of the sensor or gain module front

2) Calculate ADC requirements

3) Find the best ADC + reference voltage for signal conversion

4) Find the maximum gain for the op amp and define the search criteria

5) Find the best amplifier and design the gain block

6) Check the total solution noise against the design goals

7) Run the simulation and verify

Step 1: Describe the electrical output of the sensor or gain block front

The signal may come directly from the sensor or it may pass through EMI and RFI filters before reaching the gain block. In order to design the gain block, the ac and dc characteristics of the signal and the available power supplies must be known. Knowing the characteristics of the signal and the noise level will give us an idea of what input voltage range and noise level are required when selecting the ADC. Assume that there is a sensor that outputs a 10kHz signal with a full-scale amplitude of 250 mV pp (88.2 mV rms) and 25 μV pp noise. We further assume that there is a 5V power supply available in the system. With this information, we should be able to calculate the signal-to-noise ratio at the ADC input in step 2. To simplify data processing and avoid confusion, assume that we design this solution to operate at room temperature.

Step 2: Calculate ADC Requirements

What kind of ADC do we need, what is the sampling rate, how many bits, and what is the noise specification? If we know the input signal amplitude and noise information from the first step, we can calculate the signal-to-noise ratio (SNR) at the input of the gain block. We need to choose an ADC with a better signal-to-noise ratio. When choosing an ADC, knowing the SNR will help us calculate the effective number of bits (ENOB). This relationship is expressed as follows.

Ideally, the ADC data sheet will always specify the SNR and ENOB. The required 86.8 dB SNR and 14.2-bit ENOB in this example dictate that we should choose a 16-bit analog-to-digital converter. In addition, the Nyquist criterion requires that the sampling rate (fs) should be at least twice the maximum input frequency (fin), so a 20-kSPS ADC should be sufficient. Next, we need to design the overall solution so that the noise density does not exceed 416 nV/rt-Hz.

Step 3: Find the Optimal ADC + Reference Voltage for Signal Conversion

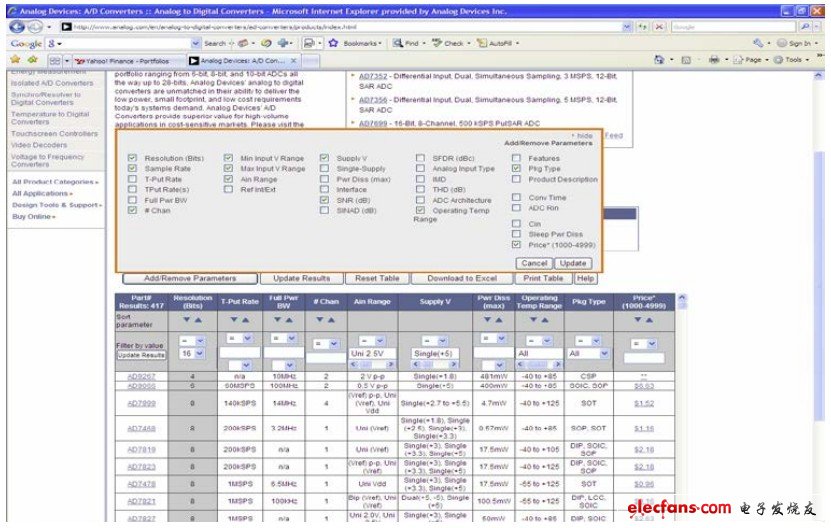

With a set of search criteria, there are many ways to find the right ADC. One of the easiest ways to find a 16-bit ADC is to use the search tool on the manufacturer's website. Enter the resolution and sampling rate, and you will find many recommended ADCs.

Many 16-bit ADCs meet the 14.5-bit ENOB requirement. If you want better noise performance, you can use oversampling to force the ENOB to 16 bits (n-bit enhancement from 4^n oversampling). Oversampling allows you to use a lower resolution ADC: a 12-bit ADC oversampled by 256 (4^4 oversampling) gives you 16-bit noise performance. In our example, this means a 12-bit ADC with a 5.126 MHz sample rate (20 kSPS × 256), or a 14-bit ADC oversampled by 4^2; 1.28 MSPS is even better. However, these options cost about the same as the AD7685 (16-bit, 250 kSPS ADC).

Figure 2 Typical ADC selection table

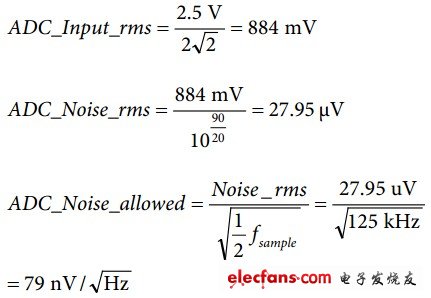

From the list, we selected the AD7685 (16-bit PulSAR ADC). This converter has a 90-dB SNR and a 250 ksps sampling rate, which meets our needs. This ADC is recommended for use with the ADR421/ADR431 precision XFET voltage reference. The 2.5-V input range exceeds the 250-mV pp input characteristic we need.

The AD7685 reference input has a dynamic input impedance and therefore requires decoupling to minimize parasitic inductance by placing a ceramic decoupling capacitor close to the pin and connecting it with wide, low-impedance traces. A 22 μF ceramic chip capacitor provides the best performance.

Step 4: Find the Maximum Gain for the Op Amp and Define the Search Criteria

Knowing the input voltage range of the ADC will help us design the gain block. To maximize the dynamic range, we need to choose the highest possible gain for the given input signal and ADC input range. This means we can design the gain block in this example to have a gain of 10.

Although the AD7685 is easy to drive, the driver amplifier needs to meet certain requirements. For example, to maintain the SNR and transition noise performance of the AD7685, the noise generated by the driver amplifier must be as low as possible, but be aware that the gain block amplifies both the signal and the noise. To keep the noise constant before and after the gain block, we need to choose an amplifier and related components with lower noise values. In addition, the THD performance of the driver should be comparable to that of the AD7685, and the ADC capacitor array must be able to settle full-scale steps at a 16-bit level (0.0015%). The noise from the amplifier can be further filtered using an external filter.

How much noise can we allow at the input of the op amp? Keep in mind that we are designing the total solution to have a noise density of no more than 416 nV/rt-Hz. We should design the gain block to have a lower noise floor by a factor of 10 since we have a gain of 10. This will ensure that the noise from the amplifier is well below the noise floor of the sensor. When calculating the noise margin, we can assume that the noise at the op amp input is roughly equal to the total noise of the op amp plus the noise of the ADC.

Step 5: Find the Optimal Amplifier and Design the Gain Block

Once the input signal bandwidth is known, the first step in op amp selection is to choose an op amp with a reasonable gain-bandwidth product (GBWP) that can handle the signal with minimal dc and ac errors. To get the best gain-bandwidth product, you need to know the signal bandwidth, noise gain, and gain error. The following sections define these terms. In general, if you want to keep the gain error less than 0.1%, it is recommended to use an amplifier with a gain bandwidth 100 times greater than the input signal bandwidth. In addition, we need an amplifier that settles quickly and has good drive capability. Note that our noise budget requires the total noise at the op amp input to be less than 40.8 nV/rt-Hz, while the ADC specifies a 7.9-nV/rt-Hz specification. To summarize the op amp search criteria: UGBW>1MHz, 5-V single supply, good voltage noise, current noise, THD characteristics, and low dc error (without degrading ADC performance).

A similar search was used when searching for an ADC, and in this case we selected the AD8641. The AD8641 is a low power, precision JFET input amplifier that features very low input bias current and rail-to-rail outputs and can operate from a 5 V to 26 V supply. The relevant data is listed in the table below. We can use the component values in the table to configure the op amp in a non-inverting configuration.

All active and passive components contribute noise to their own, so it is important to choose components that do not degrade performance. For example, it would be a waste to buy a low-noise op amp and surround it with large resistors. Keep in mind that a 1 kohm resistor contributes 4 nV of noise.

Figure 3 Complete solution

Table 1. Component values for the complete solution shown in Figure 3

Figure 5 Bandwidth simulation of the circuit shown in Figure 3

As mentioned previously, consider using an RC filter between the ADC and this gain block; this should help narrow the bandwidth and optimize the SNR.

Step 6: Check total solution noise against design goals

It is extremely important to fully understand the various error sources in the designed circuit. In order to obtain the best SNR, we need to write the total noise equation of the above scheme. The equation is shown in Formula 1:

We can calculate the total noise at the op amp input and ensure that it is less than 41.6 nV/rtHz, as we expected. The equation is shown in Equation 2:

To integrate the total noise over the entire bandwidth, we can see that the total noise at the ADC input over the filter bandwidth is 3.05μV, which is lower than the 4.16μV required by the design. Since the corner frequency of the AD8641 is less than 100 Hz, the low frequency noise (1/f) can be ignored in this example. The equation is as follows:

Maintaining a good signal-to-noise ratio requires attention to noise in every detail of the signal path and good PCB layout. Avoid running digital lines under any ADC, as this will couple noise to the chip die unless a ground plane is placed under the ADC for shielding. Fast switching signals such as CNV or clocks should not be placed near analog signal paths. Avoid overlapping digital and analog signals.

Formula 1

Formula 2

Formula 3

Step 7: Run the simulation and verify

When first verifying the circuit design, it is appropriate to use the PSpice macro model (which can be downloaded from the ADI website). A quick simulation shows the signal bandwidth we designed for the solution. Figure 5 shows the response before and after the optional RC filter at the input of the AD7685.

As shown in Figure 6, the total output noise over a 10-kHz bandwidth is close to 31 μV rms, which is slightly lower than the design target of 41 μV rms. Prototyping and verification of the entire solution is required before mass production.

Figure 6: Noise response simulation of the circuit shown in Figure 3

Summarize

Many designs today require low power and low cost, but many systems can neither afford the most expensive devices nor the higher power consumption of low noise devices. In order to get the lowest noise floor and best performance from signal conditioning circuits, designers must understand the noise sources at the component level. Maintaining a good signal-to-noise ratio requires attention to the noise in every detail of the signal path. By following the above steps, small analog signals can be successfully conditioned and converted using ultra-high resolution ADCs.

Previous article:Classification and principle of large screen splicing system

Next article:The brain of the mobile phone: an inventory of mainstream processors (Part 1)

- High signal-to-noise ratio MEMS microphone drives artificial intelligence interaction

- Advantages of using a differential-to-single-ended RF amplifier in a transmit signal chain design

- ON Semiconductor CEO Appears at Munich Electronica Show and Launches Treo Platform

- ON Semiconductor Launches Industry-Leading Analog and Mixed-Signal Platform

- Analog Devices ADAQ7767-1 μModule DAQ Solution for Rapid Development of Precision Data Acquisition Systems Now Available at Mouser

- Domestic high-precision, high-speed ADC chips are on the rise

- Microcontrollers that combine Hi-Fi, intelligence and USB multi-channel features – ushering in a new era of digital audio

- Using capacitive PGA, Naxin Micro launches high-precision multi-channel 24/16-bit Δ-Σ ADC

- Fully Differential Amplifier Provides High Voltage, Low Noise Signals for Precision Data Acquisition Signal Chain

- Innolux's intelligent steer-by-wire solution makes cars smarter and safer

- 8051 MCU - Parity Check

- How to efficiently balance the sensitivity of tactile sensing interfaces

- What should I do if the servo motor shakes? What causes the servo motor to shake quickly?

- 【Brushless Motor】Analysis of three-phase BLDC motor and sharing of two popular development boards

- Midea Industrial Technology's subsidiaries Clou Electronics and Hekang New Energy jointly appeared at the Munich Battery Energy Storage Exhibition and Solar Energy Exhibition

- Guoxin Sichen | Application of ferroelectric memory PB85RS2MC in power battery management, with a capacity of 2M

- Analysis of common faults of frequency converter

- In a head-on competition with Qualcomm, what kind of cockpit products has Intel come up with?

- Dalian Rongke's all-vanadium liquid flow battery energy storage equipment industrialization project has entered the sprint stage before production

- Allegro MicroSystems Introduces Advanced Magnetic and Inductive Position Sensing Solutions at Electronica 2024

- Car key in the left hand, liveness detection radar in the right hand, UWB is imperative for cars!

- After a decade of rapid development, domestic CIS has entered the market

- Aegis Dagger Battery + Thor EM-i Super Hybrid, Geely New Energy has thrown out two "king bombs"

- A brief discussion on functional safety - fault, error, and failure

- In the smart car 2.0 cycle, these core industry chains are facing major opportunities!

- The United States and Japan are developing new batteries. CATL faces challenges? How should China's new energy battery industry respond?

- Murata launches high-precision 6-axis inertial sensor for automobiles

- Ford patents pre-charge alarm to help save costs and respond to emergencies

- New real-time microcontroller system from Texas Instruments enables smarter processing in automotive and industrial applications

- How to spend your one-hour commute every day

- Permanent magnetic material measuring device

- High-pass filter and low-pass filter cutoff frequency problem-------------f=1/2πRC, after encountering the circuit without R...

- IoT GitHub Frame Monitor

- [ESP32-S2-Kaluga-1 Review] 1. Late unboxing

- Parameters returned by the BLE5.0 protocol stack

- Safety distance and related safety requirements

- Liquid Measurement Technology: From Water to Blood

- Analog PID

- Suddenly I want to ask myself

Three-Phase 11 kW PFC + LLC Electric Vehicle On-Board Charging (OBC) Platform User Manual (ONSEMI Semiconductor)

Three-Phase 11 kW PFC + LLC Electric Vehicle On-Board Charging (OBC) Platform User Manual (ONSEMI Semiconductor) Analog CMOS Integrated Circuit Design (2nd Edition)

Analog CMOS Integrated Circuit Design (2nd Edition)

京公网安备 11010802033920号

京公网安备 11010802033920号