summary

Analog bandwidth is more important than anything else in more and more applications. With the advent of GSPS or RF ADCs, the Nyquist zone has grown 10 times in just a few years to the multi-GHz range. This has helped the above applications expand their horizons, but in order to reach X-band (12 GHz frequency), more bandwidth is still needed. Using a sample-and-hold amplifier (THA) in the signal chain, the bandwidth can be radically extended far beyond the ADC sampling bandwidth to meet the needs of demanding high-bandwidth applications. This article will demonstrate that adding a THA in front of the latest converters developed for the RF market can achieve bandwidths in excess of 10 GHz.

Introduction

GSPS converters are the new trend, with the advantage of shortening the RF signal chain and creating more resource structures in the FPGA to use, such as reducing the downconversion in the front end and the digital downconverter (DDC) in the back end. However, there are still quite a few applications that require raw analog bandwidth (BW) at high frequencies, far beyond what RF converters can achieve. In such applications, especially in the defense and instrumentation industries (and wireless infrastructure as well), there is still a need to fully extend the bandwidth to 10 GHz or above, covering beyond the C-band and increasingly covering the X-band. As high-speed ADC technology advances, the need to accurately resolve very high intermediate frequencies (IF) in the GHz region at high speed is also increasing, with the baseband Nyquist zone exceeding 1 GHz and climbing rapidly. This statement may be outdated by the time this article is published, as developments in this area are very rapid.

This brings two major challenges: one is the converter design itself, and the other is the front-end design that couples the signal to the converter, such as amplifiers, baluns, and PCB design. The better the converter performance, the higher the requirements for front-end signal quality. More and more applications require the use of high-speed GSPS converters with resolutions of 8 to 14 bits, but the signal quality of the front end has become a bottleneck - the shortcoming of the system determines the indicators of the entire project.

Wideband is defined in this article as using signal bandwidths greater than a few hundred MHz, with frequencies ranging from near DC to the 5 GHz-10 GHz region. This article will discuss the use of wideband THAs or active sampling networks to achieve bandwidths to infinity (sorry, no Toy Story emojis available yet), and highlight the background theory that supports extending the bandwidth of RF ADCs that may not have this capability on their own. Finally, this article will explain some considerations and optimization techniques to help designers achieve a viable wideband solution for ultra-wideband applications.

Lay the foundation

For radar, instrumentation, and communications applications, high GSPS converters are widely used because they provide a wider spectrum to extend the system frequency range. However, the wider spectrum poses more challenges to the internal sample-and-hold of the ADC itself, as it is usually not optimized for ultra-wideband operation, and the ADC is generally bandwidth-limited, and its high-frequency linearity/SFDR degrades in these higher analog bandwidth regions.

Therefore, using a separate THA in front of the ADC to extend the analog bandwidth becomes an ideal solution so that very high frequency analog/RF input signals can be sampled at a precise moment. This process samples the signal through a low jitter sampler and reduces the dynamic linearity requirements of the ADC over a wider bandwidth because the sampling rate remains unchanged during the RF analog-to-digital conversion process.

这种方案带来的好处显而易见:模拟输入带宽从根本上得以扩展,高频线性度显著改善,并且与单独的RF ADC性能相比,THA-ADC组件的高频SNR得到改进。

THA characteristics and overview

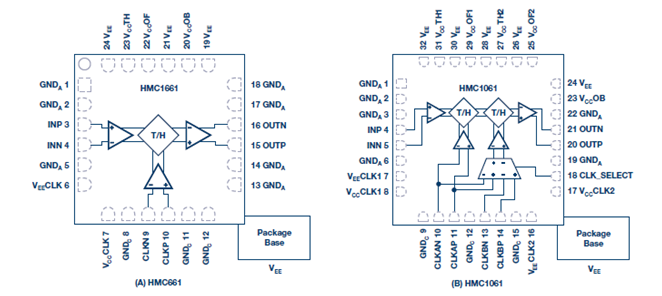

ADI's THA series can provide precision signal sampling within an 18 GHz bandwidth, with 9 to 10-bit linearity, 1.05 mV noise, and <70 fs random aperture jitter performance in the input frequency range from DC to over 10 GHz. The device can operate at 4 GSPS with minimal loss of dynamic range, and specific models include HMC661 and HMC1061. These track-and-hold amplifiers can be used to extend the bandwidth and/or high-frequency linearity of high-speed analog-to-digital conversion and signal acquisition systems.

Taking the single-stage THA HMC661 as an example, the output produced consists of two segments. During the sampling mode interval of the output waveform (positive differential clock voltage), the device becomes a unity-gain amplifier, which copies the input signal to the output stage within the constraints of the input bandwidth and the output amplifier bandwidth. At the positive-to-negative clock transition, the device samples the input signal with a very narrow sampling time aperture, and during the negative clock interval, the output is maintained at a relatively constant value representing the signal at the sampling moment. When used with an ADC for front-end sampling, single-stage devices (ADI also fabricated a two-stage THA model HMC1061) are often preferred because most high-speed ADCs already have a THA integrated internally, which usually has a much smaller bandwidth. Therefore, adding a THA before the ADC forms a composite two-stage component (or a three-stage component if a two-stage HMC1061 is used), with the THA in front of the converter. When using equivalent technology and design, single-stage devices usually have better linearity and noise performance than two-stage devices because single-stage devices have fewer stages. Therefore, single-stage devices are often the best choice for front-end sampling with high-speed ADCs.

Delay Mapping THA and ADC

One of the most difficult tasks in developing a sample-and-hold and ADC signal chain is setting the proper timing delay between the moment the THA captures a sample event and the moment it should be moved to the ADC to resample that event. The process of setting the ideal time difference between the two efficient sampling systems is called delay mapping.

Figure 1. Sample-and-hold topologies: (1a) single-row, (1b) dual-row.

Figure 2. Delay mapping circuit.

This process can be tedious to complete on the board, as the paper analysis may not take into account the corresponding delays caused by the propagation spacing of the clock traces on the PCB board, internal device group delays, ADC aperture delays, and the associated circuitry involved in splitting the clock into two different segments (one clock trace for the THA and the other clock trace for the ADC). One way to set the delay between the THA and the ADC is to use variable delay lines. These devices can be active or passive, and the purpose is to properly align the timing of the THA sampling process and hand it off to the ADC for sampling. This ensures that the ADC samples the stable hold mode portion of the THA output waveform, accurately representing the input signal.

As shown in Figure 2, the HMC856 can be used to enable this delay. It is a 5-bit QFN package with an intrinsic delay of 90 ps in steps of 3 ps or 25 ps, and a 32-bit high-speed delay. Its disadvantage is the need to set/step through each delay setting. To enable a new delay setting, each bit/pin on the HMC856 needs to be pulled to a negative voltage. Therefore, it can be a tedious task to find the best delay setting among the 32 combinations by soldering pull-down resistors. To solve this problem, ADI uses serially controlled SPST switches and an off-board microprocessor to help complete the delay setting process faster.

To obtain the best delay setting, a signal is applied to the THA and ADC combination that is outside the ADC bandwidth. In this example, a signal of approximately 10 GHz is selected and applied at a level of -6 dBFS (captured on the FFT display). The delay setting is now swept in a binary step fashion, with the level and frequency of the signal held constant. The FFT is displayed and captured during the sweep, collecting fundamental power and spurious-free dynamic range (SFDR) values for each delay setting.

The results are shown in Figure 3a, where the fundamental power, SFDR, and SNR will vary with each setting applied. As shown, when the sampling position is placed in a better place (in the process of the THA sending samples to the ADC), the fundamental power will be at the highest level, while the SFDR should be at the best performance (i.e., lowest). Figure 3b is a zoomed-in view of the delay mapping sweep, with the delay set point at 671, i.e., the delay should remain fixed in this window/position. Keep in mind that the delay mapping procedure is only valid for the relevant sampling frequency of the system, and if the design requires a different sampling clock, a re-sweep will be required. In this case, the sampling frequency is 4 GHz, which is the highest sampling frequency of the THA device used in this signal chain.

Figure 3a. Mapping results of signal amplitude and SFDR performance at each delay setting.

Figure 3b. Mapping results of signal amplitude and SFDR performance at each delay setting (zoomed in).

Front-end design for massive raw analog bandwidth

First, if the key objective of the application is to process 10 GHz of bandwidth, we should obviously consider the RF approach. Note that the ADC is still a voltage-mode device and power is not a consideration. The word “matched” should be used with caution in this context. We have found that matching a converter front end to a 100 MSPS converter at every frequency is nearly impossible; a high frequency bandwidth RF ADC will not be much different, but the challenge remains. The term “matched” should refer to the optimization in the front-end design that produces the best results. This is an all-encompassing term where input impedance, AC performance (SNR/SFDR), signal drive strength or input drive, bandwidth, and passband flatness are all metrics that produce the best results for that specific application.

Ultimately, these parameters together define the matching performance of the system application. When starting a broadband front-end design, layout can be critical, and the number of components should be minimized to reduce the loss between two adjacent ICs. Both aspects are very important to achieve the best performance. Be careful when connecting the analog input networks together. Trace length and matching are the most important, and the number of vias should also be minimized, as shown in Figure 4.

Figure 4. THA and ADC layout.

Figure 5. THA and ADC front-end network and signal chain.

The signals are connected to the THA inputs in differential mode (we also provide a reference design link for single-ended RF signal inputs), forming a single front-end network. To minimize the number of vias and overall length, we have taken special care here to not have vias pass through the two analog input paths and to help offset any stubs in the trace connections.

The final design is fairly simple with only a few caveats, as shown in Figure 5. The 0.01 μF capacitors used are broadband types, which help keep the impedance flat over a wide frequency range. Typical off-the-shelf 0.1 μF capacitors do not provide a flat impedance response and typically introduce more ripple in the passband flatness response. The 5Ω and 10Ω series resistors at the THA output and ADC input help reduce peaking at the THA output and minimize distortion caused by residual charge injection from the ADC’s own internal sampling capacitor network. However, these values need to be chosen carefully or they may increase signal attenuation and force the THA to increase drive strength, or the design may not utilize the full range of the ADC.

Finally, let’s discuss differential shunt termination. This is critical when connecting two or more converters together. Generally, a light load, such as 1 kΩ on the input, helps maintain linearity and keeps reverberant frequencies in check. A 120 Ω shunt load on the shunt also does this, but creates more of a practical load, 50 Ω in this case, which is what the THA wants to see and optimize for.

现在看结果!检查图6中的信噪比或SNR,可以看出在15 GHz范围上可以实现8位的ENOB(有效位数)。这是相当不错的,想想对于相同性能的13 GHz示波器,您可能支付了12万美元。当频率向L、S、C和X波段移动时,集成带宽(即噪声)和抖动限制开始变得显著,因此我们看到性能出现滚降。

It should also be noted that in order to keep the voltage level between the THA and the ADC constant, the full-scale input of the ADC is changed internally to 1.0 V pp via the SPI register. This helps keep the THA in the linear region, as its maximum output is 1.0 V pp differential.

Figure 6. – SNRFS/SFDR performance results at 6 dBFS.

The linearity results or SFRD are also shown. Here, the linearity is over 50 dBc to 8 GHz and over 40 dBc to 10 GHz. To achieve the best linearity over such a wide frequency range, the design here was optimized using the AD9689 analog input buffer current setting feature (via the SPI control register).

Figure 7 shows the passband flatness, demonstrating that adding a THA before the RF ADC can achieve a bandwidth of 10 GHz, fully extending the analog bandwidth of the AD9689.

Figure 7. THA and ADC network and signal chain—bandwidth results.

Conclusion

For applications that require optimal performance over multi-GHz analog bandwidths, THAs are almost a necessity, at least for now! RF ADCs are catching up quickly. It is easy to see that GSPS converters have a theoretical ease-of-use advantage when sampling wider bandwidths to cover multiple bands of interest, eliminating one or more down-mixing stages on the front-end RF strip. However, achieving higher range bandwidths can present design challenges and maintenance issues.

When using a THA in a system, one should ensure that the location of the sampling point is optimized between the THA and the ADC. Using the delay mapping procedure described in this article will yield the best overall performance results. Understanding the procedure is tedious, but very important. Finally, one should remember that matching the front end really means achieving the best performance for a given set of performance requirements for the application. The Lego approach (simply connecting 50 Ω impedance blocks together) may not be the best approach when sampling at X-band frequencies.

Previous article:Implantable electronic devices have amazing performance! A battery-free, self-powered pacemaker is now available

Next article:Planning and strategizing – grinding of hip implants

- Popular Resources

- Popular amplifiers

- Chen Han from Rouling Technology: Bringing small, flexible brain-computer interface sleep devices to every household

- Li Xiaojian of Weiling Medical: Brain-computer interface technology is opening a new era of integration of consciousness and AI

- Geng Dong of Jingyu Medical: Brain-computer interface DBS treatment technology has achieved domestic substitution

- Wang Changming from Capital Medical University: Digital therapy for epilepsy has entered the use stage

- Shi Chunbo of Qianqiu Intelligent: Using digital therapy to illuminate the light of children with autism

- Feng Shang, Digital Medicine Intelligence: ADHD digital therapy is providing more effective and convenient services for children with ADHD

- Ultrasound patch can continuously and noninvasively monitor blood pressure

- High-speed 3D bioprinter is available, using sound waves to accurately build cell structures in seconds

- [“Source” Observation Series] Application of Keithley in Particle Beam Detection Based on Perovskite System

- Intel promotes AI with multi-dimensional efforts in technology, application, and ecology

- ChinaJoy Qualcomm Snapdragon Theme Pavilion takes you to experience the new changes in digital entertainment in the 5G era

- Infineon's latest generation IGBT technology platform enables precise control of speed and position

- Two test methods for LED lighting life

- Don't Let Lightning Induced Surges Scare You

- Application of brushless motor controller ML4425/4426

- Easy identification of LED power supply quality

- World's first integrated photovoltaic solar system completed in Israel

- Sliding window mean filter for avr microcontroller AD conversion

- What does call mean in the detailed explanation of ABB robot programming instructions?

- STMicroelectronics discloses its 2027-2028 financial model and path to achieve its 2030 goals

- 2024 China Automotive Charging and Battery Swapping Ecosystem Conference held in Taiyuan

- State-owned enterprises team up to invest in solid-state battery giant

- The evolution of electronic and electrical architecture is accelerating

- The first! National Automotive Chip Quality Inspection Center established

- BYD releases self-developed automotive chip using 4nm process, with a running score of up to 1.15 million

- GEODNET launches GEO-PULSE, a car GPS navigation device

- Should Chinese car companies develop their own high-computing chips?

- Infineon and Siemens combine embedded automotive software platform with microcontrollers to provide the necessary functions for next-generation SDVs

- Continental launches invisible biometric sensor display to monitor passengers' vital signs

- ADI reference material sharing

- EEWORLD University ---- Embedded C Language

- Espressif ESP32-S3-WROOM-2 latest information

- Global wireless spectrum resource allocation map

- Analog Electronics Popular Data Download Collection

- Terminal Software XShell Manual

- Ultra-long CIS image acquisition system based on FPGA.pdf

- EEWORLD University Hall ---- Introduction to Internet of Things Engineering by Wang Zhiliang, University of Science and Technology Beijing

- GaN Hardware and Software Co-design & RF Device Architecture

- What parameters should be considered when selecting a voltage regulator?

ACA2402ERS7P2

ACA2402ERS7P2

京公网安备 11010802033920号

京公网安备 11010802033920号