In the previous experiment, we explained how to relocate the code, but relocating the code to the IRAM with only 256K is not very useful. The correct way is to relocate the code to the main memory with larger capacity, that is, DRAM.

There are two independent DRAM controllers in Exynos4412, called DMC0 and DMC1. DMC0 and DMC1 support DRAM up to 1.5GB respectively. They both support DDR2/DDR3 and LPDDR2, 512Mb, 1Gb, 2Gb, 4Gb and 8Gbit memory devices, and support 16/32bit bit width. The address corresponding to DRAM0 is 0x4000_0000~0xAFFF_FFF, totaling 1.5GB, and the address corresponding to DRAM1 is 0xA000_000~0x0000_0000, totaling 1.5GB.

![]()

DRAM Controller Address Map

The 1GB DRAM of Tiny4412 is composed of 4 128MX16 DDR3 chips. Here is the schematic diagram of Tiny4412:

Tiny4412 DDR Circuit Diagram

Tiny4412 DDR Circuit Diagram

As can be seen from the above two figures, the four DDR chips are divided into groups of two to form 32-bit data, and all four chips are connected to DMC0.

How can we use DRAM? For Tiny4412, since DMC0 is used, we need to initialize DMC0 and DDR3 DRAM chip.

Below the statement:

From this section, our program structure has changed. In the previous experiments, we only generated one file. From this experiment, we generate two files, BL2.bin and main.bin. The link address of BL2.bin is 0x02023400; (position-independent code is used, and the program can run in any available memory), and the link address of main.bin is 0x43E00000 (position-independent code is not used, and all programs must be located at this address to run normally). Three parts of the program need to be burned on the SD card, namely:

1.BL1 (provided by Samsung): implement some initialization

2.BL2 (we write the source code ourselves and generate it with the mkbl2 tool): board-level initialization, complete code relocation to DDR SDRAM, and complete the jump

3. Main code: implement the functions we want

The locations of the three parts of code on the SD card are as follows:

Programs are distributed on the SD card

As can be seen from the figure, BL1.bin is burned to SD card sector 1, BL2.bin is burned to SD card sector 17, and main.bin is burned to SD card sector 49.

The running process of the whole program is as follows: after the system is powered on, bl1 at sector 1 of the SD card is first copied to the 0x02020000 address of IRAM, and then this part of the code is run. This part of the code will first load BL2.bin, which will initialize the clock and DRAM, and then copy main.bin located at sector 49 in the SD card to the 0x43E00000 address of DRAM, and finally jump to this address to continue running.

1. Program Description

We have already gone through the DDR initialization sequence in the previous article Tiny4412 bare metal program DDR3 initialization process . Now we will set it up one by one according to the steps mentioned above.

Note: Seeing so many setup steps is really cumbersome. Let's refer to the code in u-boot for Tiny4412 to figure out what it sets:

================================================================

//(C) Copyright 2011 Samsung Electronics Co. Ltd

//

//See file CREDITS for list of people who contributed to this

//project.

//

//This program is free software; you can redistribute it and/or modify

//it under the terms of the GNU General Public License version 2 as

//published by the Free Software Foundation.

#include "config.h"

#include "asm/arch/cpu.h"

#define MCLK_400

.globl mem_ctrl_asm_init

mem_ctrl_asm_init:

// Async bridge configuration at CPU_core:

// 1: half_sync

// 0: full_sync */

ldr r0, =0x10010350

mov r1, #1

str r1, [r0]

// I don't know what these lines of code mean, and why they are done this way

///////////////////////////////////////////////////////////////////

//--------------------------------DREX0---------------------------

///////////////////////////////////////////////////////////////////

ldr r0, =APB_DMC_0_BASE

ldr r1, =0xe0000086

str r1, [r0, #DMC_PHYCONTROL1]

//2. If on die termination is required, enable PhyControl1.term_write_en,

//PhyControl1.term_read_en.

ldr r1, =0xE3854C03

str r1, [r0, #DMC_PHYZQCONTROL]

//3. If ZQ calibration is required, disable PhyZQControl.

// ctrl_zq_mode_noterm and enable PhyZQCon-trol.

// ctrl_zq_start so that the PHY automatically calibrates

// the I/Os to match the driving and termination impedance

// by referencing resistor value of an external resistor

// and updates the matched value during auto re-fresh cycles.

move r2, #0x100000

1: subs r2, r2, #1

bne 1b

ldr r1, =0x7110100A

str r1, [r0, #DMC_PHYCONTROL0]

//4. Set the PhyControl0.ctrl_start_point and PhyControl0.

// ctrl_inc bit-fields to correct value according to clock frequency.

// Set the PhyControl0.ctrl_dll_on bit-field to "1" to activate the PHY DLL.

ldr r1, =0xe0000086

str r1, [r0, #DMC_PHYCONTROL1]

//5. DQS Cleaning: set the PhyControl1.ctrl_shiftc and PhyControl1.

// ctrl_offsetc bit-fields to the proper value according to clock frequency,

// board delay and memory tDQSCK parameter.

ldr r1, =0x7110100B

str r1, [r0, #DMC_PHYCONTROL0]

// 6. Set the PhyControl0.ctrl_start bit-field to "1".

ldr r1, =0x00000000

str r1, [r0, #DMC_PHYCONTROL2]

// DQS offset

// After some experimentation, it can be omitted, the default value is all zeros

ldr r1, =0x0FFF301A

str r1, [r0, #DMC_CONCONTROL]

// 7. Set the ConControl. At this moment,an auto refresh counter should be off.

ldr r1, =0x00312640

str r1, [r0, #DMC_MEMCONTROL]

// 8. Set the MemControl. At this moment,

// all power down modes and periodic ZQ(pzq_en) should be off.

ldr r1, =0x40e01323

str r1, [r0, #DMC_MEMCONFIG0]

ldr r1, =0x60e01323

str r1, [r0, #DMC_MEMCONFIG1]

// 9. Set the MemConfig0 register. If there are two external memory chips,

// also set the MemConfig1 register.

ldr r1, =(0x80000000 | CONFIG_IV_SIZE)

str r1, [r0, #DMC_IVCONTROL]

// Memory Channel Interleaving

// After some experimentation, it can be omitted and the default value can be used

ldr r1, =0xff000000

str r1, [r0, #DMC_PRECHCONFIG]

// 10. Set the PrechConfig and PwrdnConfig registers.

ldr r1, =0x000000BB

str r1, [r0, #DMC_TIMINGAREF] @TimingAref

ldr r1, =0x4046654f

str r1, [r0, #DMC_TIMINGROW] @TimingRow

ldr r1, =0x46400506

str r1, [r0, #DMC_TIMINGDATA] @TimingData

ldr r1, =0x52000a3c

str r1, [r0, #DMC_TIMINGPOWER] @TimingPower

// 11. Set the TimingAref, TimingRow, TimingData and

// TimingPower registers according to memory AC parame-ters.

// chip 0

ldr r1, =0x07000000

str r1, [r0, #DMC_DIRECTCMD]

// 19. Issue a NOP command using the DirectCmd register to assert

//and to hold CKE to a logic high level.

move r2, #0x100000

2: subs r2, r2, #1

bne 2b

// 20. Wait for tXPR(max(5nCK,tRFC(min)+10ns)) or set tXP to tXPR value before step

// 17. If the system set tXP to tXPR, then the system must set tXP to proper value

// before normal memory operation.

ldr r1, =0x00020000

str r1, [r0, #DMC_DIRECTCMD]

ldr r1, =0x00030000

str r1, [r0, #DMC_DIRECTCMD]

ldr r1, =0x00010002

str r1, [r0, #DMC_DIRECTCMD]

ldr r1, =0x00000328

str r1, [r0, #DMC_DIRECTCMD]

// I don't understand what command is issued here

move r2, #0x100000

3: subs r2, r2, #1

bne 3b

ldr r1, =0x0a000000

str r1, [r0, #DMC_DIRECTCMD]

// 26. Issues a ZQINIT commands using the DirectCmd register.*/

move r2, #0x100000

4: subs r2, r2, #1

bne 4b

// 27. If there are two external memory chips, perform steps 19 ~ 26

// procedures for chip1 memory device.

#if 1

// chip 1

ldr r1, =0x07100000

str r1, [r0, #DMC_DIRECTCMD]

move r2, #0x100000

5: subs r2, r2, #1

bne 5b

ldr r1, =0x00120000

str r1, [r0, #DMC_DIRECTCMD]

ldr r1, =0x00130000

str r1, [r0, #DMC_DIRECTCMD]

ldr r1, =0x00110002

str r1, [r0, #DMC_DIRECTCMD]

ldr r1, =0x00100328

str r1, [r0, #DMC_DIRECTCMD]

move r2, #0x100000

6: subs r2, r2, #1

bne 6b

ldr r1, =0x0a100000

str r1, [r0, #DMC_DIRECTCMD]

move r2, #0x100000

7: subs r2, r2, #1

bne 7b

#endif

ldr r1, =0xe000008e

str r1, [r0, #DMC_PHYCONTROL1]

ldr r1, =0xe0000086

str r1, [r0, #DMC_PHYCONTROL1]

move r2, #0x100000

8: subs r2, r2, #1

bne 8b

///////////////////////////////////////////////////////////////////

//--------------------------DREX1-------------------- -------------/

///////////////////////////////////////////////////////////////////

ldr r0, =APB_DMC_1_BASE

ldr r1, =0xe0000086

str r1, [r0, #DMC_PHYCONTROL1]

ldr r1, =0xE3854C03

str r1, [r0, #DMC_PHYZQCONTROL]

move r2, #0x100000

1: subs r2, r2, #1

bne 1b

ldr r1, =0xe000008e

str r1, [r0, #DMC_PHYCONTROL1]

ldr r1, =0xe0000086

str r1, [r0, #DMC_PHYCONTROL1]

ldr r1, =0x71101008

str r1, [r0, #DMC_PHYCONTROL0]

ldr r1, =0x7110100A

str r1, [r0, #DMC_PHYCONTROL0]

ldr r1, =0xe0000086

str r1, [r0, #DMC_PHYCONTROL1]

ldr r1, =0x7110100B

str r1, [r0, #DMC_PHYCONTROL0]

ldr r1, =0x00000000

str r1, [r0, #DMC_PHYCONTROL2]

ldr r1, =0x0FFF301A

str r1, [r0, #DMC_CONCONTROL]

ldr r1, =0x00312640

str r1, [r0, #DMC_MEMCONTROL]

ldr r1, =0x40e01323 @Interleaved?

str r1, [r0, #DMC_MEMCONFIG0]

ldr r1, =0x60e01323

str r1, [r0, #DMC_MEMCONFIG1]

ldr r1, =(0x80000000 | CONFIG_IV_SIZE)

str r1, [r0, #DMC_IVCONTROL]

ldr r1, =0xff000000

str r1, [r0, #DMC_PRECHCONFIG]

ldr r1, =0x000000BB

str r1, [r0, #DMC_TIMINGAREF] @TimingAref

ldr r1, =0x4046654f

str r1, [r0, #DMC_TIMINGROW] @TimingRow

ldr r1, =0x46400506

str r1, [r0, #DMC_TIMINGDATA] @TimingData

ldr r1, =0x52000a3c

str r1, [r0, #DMC_TIMINGPOWER] @TimingPower

// chip 0

ldr r1, =0x07000000

str r1, [r0, #DMC_DIRECTCMD]

move r2, #0x100000

2: subs r2, r2, #1

bne 2b

ldr r1, =0x00020000

str r1, [r0, #DMC_DIRECTCMD]

ldr r1, =0x00030000

str r1, [r0, #DMC_DIRECTCMD]

ldr r1, =0x00010002

str r1, [r0, #DMC_DIRECTCMD]

ldr r1, =0x00000328

str r1, [r0, #DMC_DIRECTCMD]

move r2, #0x100000

3: subs r2, r2, #1

bne 3b

ldr r1, =0x0a000000

str r1, [r0, #DMC_DIRECTCMD]

move r2, #0x100000

4: subs r2, r2, #1

bne 4b

#if 1

// chip 1

ldr r1, =0x07100000

str r1, [r0, #DMC_DIRECTCMD]

move r2, #0x100000

5: subs r2, r2, #1

bne 5b

ldr r1, =0x00120000

str r1, [r0, #DMC_DIRECTCMD]

ldr r1, =0x00130000

str r1, [r0, #DMC_DIRECTCMD]

ldr r1, =0x00110002

str r1, [r0, #DMC_DIRECTCMD]

ldr r1, =0x00100328

str r1, [r0, #DMC_DIRECTCMD]

move r2, #0x100000

6: subs r2, r2, #1

bne 6b

ldr r1, =0x0a100000

str r1, [r0, #DMC_DIRECTCMD]

move r2, #0x100000

7: subs r2, r2, #1

bne 7b

#endif

ldr r1, =0xe000008e

str r1, [r0, #DMC_PHYCONTROL1]

ldr r1, =0xe0000086

str r1, [r0, #DMC_PHYCONTROL1]

move r2, #0x100000

8: subs r2, r2, #1

bne 8b

///////////////////////////////////////////////////////////////////

//-----------------------Finalize---------------------------------/

///////////////////////////////////////////////////////////////////

ldr r0, =APB_DMC_0_BASE

ldr r1, =0x0FFF303A

str r1, [r0, #DMC_CONCONTROL]

// 28. Set the ConControl to turn on an auto refresh counter.

ldr r0, =APB_DMC_1_BASE

ldr r1, =0x0FFF303A

str r1, [r0, #DMC_CONCONTROL]

// 28. Set the ConControl to turn on an auto refresh counter.

mov pc, lr

================================================================

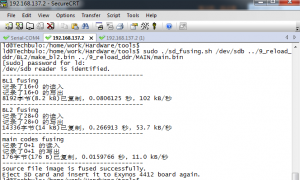

2. Compile, burn and run

1. Compile

Upload the file to the server via FTP or other tools, and enter the make command to compile to get the make_bl2.bin and main.bin files.

2. Burn

Insert the SD card into the computer and let Ubuntu in VmWare recognize it, then execute the following command:

1 | sudo ./sd_fusing.sh /dev/sdb ../9_reload_ddr/BL2/make_bl2.bin ../9_reload_ddr/MAIN/main.bin |

Program burning

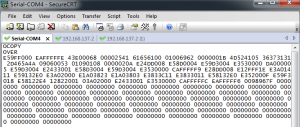

2. Operation phenomenon

Insert the SD card into the Tiny4412 development board, connect the serial port tool, and power on. You will see the same running effect as in the previous section (because we did not modify the LED display effect, but only modified the program's running address, which is invisible to the outside world).

The serial port can see the following display information;

running result

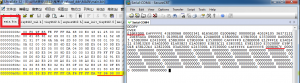

The content at address 0x43E00000 printed from the information room of the figure (the link address of the main.bin file)

We compared the above printed information with the main.bin file and found that they are exactly the same, indicating that the code has been copied to the correct link address.

File Comparison

Previous article:Exynos4412 bare metal program UART sending and receiving data

Next article:Exynos4412 bare metal program DDR3 initialization process

Recommended ReadingLatest update time:2024-11-16 15:54

- Popular Resources

- Popular amplifiers

Professor at Beihang University, dedicated to promoting microcontrollers and embedded systems for over 20 years.

Professor at Beihang University, dedicated to promoting microcontrollers and embedded systems for over 20 years.

- Innolux's intelligent steer-by-wire solution makes cars smarter and safer

- 8051 MCU - Parity Check

- How to efficiently balance the sensitivity of tactile sensing interfaces

- What should I do if the servo motor shakes? What causes the servo motor to shake quickly?

- 【Brushless Motor】Analysis of three-phase BLDC motor and sharing of two popular development boards

- Midea Industrial Technology's subsidiaries Clou Electronics and Hekang New Energy jointly appeared at the Munich Battery Energy Storage Exhibition and Solar Energy Exhibition

- Guoxin Sichen | Application of ferroelectric memory PB85RS2MC in power battery management, with a capacity of 2M

- Analysis of common faults of frequency converter

- In a head-on competition with Qualcomm, what kind of cockpit products has Intel come up with?

- Dalian Rongke's all-vanadium liquid flow battery energy storage equipment industrialization project has entered the sprint stage before production

- Allegro MicroSystems Introduces Advanced Magnetic and Inductive Position Sensing Solutions at Electronica 2024

- Car key in the left hand, liveness detection radar in the right hand, UWB is imperative for cars!

- After a decade of rapid development, domestic CIS has entered the market

- Aegis Dagger Battery + Thor EM-i Super Hybrid, Geely New Energy has thrown out two "king bombs"

- A brief discussion on functional safety - fault, error, and failure

- In the smart car 2.0 cycle, these core industry chains are facing major opportunities!

- The United States and Japan are developing new batteries. CATL faces challenges? How should China's new energy battery industry respond?

- Murata launches high-precision 6-axis inertial sensor for automobiles

- Ford patents pre-charge alarm to help save costs and respond to emergencies

- New real-time microcontroller system from Texas Instruments enables smarter processing in automotive and industrial applications

- New Tang 8051 (1T) Quickly build the entry keil environment

- A python comic

- A display solution for APF system information——Based on Topmicro intelligent display module

- Is there any way in KEIL4 to find out whether == in IF() is written as =?

- [Analog Electronics Course Selection Test] + Strongly targeted functions

- Why does CCS need to install a driver?

- The age of gadgets freeing your hands

- How does BLUE NRG1 achieve one-to-many communication?

- Solar Simple Automatic Tracker

- Questions about the constant current source composed of op amp and MOS tube

Production of Linux file system without interface for embedded development board

Production of Linux file system without interface for embedded development board Detailed analysis of the relocation principle of uboot

Detailed analysis of the relocation principle of uboot

京公网安备 11010802033920号

京公网安备 11010802033920号