1. Memory format (word alignment):

The Arm architecture treats memory as a linear combination of bytes starting from address zero. The first stored word (32-bit) data is placed from byte zero to byte three, and the second stored word data is placed from byte four to byte seven, arranged one by one. As a 32-bit microprocessor, the maximum addressing space supported by the Arm architecture is 4GB.

Storage format

1. Big-endian format: high byte at low address, low byte at high address;

2. Little-endian format: high byte at high address, low byte at low address;

Instruction length:

The instruction length of the Arm microprocessor is 32 bits, and can also be 16 bits (in thumb mode). The Arm microprocessor supports three data types: byte (8 bits), halfword (16 bits), and word (32 bits). Among them, words need to be aligned to 4 bytes, and halfwords need to be aligned to 2 bytes.

Note: The so-called instruction length is the length of a complete instruction, not just the length of the three letters mov.

2. The ARM system CPU has two working states

1. ARM state: the processor executes 32-bit word-aligned ARM instructions;

2. Thumb state: The processor executes 16-bit, half-word aligned Thumb instructions;

During the program execution, the two states can be switched accordingly. The change of the processor working state does not affect the processor's working mode and the contents of the corresponding registers.

CPU is powered on in ARM state

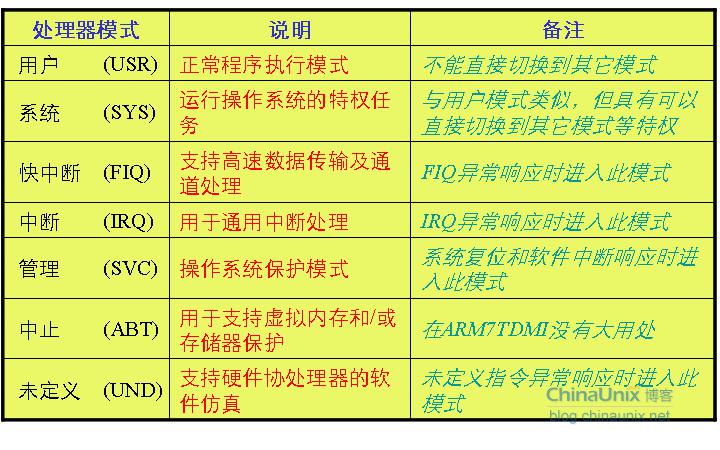

3. The ARM system CPU has the following 7 working modes:

1. User mode (Usr): used for normal program execution;

2. Fast interrupt mode (FIQ): used for high-speed data transmission;

3. External interrupt mode (IRQ): used for normal interrupt processing;

4. Management mode (svc): protection mode used by the operating system;

5. Data access termination mode (abt): This mode is entered when data or instruction prefetching is terminated. It can be used for virtual storage and storage protection.

6. System mode (sys): runs privileged operating system tasks;

7. Undefined instruction abort mode (und): This mode is entered when an undefined instruction is executed and can be used to support hardware;

There are two ways to switch the working mode of Arm:

Passive switching: some exceptions or interrupts are generated when the arm is running to automatically switch modes

Active switching: through software changes, that is, the software sets the register to perform arm mode switching, because the arm's working mode can be switched by assigning values to the corresponding registers.

Tips: When the processor runs in user mode, certain protected system resources cannot be accessed.

Except for the user mode, the other six working modes are privileged modes;

The other five modes in the privileged mode except the system mode are called exception modes;

Most programs run in user mode;

Entering privileged mode is to handle interrupts, exceptions, or access protected system resources;

4. Register

ARM has 31 general 32-bit registers and 6 program status registers, which are divided into 7 groups. Some registers are shared by all working modes, and some registers are specific to each working mode.

R13 - Stack pointer register, used to save the stack pointer;

R14 - Program connection register. When the BL subroutine call instruction is executed, R14 gets the backup of R15. When an interrupt or exception occurs, R14 saves the return value of R15.

R15——Program counter;

The fast interrupt mode has 7 backup registers R8-R14, which makes it unnecessary to save any registers when entering the fast interrupt mode to execute a large part of the program;

Other privileged modes have two independent copies of registers, R13 and R14, so that each mode can have its own stack pointer and connection registers;

5. Current Program Status Register (CPSR)

The meaning of each bit in CPSR is as follows:

T bit: 1——CPU is in Thumb state, 0——CPU is in ARM state;

I, F (interrupt disable bit): 1-disable interrupt, 0-enable interrupt;

Working mode bits: These bits can be changed to switch modes;

6. Program Status Save Register (SPSR)

When switching to a privileged mode, the SPSR saves the CPSR value of the previous working mode, so that when returning to the previous working mode, the value of the SPSR can be restored to the CPSR;

7. Mode Switching

When an exception occurs and the CPU enters the corresponding exception mode, the following tasks are automatically completed by the CPU:

1. Save the address of the next instruction to be executed in the previous working mode in R14 of the exception mode;

2. Copy the value of CPSR to the SPSR of the exception mode;

3. Set the working mode of CPSR to the working mode corresponding to the abnormal mode;

4. Set the PC value to the address of this exception mode in the exception vector table, that is, jump to execute the corresponding instruction in the exception vector table;

When returning from an abnormal working mode to the previous working mode, the software needs to complete the following tasks:

1. Subtract an appropriate value (4 or 8) from R14 in the exception mode and assign it to the PC register;

2. Assign the value of the exception mode SPSR to the CPSR;

================================================== ==================================

Reprint: Detailed explanation of big-endian and little-endian storage modes

Storage mode:

Little endian: higher significant bytes are stored in higher memory addresses, and lower significant bytes are stored in lower memory addresses.

Big endian: higher significant bytes are stored in lower memory addresses, and lower significant bytes are stored in higher memory addresses.

STM32 belongs to the little endian mode. Simply put: for example: temp = 0X12345678; assuming that the address of temp is: 0X4000 0000

, then, in the memory, its storage becomes:

| address | HEX |

|0X4000 0000 |78 56 43 12|

A little simpler:

low address---------->high address [big endian mode]:

0X12|0X34|0X56|0X78|

low address---------->high address [little endian mode]:

0X78|0X56|0X34|0X12|

Advantages of big endian and little endian

There is no advantage or disadvantage between the two. Each advantage is the disadvantage of the other.

Big endian mode: the determination of the sign bit is fixed to the first byte, which is easy to judge positive and negative.

Little-endian mode: Forced conversion of data does not require adjustment of byte content, and 1, 2, and 4 bytes are stored in the same way.

Array storage in big-endian and little-endian situations:

Take unsigned int value = 0x12345678 as an example,

and look at its storage in the two byte orders.

We can use unsigned char buf[4] to represent value:

Big-Endian: The low address stores the high bit, as follows:

High address

---------------

buf[3] (0x78) -- Low bit

buf[2] (0x56)

buf[1] (0x34)

buf[0] (0x12) -- High bit

---------------

low address

Little-Endian: The low address stores the low bit, as follows:

High address

---------------

buf[3] (0x12) -- High bit

buf[2] (0x34)

buf[1] (0x56)

buf[0] (0x78) -- Low bit

-------------- Why is there a big-endian and small-endian difference in

low address : This is because in the computer system, we use bytes as units, and each address unit corresponds to a byte, and a byte is 8 bits. However, in C language, in addition to 8-bit char, there are also 16-bit short type and 32-bit long type (depending on the specific compiler). In addition, for processors with a bit number greater than 8 bits, such as 16-bit or 32-bit processors, since the register width is greater than one byte, there must be a problem of how to arrange multiple bytes. Therefore, it leads to the big-endian storage mode and the little-endian storage mode. For example, a 16-bit short type x, the address in the memory is 0x0010, and the value of x is 0x1122, then 0x11 is the high byte and 0x22 is the low byte. For the big-endian mode, 0x11 is placed in the low address, that is, 0x0010, and 0x22 is placed in the high address, that is, 0x0011. The little-endian mode is just the opposite. The X86 architecture we commonly use is in little-endian mode, while KEIL C51 is in big-endian mode. Many ARM and DSP are in little-endian mode. Some ARM processors can also select big-endian or little-endian mode by hardware. Byte order: [Generally, operating systems are little-endian, while communication protocols are big-endian] Common CPU byte orders: Big Endian: PowerPC, IBM, Sun Little Endian: x86, DEC ARM can work in both big-endian and little-endian modes. Common file byte orders: Adobe PS – Big Endian BMP – Little Endian DXF (AutoCAD) – Variable GIF – Little Endian JPEG – Big Endian MacPaint – Big Endian RTF – Little Endian In addition, Java and all network communication protocols use Big-Endian encoding. You can use the code to test whether the CPU is big-endian or little-endian: //CPU big-endian //0, little-endian mode; 1, big-endian mode. static u8 cpu_endian; //Get the CPU big-endian mode, and save the result in cpu_endian void find_cpu_endian(void) { int x=1; if(*(char*)&x==1)cpu_endian=0; //Little-endian mode else cpu_endian=1; //Big-endian mode } In the above test, on STM32, you will get cpu_endian=0, which is little-endian mode.

Previous article:OK6410 bare metal interrupt processing

Next article:OK6410 bare metal exception handling

- Popular Resources

- Popular amplifiers

Professor at Beihang University, dedicated to promoting microcontrollers and embedded systems for over 20 years.

Professor at Beihang University, dedicated to promoting microcontrollers and embedded systems for over 20 years.

- LED chemical incompatibility test to see which chemicals LEDs can be used with

- Application of ARM9 hardware coprocessor on WinCE embedded motherboard

- What are the key points for selecting rotor flowmeter?

- LM317 high power charger circuit

- A brief analysis of Embest's application and development of embedded medical devices

- Single-phase RC protection circuit

- stm32 PVD programmable voltage monitor

- Introduction and measurement of edge trigger and level trigger of 51 single chip microcomputer

- Improved design of Linux system software shell protection technology

- What to do if the ABB robot protection device stops

- Huawei's Strategic Department Director Gai Gang: The cumulative installed base of open source Euler operating system exceeds 10 million sets

- Download from the Internet--ARM Getting Started Notes

- Learn ARM development(22)

- Learn ARM development(21)

- Learn ARM development(20)

- Learn ARM development(19)

- Learn ARM development(14)

- Learn ARM development(15)

- Analysis of the application of several common contact parts in high-voltage connectors of new energy vehicles

- Wiring harness durability test and contact voltage drop test method

- To drive a 24V5A motor, what current should the freewheeling diode have?

- CC2640R2F supports Alibaba Cloud Link IoT platform

- Some understanding of MSP430 usage

- 【HomeBao】Supplementary experiment for project submission: Connecting HomeBao to HomeAssistant

- 1. Unpacking and running the Helloworld example

- 【Repost】Thirty Practical Experiences in Switching Power Supply Design (Part 1)

- blue_nrg, how to turn off subscription function

- CC26xx product model and suffix description

- AD19, board layer, layer type, what are the uses of each? Please guide

- Melexis for you: Detailed explanation of the implementation and technical support of functional safety in semiconductor R&D. Registration for the prize-winning live broadcast is open!

5962-9679801VXA

5962-9679801VXA

京公网安备 11010802033920号

京公网安备 11010802033920号