STM32 Watchdog Summary I have been adjusting the development board of Atom Brother for more than a year, and it is basically usable, but I still don't understand the working mechanism of some basic peripherals of STM32. I would like to take this summer vacation opportunity to make a brief summary of the functions of each peripheral, to improve my basic knowledge while providing some reference for other students. Let’s first look at the content of the guard dog part. The most difficult to understand part of the watchdog is the window watchdog, among which the window value setting and how to trigger a reset are even more difficult to understand. Therefore, we will analyze the working principle of the window watchdog from the fundamental point of view, and skip the interrupts related to it. stm32 has two watchdogs, independent watchdog and window watchdog. In fact, the functions of the two are similar, but the limit time of feeding the watchdog is different. The independent watchdog has its own independent 40Khz clock, and there is no enabling problem; while the window watchdog uses the PCLK1 clock, and the clock needs to be enabled first. The following is a detailed description of the watchdog: ①, Independent watchdog limits the feeding time to 0-x, where x is determined by your related registers. The feeding time cannot be too late. ②, Window watchdog, so it is called window because its feeding time is within a range of upper and lower limits. You can set the upper and lower limits by setting the relevant registers. The feeding time should not be too early or too late. Obviously, the independent watchdog is simpler and easier to understand. Here, the detailed meaning of the window watchdog is mainly explained.

The upper window of the watchdog is W[6:0] set in the configuration register WWDG->CFR; the lower window is 0x40; when the counter of the window watchdog is outside the upper window or is lower than the lower window value, a reset will occur. As shown in the figure above, when the counter value decreases to 0x3f and the dog is not fed within the counting time, a reset will be triggered; secondly, if the dog is fed before the counter value decreases to W[6:0] set in the configuration register WWDG->CFR, a reset will also be triggered. Therefore, when using a window watchdog, two values must be set, one is the upper window value of the window watchdog, that is, W[6:0] set in the configuration register WWDG->CFR, and the other is the initial count value of the decrement counter. Combined with the logical relationship in the above figure, let's analyze it: As shown in the figure, ①③ represents AND gates, and ② represents NOT-OR gates; 1. When T[6:0]>W[6:0], the comparator output value is 1. If WWDG_CR is reloaded at this time, ③ will output 1, and the output of ② must also be 1. Because the window watchdog is enabled, the 7th bit WDGA of WWDG_CR is also 1, that is, the output of AND gate ① is 1, which triggers a reset. In simple terms, when the down counter value is fed to the dog (i.e., reload WWDG_CR) before it decreases to the upper window value W[6:0], the watchdog reset will be triggered. 2. When the 6th bit of T[6:0] becomes 0, that is, the value of T[6:0] becomes 0x3f, then the output of ② must be 1, and WDGA is also 1, so the output of ① is 1, which triggers the watchdog reset. To put it simply, when the value of the down counter reaches 0x3f and the dog is not fed (that is, reload WWDG_CR), the watchdog reset will also be triggered. The value of the upper window can only be set. The maximum value of the 7-bit binary number can only be set to 127 (0x7f), and the minimum value must be greater than 0x40 of the lower window, so its value range is 64~127 (0x40~0x7f), otherwise the window cannot be guaranteed. The two bits [8:7] in the configuration register WWDG->CFR register are set to set the clock division factor for the counter, determine the time range that the counter can be timed, and thus determine the time range of the window.

The clock of the window watchdog comes from PCLK1. In the clock configuration, its frequency is the two-frequency clock of the external clock after the multiplier, that is, 36Mhz, as shown in the STM32 clock tree in the figure above. The timeout formula of the window watchdog is as follows:

The minimum and maximum timeout table of the window watchdog under the 36M clock:

The specific calculation of the data in the table is as follows: ①. When T[5:0] are all 0, the value of the 7-bit counter is 0x40. At this time, the distance to the reset value can only be counted once. The dog feeding operation must be performed within this time, otherwise a reset is triggered. Thus, we can know the minimum timeout time under each WDDTB value, such as when WDDTB=0, Twwdg=4096×2^0×1/36 (us)=113 us. The minimum timeout time under other WDDTB values can be calculated in turn. ②. When T[5:0] are all 1, the value of the 7-bit counter is 0x7f. At this time, the counter is counted down 0x40 times (0x3f+1) from the reset value. Feeding the dog within this time can avoid reset. Thus, we can know the maximum timeout time under each WDDTB value, such as when WDDTB=0, Twwdg=4096×2^0×64/36 (us)=7281.7 us. The maximum timeout under other WDDTB values can be calculated in turn.

The STM32 series CPU has up to 8 timers, of which TIM1 and TIM8 are advanced timers that can generate three pairs of PWM complementary outputs, commonly used to drive three-phase motors, and their clocks are generated by the output of APB2. The other 6 are ordinary timers, and their clocks are generated by the output of APB1. Definition of general timer: The general timer of STM32 is composed of a 16-bit automatic reload counter (CNT) driven by a programmable prescaler (PSC). Function: The general timer of STM32 can be used to measure the pulse length of the input signal (input capture) or generate output waveform (output comparison and PWM), etc. Frequency division coefficient: determines the time base of the timer, that is, the minimum timing time. Timer clock source: As can be seen from the figure, the timer clock does not come directly from APB1 or APB2, but from a frequency multiplier whose input is APB1 or APB2. When the pre-scaling factor of APB1 is 1, this frequency multiplier does not work, and the clock frequency of the timer is equal to the frequency of APB1; when the pre-scaling factor of APB1 is other values (that is, the pre-scaling factor is 2, 4, 8 or 16), this frequency multiplier works, and the clock frequency of the timer is equal to twice the frequency of APB1.

Let's take an example to illustrate. Assuming AHB = 36MHz, since the maximum frequency allowed by APB1 is 36MHz, the pre-scaling coefficient of APB1 can take any value; When the pre-scaling factor = 1, APB1 = 36MHz, the clock frequency of TIM2~7 = 36MHz (the multiplier does not work); When the pre-division coefficient = 2, APB1 = 18MHz. Under the action of the frequency multiplier, the clock frequency of TIM2~7 = 36MHz. Since APB1 not only provides clocks for general-purpose timers but also provides clocks for other peripherals, the flexibility of the APB1 rescaler design is also reflected

When assigning values to the auto-reload register, the size of TIM_Period actually means that an update or interrupt will occur after TIM_Period counts. The setting of TIM_Prescaler directly determines the clock frequency of the timer. In layman's terms, it is how many times it can count in one second. For example, if the calculated clock frequency is 2000, it will count 2000 times in one second. If TIM_Period is set to 4000 at this time, it will interrupt once after 4000 counts. Since the clock frequency is 2000 counts per second, it will interrupt once in just 2 seconds. The time when the interrupt occurs = (TIM_Prescaler+1)* (TIM_Period+1)/FLK. It is also important to note that once entering the interrupt service routine, the first step is to clear the interrupt flag so that the next interrupt service function can be executed smoothly. Note: Of course, the counting mode of the counter is relatively simple and is not described in detail here. |

Today a classmate asked me how PWM works? Why is it like this? Why? I was confused by the question. So today I will summarize some general timers to generate PWM output.

①. PWM mainly controls frequency and duty cycle: these two factors are controlled by two registers: TIMX_ARR and TIMX_CCRX. The ARR register is an automatic reload register, that is, the counter will be cleared to zero after recording this number and then start counting again, so the frequency of PWM is tim_frequency/(TIMX_ARR-1). When counting, it will be constantly compared with the data in the CCRX register. If it is less than, it is a high level or a low level. If the count value is greater than the CCRX value, the level polarity is reversed. So this also controls the duty cycle.

②、The data in TIM3-CNT counts from 0 to the value in ARR. When the count reaches the data size received by TIM3_CCRx, it changes from high level to low level. When the value in CNT increases to the value set in the ARR register, it is automatically cleared, and counts again from 0, and generates a count overflow event. The time from counting 0 to the ARR value is the PWM cycle. Setting the value of CCRx is used to change the duty cycle of PWM.

③. The value of TIM3-CNT is automatically compared with the data in TIM3_CCRx. When the value of TIM3-CNT is equal to the data in TIM3_CCRx, PWM automatically jumps. This process is implemented by hardware. There is no code for comparing the two in the routine of the Atomic Development Board, so don’t ask how it is implemented in the software, because I haven’t found it for a long time.

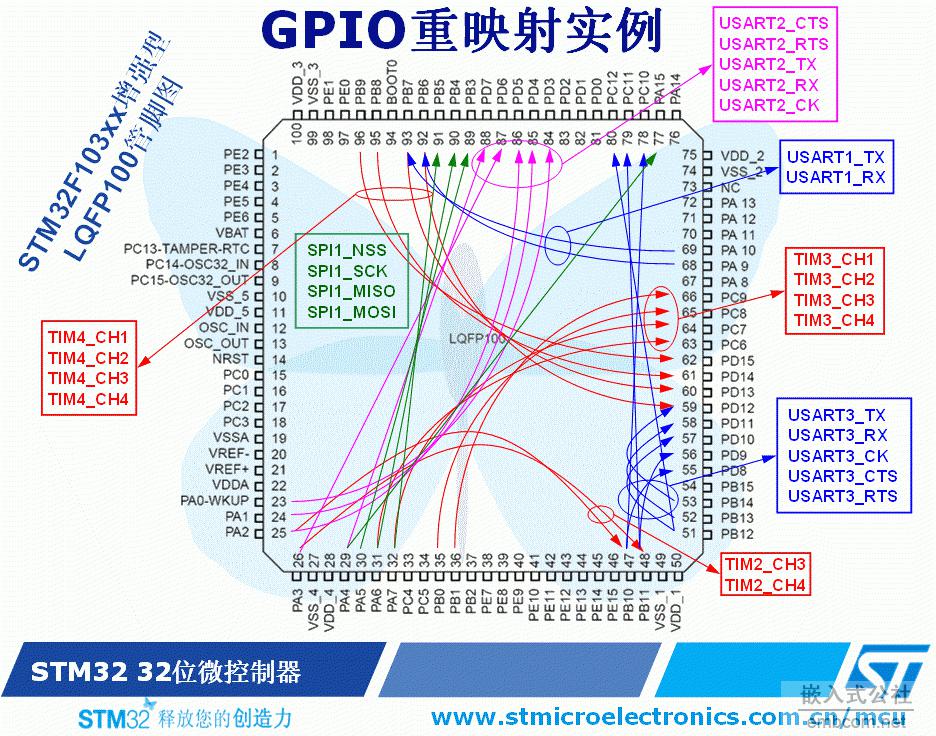

④Port remapping

To optimize the number of peripherals in a 64-pin or 100-pin package, some multiplexed functions can be remapped to other pins. Set the multiplexed remapping and debug I/O configuration register (AFIO_MAPR) to achieve pin remapping. At this time, the multiplexed functions are no longer mapped to their original assignments. (Note: The redefined pins are fixed, and you cannot remap them to any pin you want! Remapping is generally only applicable to 100- and 144-pin packages! (It depends on which peripheral)).

There are many I/O ports on STM32, and there are also many built-in peripherals such as I2C, ADC, ISP, USART, etc. In order to save lead pins, these built-in peripherals basically share pins with I/O ports, that is, the multiplexing function of I/O pins. However, STM32 has another special feature: many I/O pins of multiplexed built-in peripherals can be led out from different I/O pins through the remapping function, that is, the pins of the multiplexing function can be changed through the program. But these remappings are not arbitrary, only some pins can be remapped. The specific pins are listed in the GPIO and AFIO chapters of the STM32 reference manual. Generally, the pins of digital systems such as timers and communication interfaces can be remapped, but those related to analog quantities such as adc, dac, and clocks cannot be remapped.

Simply put, STM32's IO has three functions: one is the default, one is multiplexing, and one is the remapping function (this actually also belongs to multiplexing). If it is configured for multiplexing, the second function will be used. If it is configured for multiplexing and the corresponding remapping is also configured, the third function will be used.

Some remapping examples of STM32:

Input capture experiment

How is the capture achieved? How does it relate to the timer? Why can it be captured?

Preconceived: The timer can be used to capture the high-level pulse width of certain IO ports, and the pulse width time can be obtained through serial port printing.

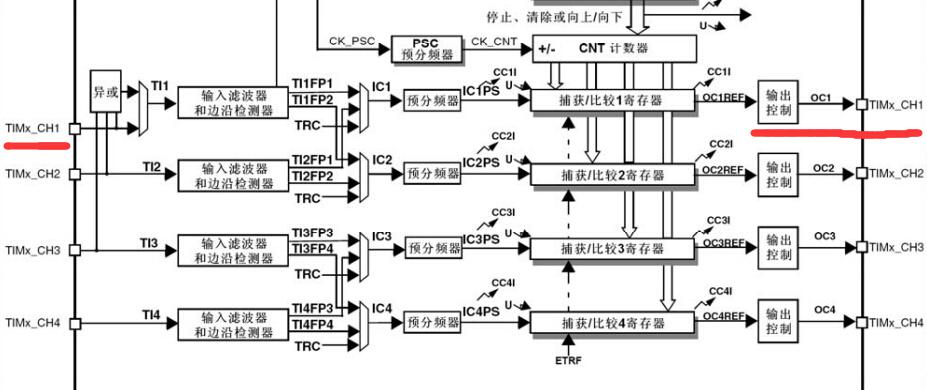

Input capture mode can be used to measure pulse width or frequency. Except for TIM6 and TIM7, all other STM32 timers have input capture function. Simply put, STM32 input capture detects the edge signal on TIMx_CHx. When the edge signal changes (such as rising edge/falling edge), the current timer value is stored in the capture/compare register (TIMx_CCRx) of the corresponding channel to complete a capture.

Understanding of capture mode and comparison mode:

The principle of capture mode is that when the selected input pin has the selected pulse trigger edge, the count value TIMx_CNT of the timer at that moment will be saved and an interrupt will be generated (the value of TIMx_CNT will not be compared with anything). The most common use of this function is to measure the pulse width of an external pulse.

The principle of compare mode is that when the value set in the CCRx register is equal to the timer counter value, the level of the relevant pin changes and an interrupt is generated. This function is often used to generate a PWM waveform with a certain pulse width.

The digital filter consists of an event counter, which will generate an output jump after recording N events: The value of this N can be found in the Chinese manual, which means: I sample a high level, and only if N consecutive high levels are sampled will I consider it a valid high level. If it is less than N, I will consider it invalid.

PWM input capture mode is a special case of input capture mode. You can understand it as follows

1. Each timer has four input capture channels IC1, IC2, IC3, and IC4. IC1 and IC2 form a group, and IC3 and IC4 form a group. And the corresponding relationship between the pins and registers can be set.

2. Two ICx signals are mapped to the same TIx input.

3. The two ICx signals are valid on opposite polarity edges.

4. One of the two edge signals is selected as the trigger signal and the slave mode controller is set to reset mode.

5. When the trigger signal comes, the capture register set to trigger the input signal captures "one PWM cycle (that is, two consecutive rising or falling edges)", which is equal to the number of TIM clock cycles (that is, the number of TIM counts n captured in the capture register).

6. Similarly, another capture channel captures the trigger signal and the count number m of the next edge signal of the opposite polarity, that is, (i.e., the high level cycle or the low level cycle)

7. From this, we can calculate the clock period and duty cycle of PWM

frequency=f(TIM clock frequency)/n.

duty cycle = (number of high level counts/n),

If m is the number of high level counts, then duty cycle = m/n

If m is the number of low-level counts, then duty cycle = (nm)/n

Note: Because the counter is 16 bits, the maximum number of counts in one cycle is 65535, so the measured minimum frequency = TIM clock frequency/65535.

Understanding of pulse width measurement:

The principle of input capture is that the timer counts normally, and when an external pulse arrives, the timer count value is stored. When the next pulse arrives, the difference between the two count values is calculated, which is the period of the two pulses. For example, the timer counts to 10, an external pulse arrives, and last_time_CH1 is used to store 10. When the next pulse arrives, the timer counts to 110, and this_time_CH1 is used to store 110. After that, the difference is made, and tmp16_CH1 stores the difference of 100. Since the timer runs at 100KHZ, the count value increases once every 10us, so the pulse period is 100*10=1000us=1ms, which is 1KHZ. Of course, the timer will overflow and reload, and the difference compensation operation needs to be performed at this time, tmp16_CH1 = ((0xFFFF - last_time_CH1) + this_time_CH1); the measurable range depends on the frequency of the timer. If the external frequency is so slow that the timer is not triggered twice after counting for a whole week, an overflow will occur, and the count value is no longer accurate. Therefore, the timer clock configuration depends on the external pulse frequency and should be configured properly so that the pulse frequency range does not overflow. Since each external pulse will trigger an interrupt, especially when there are four channels, using the interrupt method will slightly occupy CPU resources. Using DMA can solve this problem.

After obtaining the pulse period, the external frequency can be obtained through calculation and then the speed can be measured.

STM32 ADC sampling (see online content summary) Difficulty: How to determine the sampling period? How to configure the relevant registers? Where does the 12.5 in the conversion time come from? 1. Basic concepts: ADC conversion is the conversion of analog input signals into digital quantities by the microcontroller. To read the digital quantity, you must wait until the conversion is completed. The completion of a channel reading is called the sampling cycle. The sampling cycle is generally = conversion time + reading time. And the conversion time = sampling time + 12.5 clock cycles. The sampling time is the time you tell the STM32 to sample the analog quantity through the register. The longer the setting, the more accurate it is.

IO corresponding to each channel of the STM32 ADC module (Note: The STM32F103 series has at least 2 ADCs, and the STM32F103ZET6 contains 3 ADCs. The STM32F103ZET6 integrates a 12-bit successive approximation analog-to-digital converter with up to 18 channels, which can measure 16 external and 2 internal signal sources.)

2. Rule Groups and Injection Groups The ADC channels of STM32 are divided into regular groups and injection groups. Because the ADC conversion module has only one ADC function core, it can support data conversion of so many channels using time-division multiplexing. The purpose of grouping is to give priority to specific ADC channels. For example, ADCx_IN2 is assigned to the rule group, and ADCx_IN3 is assigned to the injection group. During the data conversion process of the IN2 channel, an external signal triggers the conversion of the IN3 channel. The ADC function core will suspend the conversion of IN2 and switch to the conversion of IN3. After the conversion is completed, it will return to the conversion of IN2. It can be seen that the channel of the injection group has the priority conversion right and can interrupt the conversion of the channel of the rule group.

3. Determination of STM32 ADC sampling frequency ①、Programmable channel sampling time The ADC uses several ADC_CLK cycles to sample the input voltage. The number of sampling cycles can be determined by Each channel can be changed by the SMP[2:0] bits in the ADC_SMPR1 and ADC_SMPR2 registers. Different time sampling. The total conversion time is calculated as follows: TCONV = sampling time + 12.5 cycles For example: When ADCCLK=14MHz and sampling time of 1.5 cycles TCONV = 1.5 + 12.5 = 14 cycles = 1μs

Where does the 12.5 in the conversion time come from? Brother Atom told me that ST is dead and we don't need to worry about it.

②、The specific analysis is as follows: (1) Our input signal is 50Hz (cycle is 20ms), and the initial setting is 200 sampling points per cycle (Note: at least 20 points are sampled per cycle, that is, the sampling rate is at least 1k), and the interval between every 2 sampling points is 20ms/200 = 100 us We choose the smallest 1.5 cycles for the ADC programmable channel sampling time, so the ADC sampling cycle is 100us /1.5=66us. ADC clock frequency is 1/66us =15 KHz. The ADC programmable channel sampling time is selected as 71.5 cycles, so the ADC sampling cycle is (100us /71.5). The ADC clock frequency is 7.15MHz.

(2) Next we need to determine the system clock: We use an 8 MHz external crystal oscillator as the clock source (HSE), and it is estimated that after

We provide a dedicated programmable pre-divider for the ADC clock by setting the clock configuration register (RCC_CFGR) and dividing PCLK2 by 8 as the ADC clock. It can be seen that the ADC clock frequency is 9MHz. From the manual, we know: ADC conversion time: STM32F103xx enhanced products: 1μs when ADC clock is 56MHz (1.17μs when ADC clock is 72MHz) (3) From the above analysis, we can see that: it is not quite appropriate. We readjust the above content and propose the following two solutions:

Solution 1: Our input signal is 50Hz (cycle is 20ms), initially set to 2500 sampling points per cycle (Note: at least 20 points are sampled per cycle, that is, the sampling rate is at least 1k), and the interval between every 2 sampling points is 20ms / 2500 = 8 us The ADC programmable channel sampling time is selected as 71.5 cycles, so the ADC sampling cycle is 8us /71.5. The ADC clock frequency is about 9 MHz. Divide PCLK2 by 8 and use it as the ADC clock, then the ADC clock frequency is 9MHz.

Solution 2: Our input signal is 50Hz (cycle is 20ms), and the initial setting is 1000 sampling points per cycle (Note: at least 20 points are sampled per cycle, that is, the sampling rate is at least 1k), and the interval between every 2 sampling points is 20ms/1000= 20 us The ADC programmable channel sampling time is selected as 239.5 cycles, so the ADC sampling cycle is 20us /239.5. The ADC clock frequency is about 12 MHz. |

STM32 DAC Experiment Basic principle: The 12-bit DAC module divides the reference voltage (3.3V) used for measurement into 4095 parts (3.3/4095). By setting the value of the register DAC_DHR12Rx (different alignments correspond to different registers), the output voltage can be obtained. The value is the value in the register multiplied by the value of each part (3.3/4095). The result is the desired output voltage value. Then we can detect the output voltage value through ADC sampling and display it on the LCD. Note that the reference voltage setting here is that VREF+ is connected to 3.3V and VREF- is connected to 0V. In addition, the DAC output is directly controlled by the DORx register, but data cannot be written directly to the DORx register. Instead, it is indirectly transmitted to the DORx register through DHRx to achieve control of the DAC output.

|

1. GPIO mode configuration

1. Input/output mode (refer to the STM32 manual)

2. In GPIO output mode, the difference between several speeds:

(1). GPIO pin speed: GPIO_Speed_2MHz (10MHz, 50MHz);

also known as the response speed of the output driver circuit: (The chip has arranged multiple output driver circuits with different response speeds in the output part of the I/O port. Users can choose the appropriate driver circuit according to their needs and select different output driver modules by selecting the speed to achieve the best noise control and reduce power consumption.)

It can be understood as: The bandwidth of the output driver circuit: that is, the maximum frequency of the signal that a driver circuit can pass without distortion.

(If the frequency of a signal exceeds the response speed of the driver circuit, the signal may be distorted. Distortion factor?)

If the signal frequency is 10MHz, and you configure a bandwidth of 2MHz, the 10MHz square wave is likely to become a sine wave. It is like the design speed of a highway. When the car speed is lower than the design speed, it can run smoothly. If it exceeds the design speed, it will be bumpy or even overturn.

The key is: The GPIO pin speed matches the application. The higher the speed configuration, the greater the noise and the greater the power consumption.

Drivers with high bandwidth and speed consume more power and have more noise, while drivers with low bandwidth consume less power and have less noise. Using a suitable driver can reduce power consumption and noise.

For example: high-frequency drive circuits also have high noise. When a high output frequency is not required, please use a low-frequency drive circuit, which is very helpful to improve the EMI performance of the system. Of course, if you want to output a higher frequency signal, but choose a lower frequency drive module, you may get a distorted output signal. The key is that the GPIO pin speed matches the application (recommended more than 10 times?).

For example:

① USART serial port, if the maximum baud rate is only 115.2k, then a speed of 2M is enough, which is both power-saving and noise-free.

② I2C interface, if you use a 400k baud rate, if you want to leave more margin, you can choose a GPIO pin speed of 10M. ③

SPI interface, if you use an 18M or 9M baud rate, you need to choose a GPIO pin speed of 50M.

(2). The GPIO flip speed refers to the speed at which the 0 and 1 values of the input/output register are reflected on the high and low levels of the external pin (APB2). The manual states that the maximum GPIO flip speed can reach 18MHz.

@Through a simple program test, the flip time observed with an oscilloscope: is a comprehensive time, including the time to fetch instructions, the time to execute instructions, the time to transfer the signal to the register after the instruction is executed (this may go through many links, such as AHB, APB, bus arbitration, etc.), and finally the time it takes for the signal to be transferred from the register to the pin.

For example: if there is a pull-up resistor, the larger the resistance, the larger the RC delay, that is, the slower the logic level conversion speed and the greater the power consumption.

(3). GPIO output speed: It is related to the program (how long does it take to output a signal in the program).

2. When the GPIO port is set to input, the output drive circuit is disconnected from the port, so the output speed configuration is meaningless.

3. During reset and just after reset, the multiplexing function is not enabled, and the I/O port is configured as floating input mode.

4. All ports have external interrupt capability. In order to use the external interrupt line, the port must be configured as input mode.

5. The configuration of the GPIO port has a locking function. After the GPIO port is configured, the configuration combination can be locked by the program until the next chip reset to unlock.

General application:

analog input_AIN - apply ADC analog input, or save power under low power consumption.

Floating input_IN_FLOATING - can be used for KEY identification, RX1

open drain output_Out_OD - applied to I2C bus; (STM32 open drain output can only output 0 if no pull-up resistor is connected externally)

2. Pin multiplexing function remapping

1. Multiplexing function: built-in peripherals share the lead pins with I/O ports (different functions correspond to the same pin)

The external pins of all built-in peripherals of STM32 are multiplexed with standard GPIO pins. If there are multiple multiplexing function modules corresponding to the same pin, only one of them can be enabled, and the other modules remain disabled.

2. Remapping function: The lead pins of the multiplexing function can be led out from different I/O pins through remapping, that is, the lead pins of the multiplexing function can be changed to other pins through the program!

Direct benefit: PCB designers can connect certain signals without having to make a big circle on the board when necessary, which facilitates PCB design and potentially reduces signal cross-interference.

For example: USART1: 0: No re-imaging (TX/PA9, RX/PA10); 1: Re-imaging (TX/PB6, RX/PB7).

(Refer to the introduction of AFIO_MAPR register) [0,1 is the bit value of a register]

[Note] The pinouts of the following multiplexed functions have the remapping function:

- The pins of the crystal oscillator can be used as ordinary I/O ports when no crystal is connected

- CAN module; - JTAG debug interface; - The pinout interfaces of most timers; - Most USART pinout interfaces

- The pinout interface of I2C1; - The pinout interface of SPI1;

For example: for STM32F103VBT6, pin 47 is PB10, and its multiplexed functions are I2C2_SCL and USART3_TX, which means that its default function after power-on is PB10, and the SCL of I2C2 and the TX of USART3 are its multiplexed functions; in addition, after the pin of TIM2 is remapped, TIM2_CH3 also becomes the multiplexed function of this pin.

(1) To use the USART3 function of pins 47 and 48 of STM32F103VBT6, you need to configure pin 47 as multiplexed push-pull output or multiplexed open-drain output, configure pin 48 as a certain input mode, enable USART3 and keep I2C2 in the disabled state.

(2) To use pin 47 of STM32F103VBT6 as TIM2_CH3, you need to remap TIM2 and then configure the corresponding pins according to the multiplexed function.

Previous article:Summary of the watchdog experiment of STM32F107

Next article:STM32 ADC example (based on DMA)

Recommended ReadingLatest update time:2024-11-16 18:01

- Popular Resources

- Popular amplifiers

Professor at Beihang University, dedicated to promoting microcontrollers and embedded systems for over 20 years.

Professor at Beihang University, dedicated to promoting microcontrollers and embedded systems for over 20 years.

- Innolux's intelligent steer-by-wire solution makes cars smarter and safer

- 8051 MCU - Parity Check

- How to efficiently balance the sensitivity of tactile sensing interfaces

- What should I do if the servo motor shakes? What causes the servo motor to shake quickly?

- 【Brushless Motor】Analysis of three-phase BLDC motor and sharing of two popular development boards

- Midea Industrial Technology's subsidiaries Clou Electronics and Hekang New Energy jointly appeared at the Munich Battery Energy Storage Exhibition and Solar Energy Exhibition

- Guoxin Sichen | Application of ferroelectric memory PB85RS2MC in power battery management, with a capacity of 2M

- Analysis of common faults of frequency converter

- In a head-on competition with Qualcomm, what kind of cockpit products has Intel come up with?

- Dalian Rongke's all-vanadium liquid flow battery energy storage equipment industrialization project has entered the sprint stage before production

- Allegro MicroSystems Introduces Advanced Magnetic and Inductive Position Sensing Solutions at Electronica 2024

- Car key in the left hand, liveness detection radar in the right hand, UWB is imperative for cars!

- After a decade of rapid development, domestic CIS has entered the market

- Aegis Dagger Battery + Thor EM-i Super Hybrid, Geely New Energy has thrown out two "king bombs"

- A brief discussion on functional safety - fault, error, and failure

- In the smart car 2.0 cycle, these core industry chains are facing major opportunities!

- The United States and Japan are developing new batteries. CATL faces challenges? How should China's new energy battery industry respond?

- Murata launches high-precision 6-axis inertial sensor for automobiles

- Ford patents pre-charge alarm to help save costs and respond to emergencies

- New real-time microcontroller system from Texas Instruments enables smarter processing in automotive and industrial applications

- I am a novice and would like to ask the experts how to adjust the minimum spacing in Altium Designer

- What are the factors that affect the power consumption of microcontrollers?

- GigaDevice GD32 MCU Design Competition Selected Works Album (Limited Time Free Points Download)

- Share the production of a wireless remote control car

- Review of the 2019 National Electronic Design Competition - The small plane I made

- 【GD32F310G-START】USART indefinite length reception

- Discussion on simple polymer lithium battery charging and discharging circuit. Please give me your valuable advice.

- Difference between TMS320C6713 and TMS320C6713B

- [TI recommended course] #DC/DC switching regulator packaging innovation#

- Renesas CPK-RA2L1 development board first step development environment construction

.

.

usb_host_device_code

usb_host_device_code Transplantation of real-time operating system RT-ThreadSmart on STM32MP1

Transplantation of real-time operating system RT-ThreadSmart on STM32MP1

京公网安备 11010802033920号

京公网安备 11010802033920号