TFT screen

- supports monochrome, 4-level grayscale, 256-color palette display mode

- supports 64K and 16M color non-palette display mode

- supports LCD with resolution of 640*480, 320*240 and other specifications

For controlling the TFT screen, in addition to sending it video data (VD[23:0]), the following signals are indispensable, namely:

VSYNC (VFRAME): frame synchronization signal

HSYNC (VLINE): line synchronization signal

VCLK: pixel clock signal

VDEN (VM): data valid flag signal

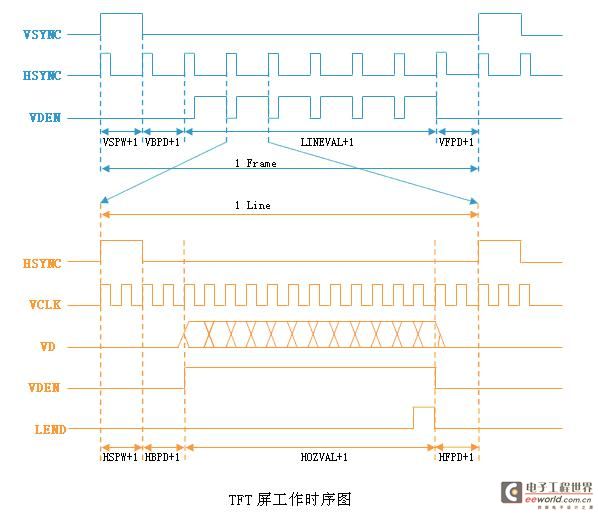

General TFT screen working sequence

External pin signal:

VSYNC: vertical synchronization signal, indicating the start of scanning 1 frame.

HSYNC: horizontal synchronization signal, indicating the start of scanning 1 line.

VDEN: data enable signal.

VD[23:0]: LCD pixel data output port.

VCLK: pixel clock signal.

Register parameters:

VSPW: Pulse width of vertical synchronization signal, unit is 1 line time.

VFPD: Front shoulder of vertical synchronization signal, unit is 1 line time.

VBPD: Back shoulder of vertical synchronization signal, unit is 1 line time.

LINEVAL: Vertical display size - 1, that is, screen line width - 1.

HBPD: Back shoulder of horizontal synchronization signal, unit is 1VCLK time.

HFPD: Front shoulder of horizontal synchronization signal, unit is 1VCLK time.

HSPW: Pulse width of horizontal synchronization signal, unit is 1VCLK time.

HOZVAL: Horizontal display size - 1, that is, screen column width - 1.

As can be seen from the above figure:

The time required to scan one frame:

=((VSPW+1)+(VBPD+1)+(LINEVAL+1)+(VFPD+1)) line time.

The time required to scan a line:

= ((HSPW+1)+(HSPD+1)+(HFPD+1)+ (HOZVAL+1)) VCLK time.

And one VCLK time is determined by the CLKVAL in the LCD register LCDCON1:

=HCLK/[2*(CLKVAL+1)]

Therefore, the time required to scan a frame:

T=[(VSPW+1)+(VBPD+1)+(LINEVAL+1)+(VFPD+1)]* [(HSPW+1)+(HSPD+1)+(HFPD+1)+ (HOZVAL+1)]* HCLK/[2*(CLKVAL+1)]

That is, the frame frequency is: 1/T

To use LCD correctly, you must pay attention to two points: 1. Timing; 2. Display buffer.

1. Timing

LCD generally requires three timing signals: VSYNC, HSYNC and VCLK. VSYNC is the vertical synchronization signal. Before each frame (i.e., a screen) is scanned, the signal is valid once. The field frequency of the LCD can be determined by this signal, that is, the number of times the screen is refreshed per second (in Hz). HSYNC is the horizontal synchronization signal. Before each line is scanned, the signal is valid once. The line frequency of the LCD can be determined by this signal, that is, the number of times the screen scans a line from left to right per second (in Hz). VCLK is the pixel clock signal. The

clock source for the s3c2440 to process the LCD is HCLK. The VCLK frequency can be adjusted through the CLKVAL in the register LCDCON1. Its formula is:

VCLK=HCLK÷[(CLKVAL+1)×2]

For example, if the frequency of HCLK is 100MHz, to drive an LCD screen with a pixel clock signal of 6.4MHz, the CLKVAL value is calculated by the above formula. The result is CLKVAL is 6.8. After rounding (the value is 6), it can be placed in the corresponding position in the register LCDCON1. Since CLKVAL is rounded, we substitute the rounded value into the above formula and recalculate VCLK to get VCLK = 7.1MHz.

In theory, for an LCD screen of known size (i.e., the horizontal display size HOZVAL and the vertical display size LINEVAL are known), as long as the VCLK value is determined, the line frequency and field frequency should be known. But this is not enough, because in each frame clock signal, there will be some clocks that are not related to the screen display, which brings certain complexity to the determination of the line frequency and field frequency. For example, in the HSYNC signal, the horizontal synchronization signal front shoulder (HFPD) and the horizontal synchronization signal back shoulder (HBPD) will appear successively, and in the VSYNC signal, the vertical synchronization signal front shoulder (VFPD) and the vertical synchronization signal back shoulder (VBPD) will appear successively. In these signal timings, there will be no valid pixel signals. In addition, when the HSYNC and VSYNC signals are valid, their levels must be maintained for a certain period of time, which are called the horizontal synchronization signal pulse width HSPW and the vertical synchronization signal pulse width VSPW respectively. There can be no pixel signals during this period. Therefore, these signals must be included when calculating the line frequency and field frequency. The unit of HBPD, HFPD and HSPW is the time of one VCLK, while the unit of VSPW, VFPD and VBPD is the time used to scan a line. In s3c2440, all these signals (VSPW, VFPD, VBPD, LINEVAL, HBPD, HFPD, HSPW and HOZVAL) are the result of actual value minus 1. These values are configured through registers LCDCON2, LCDCON3 and LCDCON4. Just configure these values to be consistent with the data of the relevant content in the LCD to be driven. For example, the size of the LCD screen we want to display is 320×240, so HOZVAL=320-1, LINEVAL=240-1. The pulse width, front shoulder and back shoulder of the horizontal synchronization signal are 30, 20 and 38 respectively, then HSPW=30-1, HFPD=20-1, HBPD=38-1; the pulse width, front shoulder and back shoulder of the vertical synchronization signal are 3, 12 and 15 respectively, then VSPW=3-1, VFPD=12-1, VBPD=15-1.

Let's calculate the line frequency (HSF) and field frequency (VSF) in detail:

HSF = VCLK ÷ [(HSPW + 1) + (HSPD + 1) + (HFPD + 1) + (HOZVAL + 1)]

= 7.1 ÷ 408 = 17.5kHz

VSF = HSF ÷ [(VSPW + 1) + (VBPD + 1) + (VFPD + 1) + (LINEVAL + 1)]

= 17.5 ÷ 270 = 64.8Hz

In some cases, the default polarity of the LCD clock signal of the s3c2440 is opposite to the polarity of the controlled LCD clock signal. In this case, the polarity of some clock signals can be changed through the relevant bits of the register LCDCON5.

2. Display buffer area

As long as the data to be displayed is placed in the display buffer, the content can be displayed on the screen. This buffer is a memory area that we open up when programming. Generally, we open up this space by defining a two-dimensional array of the same size as the screen, so that it is more convenient to control the screen content. For example, when the screen size is 320×240, the buffer can be defined as LCD_BUFFER[240][320]. Since s3c2440 supports 16-bit and 24-bit non-palette true color TFT LCD modes, and the 24-bit color mode is represented by 32-bit data, the data type of the two-dimensional data defined above should be half-word integer or full-word integer. For example, in the 24-bit color mode, if we want to set a white pixel in the center of the 320×240 screen, then: LCD_BUFFER[120][160] = 0xffffffff.

In s3c2440, registers LCDSADDR1 and LCDSADDR2 are used to set the display buffer, that is, to tell s3c2440 the two-dimensional array we defined. The 9-bit data of LCDBANK specifies the BANK of the LCD, that is, the 30th to 22nd address of the display buffer; the 21-bit data of LCDBASEU specifies the base address of the LCD, that is, the 21st to 1st bit of the start address of the display buffer; the 21-bit data of LCDBASEL specifies the tail address of the LCD, that is, the 21st to 1st bit of the end address of the display buffer. For example, if we want to display 24-bit color on a screen with a size of 320×240, the display buffer array defined is LCD_BUFFER[240][320], then LCDBANK is equal to the data value from the 30th to the 22nd bit of LCD_BUFFER (because LCD_BUFFER represents the first address of the array), LCDBASEU is equal to the data value from the 21st to the 1st bit of LCD_BUFFER, because 32-bit data is used to represent 24-bit color, so each pixel value is 4 bytes, so LCDBASEL is equal to the data value from the 21st to the 1st bit of the result of (LCD_BUFFER + (240×320×4)). In addition, the register LCDSADDR3 has two contents: OFFSIZE and PAGEWIDTH. OFFSIZE is used for the offset length of the virtual screen. If we do not use the virtual screen, set it to 0; PAGEWIDTH defines the width of the viewport in half words. For example, in the above example, PAGEWIDTH should be 320×32÷16.

Previous article:S3C2440 drives 4.3-inch TFT screen program

Next article:Some details of the differences between s3c2410 and s3c2440

Recommended ReadingLatest update time:2024-11-16 22:47

Professor at Beihang University, dedicated to promoting microcontrollers and embedded systems for over 20 years.

Professor at Beihang University, dedicated to promoting microcontrollers and embedded systems for over 20 years.

- Innolux's intelligent steer-by-wire solution makes cars smarter and safer

- 8051 MCU - Parity Check

- How to efficiently balance the sensitivity of tactile sensing interfaces

- What should I do if the servo motor shakes? What causes the servo motor to shake quickly?

- 【Brushless Motor】Analysis of three-phase BLDC motor and sharing of two popular development boards

- Midea Industrial Technology's subsidiaries Clou Electronics and Hekang New Energy jointly appeared at the Munich Battery Energy Storage Exhibition and Solar Energy Exhibition

- Guoxin Sichen | Application of ferroelectric memory PB85RS2MC in power battery management, with a capacity of 2M

- Analysis of common faults of frequency converter

- In a head-on competition with Qualcomm, what kind of cockpit products has Intel come up with?

- Dalian Rongke's all-vanadium liquid flow battery energy storage equipment industrialization project has entered the sprint stage before production

- Allegro MicroSystems Introduces Advanced Magnetic and Inductive Position Sensing Solutions at Electronica 2024

- Car key in the left hand, liveness detection radar in the right hand, UWB is imperative for cars!

- After a decade of rapid development, domestic CIS has entered the market

- Aegis Dagger Battery + Thor EM-i Super Hybrid, Geely New Energy has thrown out two "king bombs"

- A brief discussion on functional safety - fault, error, and failure

- In the smart car 2.0 cycle, these core industry chains are facing major opportunities!

- The United States and Japan are developing new batteries. CATL faces challenges? How should China's new energy battery industry respond?

- Murata launches high-precision 6-axis inertial sensor for automobiles

- Ford patents pre-charge alarm to help save costs and respond to emergencies

- New real-time microcontroller system from Texas Instruments enables smarter processing in automotive and industrial applications

- [RVB2601 creative application development] + voice prompt type environmental status detection recorder

- Research on the information performance advantages of Suruide in-vehicle Ethernet hardware and applications

- [Synopsys IP Resources] Prototyping as a Service (PaaS): Breaking through chip design process bottlenecks and simplifying the path to innovation

- How to write the test bench file for the verliog10 divider

- [Xianji HPM6750 Review] + Environment Setup Test

- EEWORLD University ---- Webinar: Thermal Monitoring and Protection

- How to solve the power supply ripple

- 【AT-START-F425 Review】No.06 Driving Segment LCD

- Today at 10:00 AM Award-winning live broadcast: STMicroelectronics SiC products and industrial application guide

- Gossip negative feedback

mini2440 user manual

mini2440 user manual Design of a portable video display stand based on ARM processor S3C2440A

Design of a portable video display stand based on ARM processor S3C2440A

京公网安备 11010802033920号

京公网安备 11010802033920号