MM58167B is a real-time clock source in a bus-type microprocessing system. It includes an addressable real-time counter, 56-bit on-chip RAM and two output interrupts. The valid signal of the POWER DOWN pin can make the chip enter. Power saving working mode. The chip's time base is a 32.768kHz crystal oscillator. Its features are as follows:

●Compatible with microprocessor (8-bit data bus);

●Has counter from milliseconds to months;

●56-bit internal RAM can be compared with real-time time;

●2 interrupt outputs can generate 8 kinds of interrupt signals;

● The POWER DOWN input can disable all input and output and leave only one STANDBY interrupt;

●Status bit can indicate whether a count update occurs in a read cycle;

●4-year calendar (no leap year);

●24-hour clock;

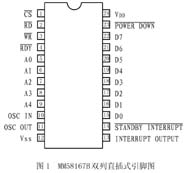

●Adopt 24-pin DIP package (shown in Figure 1).

2. Function module introduction

2.1 Real-time clock counting

Each counter of the real-time clock is divided into two numbers: tens and ones. Each number consists of 4 bits to form a BCD code (see Table 1). Any unused bits maintain logic "0" when reading. ”, is ignored when writing. Any unused bits do not participate in the synthesis of BCD codes. For example, the tens digit of the hour counter should not exceed 2, so only 2 bits are needed to represent it, while the remaining 2 bits are free and represented by a dash (-).

The addressable part of the counter is from milliseconds to months. The counter itself is a pulsation counter, and the pulsation delay is less than 60μs when working above 4.5V (less than 300μs when working at 2.2V).

2.2 On-chip RAM

The 56-bit RAM on-chip can be used as a general data memory, and can also latch the comparison value compared with the real-time clock. An alarm interrupt can be generated whenever the current value of the real-time clock is compared with the set value latched in RAM. Only the units digit of milliseconds and the tens digit of the week are not included in the comparison (they are not used in the counter, as listed in Table 1). If the two most significant bits of a certain BCD code in RAM are set to "1", the bits are considered to be equal and will not participate in the comparison, that is, they will be blocked. Therefore, the rule for setting alarm interrupts is: all bits higher than the specified time unit are set to 0CH (i.e. 1100B, the highest 2 bits are "1"), and bits lower than the specified time unit are set to "00H". For example, if you want an alarm interrupt to occur at 10:15 am every day, the time units higher than hours (week, date, month) are set to 0CH, and the time units lower than minutes (seconds, hundredths of seconds, milliseconds) are set to 0CH. into 00H.

2.3 Interrupts and Comparators

The chip has a total of 2 interrupt outputs. The first is the pin INTERRUPT OUTPUT (outputs a high level when the interrupt is active). This pin is programmed to output 8 types of interrupt signals, namely 10Hz, 1Hz, once per minute, once per hour, once per day, and once per week. An interrupt is generated once, once a month, or when the time set in the on-chip RAM is equal to the clock counter time. In order to enable a certain type of interrupt, just write "1" to the corresponding bit of the interrupt control register. When one or more bits are set to "1" and the counter corresponding to the bit overflows and turns to zero, the interrupt status register will be set. The corresponding bit and generates an interrupt (making the interrupt output pin appear high). As long as the interrupt status register is read, the interrupt type can be identified and the interrupt reset, as shown in Figure 2.

The second interrupt output is the pin STANDBY INTERRUPT (open drain, active low). As long as the time set in the on-chip RAM matches the counter, and the interrupt is enabled (write "1" to the D0 bit at address 16H Allowed, write "0" to disable), the interrupt can be generated.

2.4 Power-saving operating mode

The POWER DONW input pin is actually the second chip select signal. It can disable all inputs and outputs and leave only the STANDBY interrupt. When the pin POWER DOWN inputs a low level, the instrument will not respond to any off-chip signals. It will save the time value and open the STANDBY interrupt (must be programmed before inputting a low level). good). Before VDD switches to backup power or power-saving mode, the POWER DOWN pin should maintain a low level for at least 1μs, and when switching the VDD and POWER DOWN pin states, the levels of all input pins should be within the valid range ( V SS -0.3V~V DD +0.3V).

2.5 Counter and RAM reset and start commands.

Writing FFH to addresses 12H and 13H can reset the counter and on-chip RAM respectively, while the start command (a write pulse for address 15H) will reset 1/1000 seconds and 1/100 seconds. , 1/10 second, second, 10 second counter. This command is used to start the clock accurately. When this command is executed, if the second counter value is greater than 59, the minute counter will increase by 1 immediately, otherwise the minute counter value will not be affected.

2.6 Status bit

The D0 bit at address 14H is a status bit. Whenever a count flip occurs when the counter value is read, the status bit will be set to "1". If the status bit is "1", the count value should be reread. Therefore, each time the counter value is read, the status bit should be read immediately, and the read command will reset the status bit.

2.7 Test mode When

the chip select line and write control line remain low and the address remains at 1FH, the test mode is entered. In this mode, the clock input of the ten millisecond counter is directly connected to 32.768kHz, which allows the counter to operate normally. Count at a higher frequency to achieve the purpose of product debugging. 3. Typical applications Figure 3 shows the application circuit of MM58167B . It should be noted that pins 9 and 10 of MM58167B should be separated by a ground wire to prevent the operation of the crystal oscillator from being interfered by the address line.

Previous article:Principle and application of microprocessor real-time clock chip MM58167B

Next article:Principle and application of microprocessor real-time clock chip MM58167B

Recommended ReadingLatest update time:2024-11-16 20:51

- Popular Resources

- Popular amplifiers

Professor at Beihang University, dedicated to promoting microcontrollers and embedded systems for over 20 years.

Professor at Beihang University, dedicated to promoting microcontrollers and embedded systems for over 20 years.

- Innolux's intelligent steer-by-wire solution makes cars smarter and safer

- 8051 MCU - Parity Check

- How to efficiently balance the sensitivity of tactile sensing interfaces

- What should I do if the servo motor shakes? What causes the servo motor to shake quickly?

- 【Brushless Motor】Analysis of three-phase BLDC motor and sharing of two popular development boards

- Midea Industrial Technology's subsidiaries Clou Electronics and Hekang New Energy jointly appeared at the Munich Battery Energy Storage Exhibition and Solar Energy Exhibition

- Guoxin Sichen | Application of ferroelectric memory PB85RS2MC in power battery management, with a capacity of 2M

- Analysis of common faults of frequency converter

- In a head-on competition with Qualcomm, what kind of cockpit products has Intel come up with?

- Dalian Rongke's all-vanadium liquid flow battery energy storage equipment industrialization project has entered the sprint stage before production

- Allegro MicroSystems Introduces Advanced Magnetic and Inductive Position Sensing Solutions at Electronica 2024

- Car key in the left hand, liveness detection radar in the right hand, UWB is imperative for cars!

- After a decade of rapid development, domestic CIS has entered the market

- Aegis Dagger Battery + Thor EM-i Super Hybrid, Geely New Energy has thrown out two "king bombs"

- A brief discussion on functional safety - fault, error, and failure

- In the smart car 2.0 cycle, these core industry chains are facing major opportunities!

- The United States and Japan are developing new batteries. CATL faces challenges? How should China's new energy battery industry respond?

- Murata launches high-precision 6-axis inertial sensor for automobiles

- Ford patents pre-charge alarm to help save costs and respond to emergencies

- New real-time microcontroller system from Texas Instruments enables smarter processing in automotive and industrial applications

- AC detector

- Selection and application of freewheeling diode

- ESP32 CAM Development with MicroPython

- Challenges 5G Brings to Base Station RF PA Design

- Division circuit

- Android smart wearable device development from entry to mastery pdf download

- Why can't we develop industry software like Matlab?

- Android control LED-2-JNI basis of SinlinxA33 development board

- Free application: Canaan AI new product K510 development kit, RISC-V dual-core CPU @ 800MHZ (with training video)

- Watchdog for C2000-8027 series

Siemens PLC Project Tutorial

Siemens PLC Project Tutorial

京公网安备 11010802033920号

京公网安备 11010802033920号