In the first month of 2000, Professor Sergey Savastiou of Santa Clara University published an article titled "Moore's Law – the Z dimension" in the journal Solid State Technology. The title of the last chapter of this article is Through-Silicon Vias, which is the first time that the term Through-Silicon Via has appeared in the world. The time when this article was published seems to indicate that in the new millennium, TSV is destined to have its extraordinary performance.

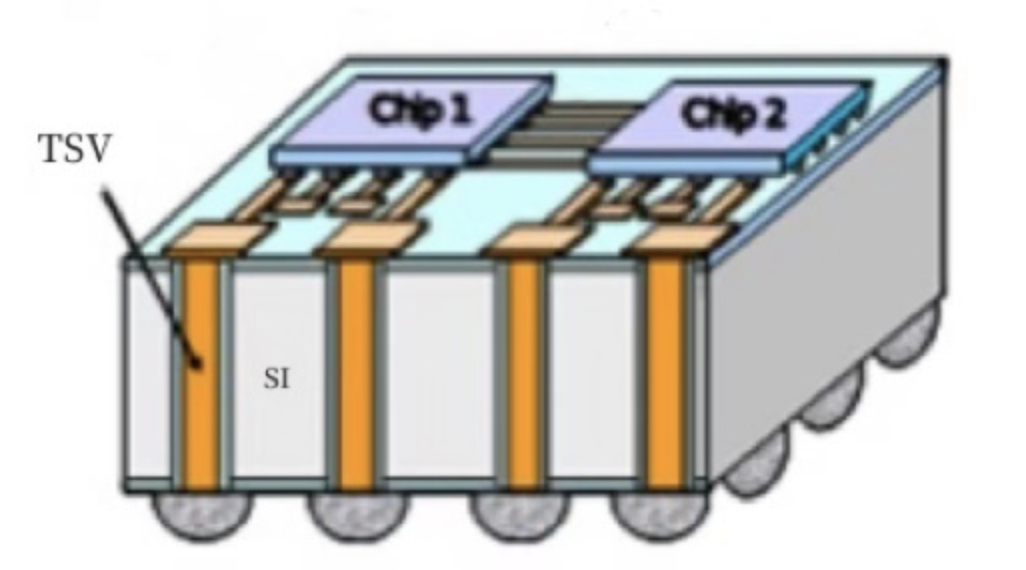

TSV schematic diagram

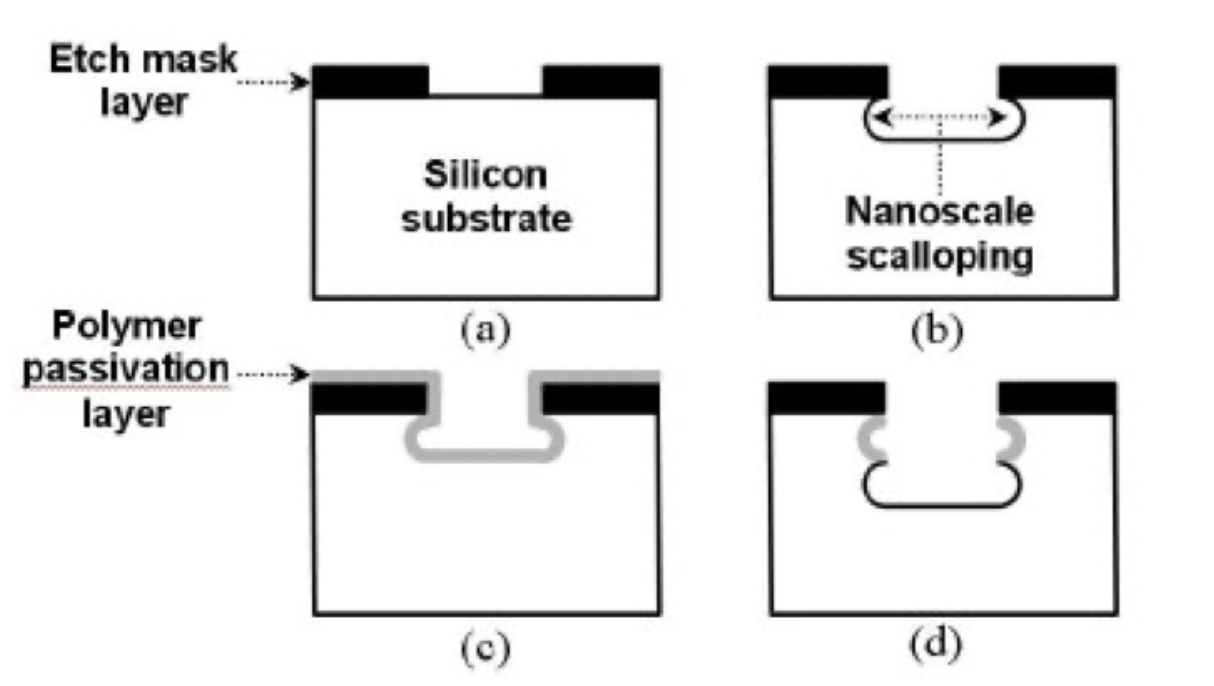

TSV is the abbreviation of Through-Silicon Via, which is a vertical electrical interconnection passing through the silicon substrate.

If wire bonding and flip-chip bumping provide electrical interconnection between the chip and the outside, and RDL (rewiring) provides electrical interconnection in the horizontal direction inside the chip, then TSV provides electrical interconnection in the vertical direction inside the silicon wafer. As the only vertical electrical interconnection technology, TSV is one of the core technologies of advanced semiconductor packaging.

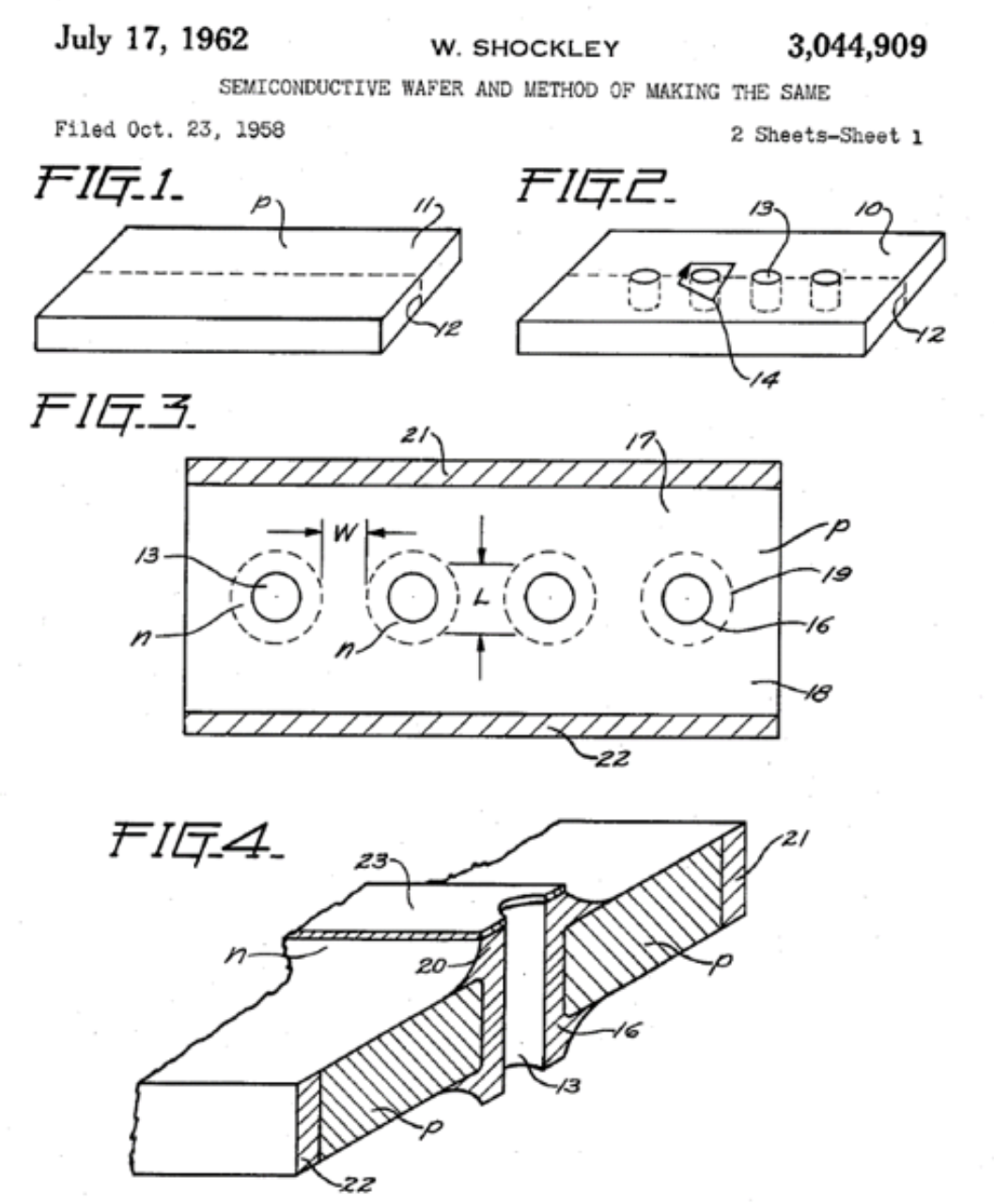

Vertical interconnection was born with integrated circuits

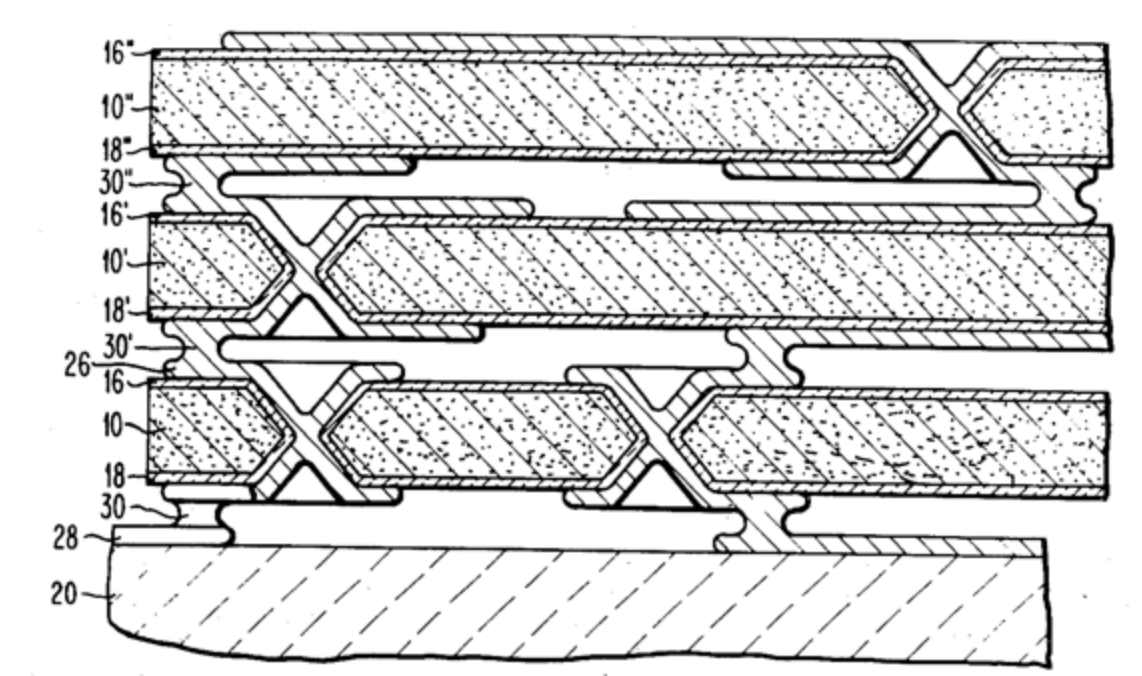

Technological breakthrough

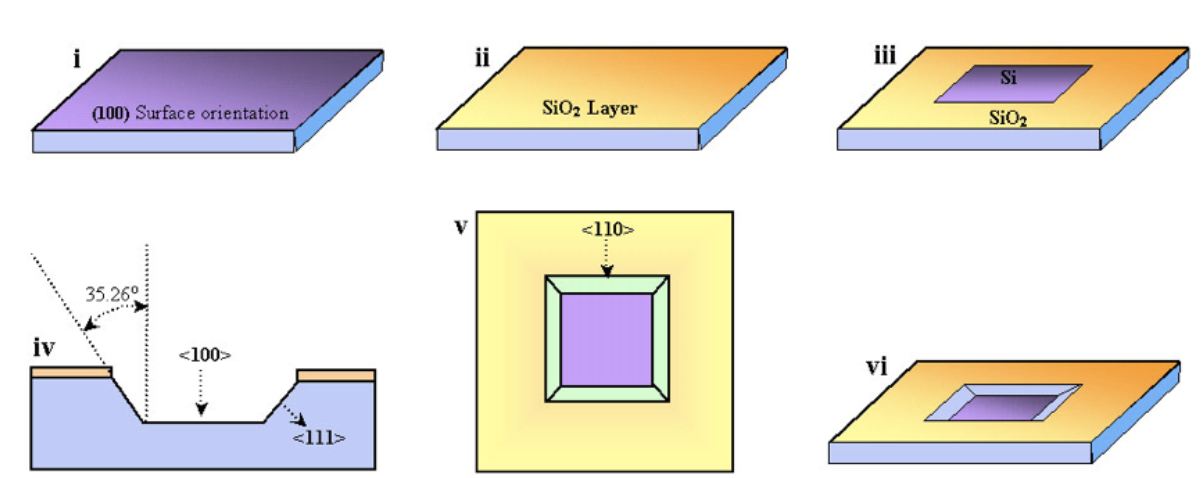

Going commercial

Previous article:Researchers develop wood-derived nanocellulose paper semiconductors

Next article:Researchers can now measure the 'wettability' of graphene and other 2D materials at the molecular level

Recommended ReadingLatest update time:2024-11-16 12:27

- Allegro MicroSystems Introduces Advanced Magnetic and Inductive Position Sensing Solutions at Electronica 2024

- Vietnam's chip packaging and testing business is growing, and supply-side fragmentation is splitting the market

- The US asked TSMC to restrict the export of high-end chips, and the Ministry of Commerce responded

- ASML predicts that its revenue in 2030 will exceed 457 billion yuan! Gross profit margin 56-60%

- ASML provides update on market opportunities at 2024 Investor Day

- It is reported that memory manufacturers are considering using flux-free bonding for HBM4 to further reduce the gap between layers

- Intel China officially releases 2023-2024 Corporate Social Responsibility Report

- Mouser Electronics and Analog Devices Launch New E-Book

- AMD launches second-generation Versal Premium series: FPGA industry's first to support CXL 3.1 and PCIe Gen 6

- Innolux's intelligent steer-by-wire solution makes cars smarter and safer

- 8051 MCU - Parity Check

- How to efficiently balance the sensitivity of tactile sensing interfaces

- What should I do if the servo motor shakes? What causes the servo motor to shake quickly?

- 【Brushless Motor】Analysis of three-phase BLDC motor and sharing of two popular development boards

- Midea Industrial Technology's subsidiaries Clou Electronics and Hekang New Energy jointly appeared at the Munich Battery Energy Storage Exhibition and Solar Energy Exhibition

- Guoxin Sichen | Application of ferroelectric memory PB85RS2MC in power battery management, with a capacity of 2M

- Analysis of common faults of frequency converter

- In a head-on competition with Qualcomm, what kind of cockpit products has Intel come up with?

- Dalian Rongke's all-vanadium liquid flow battery energy storage equipment industrialization project has entered the sprint stage before production

- Allegro MicroSystems Introduces Advanced Magnetic and Inductive Position Sensing Solutions at Electronica 2024

- Car key in the left hand, liveness detection radar in the right hand, UWB is imperative for cars!

- After a decade of rapid development, domestic CIS has entered the market

- Aegis Dagger Battery + Thor EM-i Super Hybrid, Geely New Energy has thrown out two "king bombs"

- A brief discussion on functional safety - fault, error, and failure

- In the smart car 2.0 cycle, these core industry chains are facing major opportunities!

- The United States and Japan are developing new batteries. CATL faces challenges? How should China's new energy battery industry respond?

- Murata launches high-precision 6-axis inertial sensor for automobiles

- Ford patents pre-charge alarm to help save costs and respond to emergencies

- New real-time microcontroller system from Texas Instruments enables smarter processing in automotive and industrial applications

- ODX-based diagnostic application software INTEWORK-OBT

- Share the MSP430F5529 clock UCS programming considerations

- RK3288 Information

- FFT based on C2000 series DSP

- Occupy the posting position, ESP32---WS2812 16*16 dot matrix drawing points, lines and surfaces

- ASM1117 SOT-323 heat sink problem?

- About the pitfalls of ADXL362 accelerometer

- SimpleLink Wi-Fi Devices

- Efficiency Programming of Single Chip Microcomputer Active Buzzer Driver

- TMS320F28335 project development record 9_28335 interrupt system

IC packaging basics and engineering design examples

IC packaging basics and engineering design examples 3D Packaging and Through Silicon Via (TSV) Process Technology

3D Packaging and Through Silicon Via (TSV) Process Technology

京公网安备 11010802033920号

京公网安备 11010802033920号