In foreign language multimedia teaching, it is required to control the speed of speech to meet the needs of students of different levels. However, traditional speech speed change products often change the original speaker's tone while the teacher changes the speed, which cannot achieve the real purpose of teaching. Therefore, the speech speed change system should have the characteristics of adjusting the speech speed while ensuring that the original speaker's tone remains unchanged. This article introduces a real-time speech speed change system based on TMS320C5409. In addition, considering that the compressed storage of speech and speech speed change are often required at the same time in the actual system, this article proposes a speech speed change algorithm based on the LPC low bit rate speech coding algorithm, which can adjust the speech speed arbitrarily.

Reference address:Design of real-time voice speed change system based on TMS320C5409

LPC algorithm

LPC coding regards the speech signal s(n) as the output signal of a time-varying vocal tract system under the excitation of the glottis. For voiced sounds, the glottis excitation is a periodic pulse train; for unvoiced sounds, the glottis excitation is a random noise sequence. The simplified block diagram of the speech signal is shown in Figure 1.

In LPC coding, a frame of speech signal can be represented by simplified model parameters, such as voiced and unvoiced discrimination, pitch period, gain G, and digital filter coefficient {a1}, so that 3kb/s coding can be obtained. During decoding, in LPC coding, voiced sound can be regarded as the excitation of a pulse train with a period, where the pulse period is the pitch period. Therefore, in order to change the speech rate, we lengthen the frame length of the speech, and then add several pulse train excitations to obtain a variable-speed speech signal.

Hardware system design

This system is a complete application system, which mainly completes the real-time LPC encoding and decoding of voice signals and voice speed change. In addition, it also has keyboard control function and voice recording and playback function. Therefore, this system not only needs external SRAM to store voice data, but also needs a keyboard control device connected to DSP. This system is mainly composed of TMS320C5409,

TLC320AD50

, SST39VF400A and CY7C133, and the system block diagram is shown in Figure 2. The 32K word on-chip RAM provided by TMS320C5409 is used to store real-time running programs and data, and the off-chip SRAM (CY7C133) is used to store encoded voice data. The working process of the system is as follows: After the system is powered on, the TMS320C5409 is reset through the reset function. After TMS320C5409 is reset, the internally fixed self-boot program moves the program and initialization data on the Flash (SST39VF400A) to the on-chip RAM. Then TMS320C5409 executes operations according to the control of the keyboard, runs LPC encoding operations (recording), LPC decoding and voice speed change (playback), and adjusts the voice speed change rate.

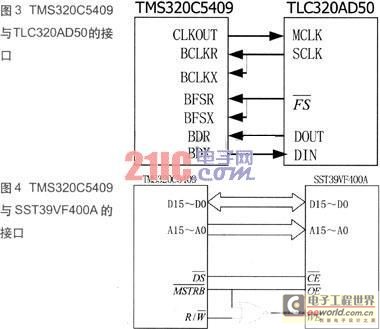

TMS320C5409 is used to implement the voice encoding and decoding algorithm, and TLC320AD50 is used to complete the D/A and A/D conversion functions of the voice signal. TMS320C5409 and TLC320AD50 communicate through the McBSP serial port. In order to reduce the burden on the CPU, this system is designed to communicate with the CPU by interrupting the CPU after receiving or sending a group of units through DMA. The interface between TMS320C5409 and TLC320AD50 is shown in Figure 3.

Adopt DMA mode, that is, every time the serial port receives or sends a group of units, it will automatically trigger DMA to move them to an internal buffer, and when the buffer is full, it will tell the CPU to process it through interruption. At this time, it is best to use ABU (Auto Buffering) mode for DMA, which can effectively prevent the data in the buffer from being washed away by new data when the serial port rate is high. When changing the voice speed, you only need to change the frame length of the 13MA channel accordingly.

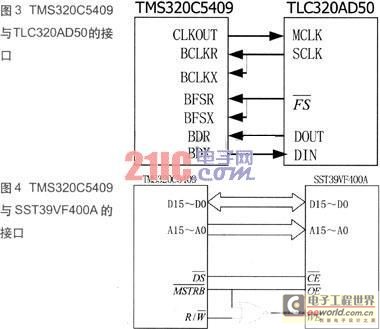

SST39VF400A (256K×1 6-bit) is used as the external data memory of TMS320C5409. The address bus and data bus are connected to the external bus of TMS320C5409, and CR is connected to DS of TMS320C5409. The interface between TMS320C5409 and SST39VF400A is shown in Figure 4.

The external memory uses CY7C133, which is a high-speed 2K×16bit static asynchronous dual-port RAM with a storage speed of 25ns. It has two independent address lines, data lines and control signal lines, allowing the data in the two control devices to communicate through the commonly connected memory. The dual-port RAM allows two controllers to read any storage unit at the same time (including reading the same unit at the same time), but does not allow simultaneous writing or one reading and one writing of the same address unit.

For TMS 320VC5402, the corresponding address of data memory CY7C133 is 4000H~47FFH.

System Software

The goal of this system is to achieve keyboard control function and voice recording and playback function, and can play the input voice signal at any variable rate without changing the voice tone. The system uses C language for function development.

In this system, the HPI port is mapped to GPIO, and the keyboard line is connected to INTO through an OR gate. When a key is pressed, the INTO interrupt handler determines whether it is recording, playing, speeding up or slowing down by reading the value from GPIO.

Anti-interference design

This system uses both hardware anti-interference technology and software anti-interference technology. The following is a brief introduction to the design of the hardware watchdog and digital filter used in this system.

The hardware watchdog function is used to improve the anti-interference ability of the system. The watchdog circuit (Figure 5) composed of the dedicated chip MAX692 uses fewer peripheral components. MAX692 is a microsystem monitoring circuit chip with functions such as backup battery switching, power failure detection, and watchdog monitoring. Among them, WDI is the watchdog detection input terminal, which is connected to a dedicated I/O port or a bus port of the digital circuit system. RESET is the reset signal output terminal, which is connected to the reset terminal RST of the digital circuit system. The WDI timing period of MAX692 is 1.6 s, and the reset pulse width is 200ms. If WDI remains high or low for more than the "watchdog" timing period (1.6s), a negative pulse of 200ms width (minimum 140ms) will occur at the RESET terminal to reset the digital circuit system.

Assume that the input signal of the digital filter is X(n) and the output signal is Y(n), then the relationship between the input sequence and the output sequence can be expressed by the difference equation:

In the formula, the input signal X(n) can be a digital sequence obtained after sampling and ADC conversion of the speech signal, or it can be the output signal of the computer; aK and bK are coefficients. By setting aK and bK, DF can be designed into the required bandpass filter.

There are six methods for software design of digital filters: program judgment filtering method (limited filtering method), median filtering method, arithmetic average filtering method, recursive average filtering method, pulse interference prevention average filtering method, first-order lag filtering method, etc. According to the needs, this system selects program judgment filtering method.

Conclusion

Practice has proved that this system can ensure that the original speaker's tone remains unchanged while changing the speech speed, and it is simple to operate and has a small system delay.

Previous article:Programmable controller solves the problem of synchronous control of distributed vehicle drives

Next article:Design of reversing radar control system

- Popular Resources

- Popular amplifiers

Latest Industrial Control Articles

- Molex leverages SAP solutions to drive smart supply chain collaboration

- Pickering Launches New Future-Proof PXIe Single-Slot Controller for High-Performance Test and Measurement Applications

- CGD and Qorvo to jointly revolutionize motor control solutions

- Advanced gameplay, Harting takes your PCB board connection to a new level!

- Nidec Intelligent Motion is the first to launch an electric clutch ECU for two-wheeled vehicles

- Bosch and Tsinghua University renew cooperation agreement on artificial intelligence research to jointly promote the development of artificial intelligence in the industrial field

- GigaDevice unveils new MCU products, deeply unlocking industrial application scenarios with diversified products and solutions

- Advantech: Investing in Edge AI Innovation to Drive an Intelligent Future

- CGD and QORVO will revolutionize motor control solutions

MoreSelected Circuit Diagrams

MorePopular Articles

- Innolux's intelligent steer-by-wire solution makes cars smarter and safer

- 8051 MCU - Parity Check

- How to efficiently balance the sensitivity of tactile sensing interfaces

- What should I do if the servo motor shakes? What causes the servo motor to shake quickly?

- 【Brushless Motor】Analysis of three-phase BLDC motor and sharing of two popular development boards

- Midea Industrial Technology's subsidiaries Clou Electronics and Hekang New Energy jointly appeared at the Munich Battery Energy Storage Exhibition and Solar Energy Exhibition

- Guoxin Sichen | Application of ferroelectric memory PB85RS2MC in power battery management, with a capacity of 2M

- Analysis of common faults of frequency converter

- In a head-on competition with Qualcomm, what kind of cockpit products has Intel come up with?

- Dalian Rongke's all-vanadium liquid flow battery energy storage equipment industrialization project has entered the sprint stage before production

MoreDaily News

- Allegro MicroSystems Introduces Advanced Magnetic and Inductive Position Sensing Solutions at Electronica 2024

- Car key in the left hand, liveness detection radar in the right hand, UWB is imperative for cars!

- After a decade of rapid development, domestic CIS has entered the market

- Aegis Dagger Battery + Thor EM-i Super Hybrid, Geely New Energy has thrown out two "king bombs"

- A brief discussion on functional safety - fault, error, and failure

- In the smart car 2.0 cycle, these core industry chains are facing major opportunities!

- The United States and Japan are developing new batteries. CATL faces challenges? How should China's new energy battery industry respond?

- Murata launches high-precision 6-axis inertial sensor for automobiles

- Ford patents pre-charge alarm to help save costs and respond to emergencies

- New real-time microcontroller system from Texas Instruments enables smarter processing in automotive and industrial applications

Guess you like

- Ginkgo USB-SPI host mode four data transmission mode timing diagram

- History of the Development of Microwave Circuits

- 6657Statically configure serial port general interrupt in sys/bios

- Understanding Nginx Architecture in One Article

- Highly recommended! ADI's latest Chinese information is here

- Urgently looking for expert advice AD15 can not open the PCB after cracking

- Difference between LPS22HH and LPS22HB

- How to collect multiple sensor signals through one RS485 interface of industrial computer?

- Altera SoC Architecture Excerpt - What is a SoC FPGA

- How to use common mode chokes in signal lines to eliminate common mode noise

FMS6418AM16

FMS6418AM16

京公网安备 11010802033920号

京公网安备 11010802033920号