1. Abstract

:

SPI interface is widely used. In many cases, people will use software simulation to generate SPI timing or use MCU with SPI function module. However, with the development of programmable logic technology, people often need to design simple SPI transmission module by themselves. This article introduces a method based on FPGA to automatically send parallel data in SPI serial mode.

2. Keywords

:

VHDL, FPGA, SPI, serial data output selection module, shift pulse generation module, SPI clock acquisition signal and SPI reference clock generation module without phase shift, SPI clock output selection module, 8-bit SPI clock acquisition generation module, 16-bit SPI clock acquisition generation module, 24-bit SPI clock acquisition generation module, 8-bit data shift module, 16-bit data shift module, 24-bit data shift module.

3. Functional block diagram

:

SPI_MODES is the input mode selection port:

--"01" is 8-bit transmission mode

--"10" is 16-bit transmission mode

--"11" is 24-bit transmission mode

CLKS is the reference clock of the entire module

DBINOUTS is the parallel data input port:

--8-bit mode is DBINOUTS(7 downto 0)

--16-bit mode is DBINOUTS(15 downto 0)

--24-bit mode is DBINOUTS(23 downto 0)

SPI_WR is the signal to start SPI transmission

The entire functional module can work in 8-bit, 16-bit, 24-bit SPI burst transmission state. The steps for software operation are quite simple:

--The software operation process of this module is as follows

--1. SPI_MODES="xx" Set the serial port operation mode

--2. DBINOUTS="xxxxxxxxxxxxxxxxxxxxxxxx" Input the data to be transmitted

--3. SPI_WR='0'

--4. SPI_WR='1'

--5. SPI_WR='0'

--8bit mode delay 2*8*4*CLKS

--16bit mode delay 2*16*4*CLKS

--24bit mode delay 2*24*4*CLKS

--6. DBINOUTS="xxxxxxxxxxxxxxxxxxxxxxxx" Input the next data to be transmitted

4. Interpretation

of VHDL Description--The following describes a SPI automatic transmission module

--In many cases, people will use software simulation methods to generate SPI timing

--Here, the hardware method is used, even if the software operation is simpler, it has improved the transmission speed

--------------------------------------------------------------

--The software operation process of this module is as follows

--1. SPI_MODES="xx" Set the serial port operation mode

--2. DBINOUTS="xxxxxxxxxxxxxxxxxxxxxxxx" Input the data to be transmitted

--3. SPI_WR='0'

--4. SPI_WR='1'

--5. SPI_WR='0'

--8bit mode delay 2*8*4*CLKS

--16bit mode delay 2*16*4*CLKS

--24bit mode delay 2*24*4*CLKS

--6. DBINOUTS="xxxxxxxxxxxxxxxxxxxxxxxx" Input the next data to be transmittedlibrary

ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity SPI_interface is

port(CLKS :in std_logic; --reference clock

LCD_SCLS :out std_logic;--SPI transmit clock, rising edge valid

LCD_SDIS :out std_logic;--SPI data serial output port

SPI_MODES :in std_logic_vector(1 downto 0);

--serial port operation mode selection

--"01"is 8bit trans mode

--"10"is 16bit trans mode

--"11"is 24bit trans mode

SPI_WR :in std_logic; --start serial port sending signal

DBINOUTS :in std_logic_vector(23 downto 0));

--parallel input port for sending data

--8bit mode use DBINOUTS(7 downto 0)

--16bit mode use DBINOUTS(15 downto 0)

--24bit mode use DBINOUTS(23 downto 0)

end;

architecture SPI_interface_behav of SPI_interface is

signal DB8BIT_reg :std_logic_vector(7 downto 0); --8bit data shift register

signal DB16BIT_reg :std_logic_vector(15 downto 0);--16bit data shift register

signal DB24BIT_reg :std_logic_vector(23 downto 0);--24bit data shift register

signal counter4 :std_logic_vector(3 downto 0); --Shift pulse generation counter

signal counter4s :std_logic_vector(1 downto 0); --SPI clock generation counter

signal counter8 :std_logic_vector(4 downto 0); --8bit SPI clock control counter

signal counter16 :std_logic_vector(5 downto 0); --16bit SPI clock control counter

signal counter24 :std_logic_vector(5 downto 0); --24bit SPI clock control counter

signal shift :std_logic;--Shift clock pulse

signal LCD_SCLSS :std_logic;--SPI clock acquisition signal

signal LCD_SCLSSS :std_logic;--SPI reference clock signal without phase shift

LCD_SCLSS8 :std_logic;--8bit SPI clock signal

signal LCD_SCLSS16 :std_logic;--16bit SPI clock signal

signal LCD_SCLSS24 :std_logic;--24bit SPI clock signal

signal LCD_SDIS_8BIT :std_logic;--8bit SPI data signal

signal LCD_SDIS_16BIT :std_logic;--16bit SPI data signal

signal LCD_SDIS_24BIT :std_logic;--24bit SPI data signal

begin

--Serial data output selection module

u1:process(LCD_SDIS_8BIT,LCD_SDIS_16BIT,LCD_SDIS_24BIT,SPI_MODES)

begin

if SPI_MODES="01" then --Select 8-bit serial data output

LCD_SDIS<=LCD_SDIS_8BIT;

elsif SPI_MODES="10" then --Select 16-bit serial data output

LCD_SDIS<=LCD_SDIS_16BIT;

elsif SPI_MODES="11" then --Select 24-bit serial data output

LCD_SDIS<=LCD_SDIS_24BIT;

else LCD_SDIS<='1';

end if;

end process;

--Shift pulse generation module

u2:process(CLKS)

begin

if CLKS='1' and CLKS'event then

if counter4="0011" then

counter4<="0000";

shift <='1';

else counter4<=counter4+1;

shift <='0';

end if;

end if;

end process;

--SPI clock acquisition signal and SPI reference clock generation module without phase shift

u3:process(CLKS)

begin

if CLKS='1' and CLKS'event then

if counter4s<"11" then

counter4s<=counter4s+1;

else counter4s<="00";

end if;

end if;

LCD_SCLSS<=counter4s(0); --SPI clock acquisition signal

LCD_SCLSSS<=counter4s(1); --SPI reference clock without phase shift

end process;

--SPI clock output selection module

u4:process(LCD_SCLSS8,LCD_SCLSS16,LCD_SCLSS24,SPI_MODES)

begin

if SPI_MODES="01" then

LCD_SCLS<=LCD_SCLSS8; --Select 8-bit SPI clock mode

elsif SPI_MODES="10" then

LCD_SCLS<=LCD_SCLSS16; --Select 16-bit SPI Clock mode

elsif SPI_MODES="11" then

LCD_SCLS<=LCD_SCLSS24; --Select 24bit SPI clock mode

else LCD_SCLS<='1';

end if;

end process;

--8bit SPI clock acquisition generation module

counter8_u:process(LCD_SCLSS)

begin

if SPI_WR='1' then

counter8<="10001";

elsif LCD_SCLSS='1' and LCD_SCLSS'event then

if counter8>0 then

counter8<=counter8-1;

LCD_SCLSS8<=LCD_SCLSSS;

end if;

end if;

end process;

--16bit SPI 时钟采集生成模块

counter16_u:process(LCD_SCLSS)

begin

if SPI_WR='1' then

counter16<="100001";

elsif LCD_SCLSS='1' and LCD_SCLSS'event then

if counter16>0 then

counter16<=counter16-1;

LCD_SCLSS16<=LCD_SCLSSS;

end if;

end if;

end process;

--24bit SPI 时钟采集生成模块

counter24_u:process(LCD_SCLSS)

begin

if SPI_WR='1' then

counter24<="110011";

elsif LCD_SCLSS='1' and LCD_SCLSS'event then

if counter24>0 then

counter24<=counter24-1;

if (counter24="000000")or(counter24="000001")or

(counter24="110011")or(counter24="000010")then

LCD_SCLSS24<='0';

else

LCD_SCLSS24<=LCD_SCLSSS;

end if;

end if;

end if;

end process;

--8bit 数据移位模块

DB8BIT_U:process(shift,SPI_WR,DBINOUTS)

begin

if SPI_WR='1' then

DB8BIT_reg<=DBINOUTS(7 downto 0);

else

if shift='1' and shift'event then

LCD_SDIS_8BIT<=DB8BIT_reg(0);

DB8BIT_reg(6 downto 0)<=DB8BIT_reg(7 downto 1);

end if;

end if;

end process;

--16bit 数据移位模块

DB16BIT_U:process(shift,SPI_WR,DBINOUTS)

begin

if SPI_WR='1' then

DB16BIT_reg(15 downto 0)<=DBINOUTS(15 downto 0);

else

if shift='1' and shift'event then

LCD_SDIS_16BIT<=DB16BIT_reg(0);

DB16BIT_reg(14 downto 0)<=DB16BIT_reg(15 downto 1);

end if;

end if;

end process;

--24bit 数据移位模块

DB24BIT_U:process(shift,SPI_WR,DBINOUTS)

begin

if SPI_WR='1' then

DB24BIT_reg(23 downto 0)<=DBINOUTS(23 downto 0);

else

if shift='1' and shift'event then

LCD_SDIS_24BIT<=DB24BIT_reg(0);

DB24BIT_reg(22 downto 0)<=DB24BIT_reg(23 downto 1);

end if;

end if;

end process;

end;

5. Simulation waveform

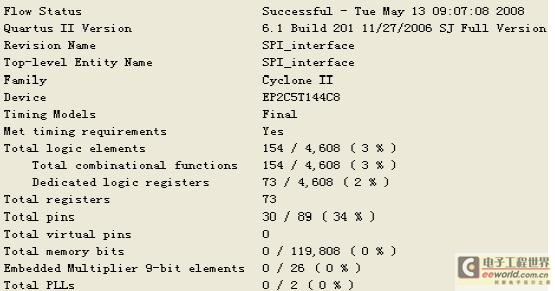

6. Resource usage after compilation

VII. Conclusion

This article aims to provide a reference for people who are learning programmable technology, and to serve as a starting point for others. I hope that readers who have read this article can provide better methods and share them with all learners.

Previous article:Design case of driving digital display circuit based on CPLD

Next article:Design of RS255/RS233 Decoder Based on Parallel Pipeline Structure

- Popular Resources

- Popular amplifiers

- Molex leverages SAP solutions to drive smart supply chain collaboration

- Pickering Launches New Future-Proof PXIe Single-Slot Controller for High-Performance Test and Measurement Applications

- CGD and Qorvo to jointly revolutionize motor control solutions

- Advanced gameplay, Harting takes your PCB board connection to a new level!

- Nidec Intelligent Motion is the first to launch an electric clutch ECU for two-wheeled vehicles

- Bosch and Tsinghua University renew cooperation agreement on artificial intelligence research to jointly promote the development of artificial intelligence in the industrial field

- GigaDevice unveils new MCU products, deeply unlocking industrial application scenarios with diversified products and solutions

- Advantech: Investing in Edge AI Innovation to Drive an Intelligent Future

- CGD and QORVO will revolutionize motor control solutions

- Innolux's intelligent steer-by-wire solution makes cars smarter and safer

- 8051 MCU - Parity Check

- How to efficiently balance the sensitivity of tactile sensing interfaces

- What should I do if the servo motor shakes? What causes the servo motor to shake quickly?

- 【Brushless Motor】Analysis of three-phase BLDC motor and sharing of two popular development boards

- Midea Industrial Technology's subsidiaries Clou Electronics and Hekang New Energy jointly appeared at the Munich Battery Energy Storage Exhibition and Solar Energy Exhibition

- Guoxin Sichen | Application of ferroelectric memory PB85RS2MC in power battery management, with a capacity of 2M

- Analysis of common faults of frequency converter

- In a head-on competition with Qualcomm, what kind of cockpit products has Intel come up with?

- Dalian Rongke's all-vanadium liquid flow battery energy storage equipment industrialization project has entered the sprint stage before production

- Allegro MicroSystems Introduces Advanced Magnetic and Inductive Position Sensing Solutions at Electronica 2024

- Car key in the left hand, liveness detection radar in the right hand, UWB is imperative for cars!

- After a decade of rapid development, domestic CIS has entered the market

- Aegis Dagger Battery + Thor EM-i Super Hybrid, Geely New Energy has thrown out two "king bombs"

- A brief discussion on functional safety - fault, error, and failure

- In the smart car 2.0 cycle, these core industry chains are facing major opportunities!

- The United States and Japan are developing new batteries. CATL faces challenges? How should China's new energy battery industry respond?

- Murata launches high-precision 6-axis inertial sensor for automobiles

- Ford patents pre-charge alarm to help save costs and respond to emergencies

- New real-time microcontroller system from Texas Instruments enables smarter processing in automotive and industrial applications

- Audi A6 computer version internal structure analysis, please come and teach me

- Excellent Works of the National College Student Electronic Design Competition - Smart Car Album

- Tektronix RF Communication Laboratory Innovation Experiment Platform

- What is the use of the C language comments in the figure?

- IoT Protocol: MQTT Protocol

- The Development and Application of Wireless Video Surveillance

- [The Big Secret of the Internet of Things Factory] How are circuit boards and data transmission modules produced?

- LIS2DE12MEMS digital output motion sensor ultra-low power high performance 3-axis "femto" accelerometer datasheet

- Chapter7 Analog-to-digital converter ADC12_A

- Open source hardware small project: Anxinke ESP-C3-12F controls WS2812

TC52N2133ECTRT

TC52N2133ECTRT

京公网安备 11010802033920号

京公网安备 11010802033920号