1. Introduction to SPI bus

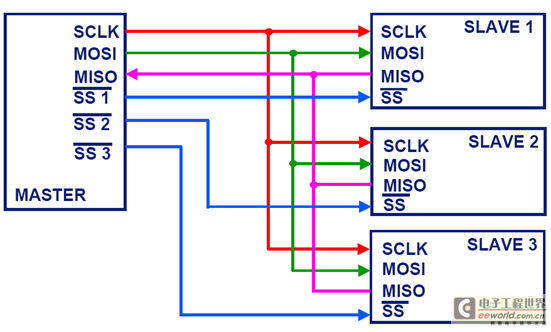

SPI (Serial Peripheral Interface) bus system is a synchronous serial peripheral interface, which enables MCU to communicate with various peripheral devices in serial mode to exchange information. It was first defined by Motorola on its MC68HCXX series processors in the 1980s. SPI interface is mainly used in EEPROM, FLASH, real-time clock, AD converter, and between digital signal processor and digital signal decoder. SPI bus system can directly interface with a variety of standard peripheral devices produced by various manufacturers. The interface generally uses 4 lines: serial clock line (SCLK), host input/slave output data line MISO, host output/slave input data line MOSI and low-level effective slave select line SS (some SPI interface chips have interrupt signal line INT, and some SPI interface chips do not have host output/slave input data line MOSI). Its main features include: can send and receive serial data at the same time; can work as a host or slave; send end interrupt flag; write conflict protection; bus competition protection. Figure 1 is a schematic diagram of SPI bus architecture.

Figure 1 SPI bus architecture

SPI is a ring bus structure, composed of SS (CS), SCK, SDI, SDO, bidirectional transmission between the master and slave devices, to send and receive data, the highest rate can reach 5Mbps. The SS (CS) signal is used to select the slave device that communicates with the master device, so point-to-point communication can be achieved between the master and slave devices at a certain point in time, and the advantage is that no addressing operation is required. SPI has 4 working modes, SP0, SP1, SP2, SP3, among which SP0 and SP3 are more commonly used. In order to exchange data with peripherals, the SPI module can configure the output serial synchronous clock polarity and phase according to the working requirements of the peripherals. The clock polarity (CPOL) has no significant impact on the transmission protocol. If CPOL=0, the idle state of the serial synchronous clock is low; if CPOL=1, the idle state of the serial synchronous clock is high. The clock phase (CPHA) can be configured to select one of two different transmission protocols for data transmission. If CPHA=0, data is sampled at the first transition edge (rising or falling) of the serial synchronous clock; if CPHA=1, data is sampled at the second transition edge (rising or falling) of the serial synchronous clock. The clock phase and polarity of the SPI master module and the peripherals communicating with it should be consistent. Figure 2 shows the SCK in the four working modes of the SPI bus.

Figure 2 shows the four working modes of the SPI bus

. SPI is a ring bus structure. Its main working sequence is that under the control of SCK, two bidirectional shift registers exchange data.

Assume that the 8-bit register below is loaded with the data to be sent, 10101010, which is sent on the rising edge, received on the falling edge, and sent first on the high bit.

Then when the first rising edge comes, the data will be sdo=1; register=0101010x. When the falling edge comes, the level on sdi will be latched into the register, then the register=0101010sdi, so that after 8 clock pulses, the contents of the two registers are exchanged once. This completes a spi sequence.

Example:

Assume that the host and slave are ready for initialization: and the host's sbuff=0xaa, the slave's sbuff=0x55, the following will demonstrate the data of 8 clock cycles of spi step by step: Assume that the rising edge sends data

Pulse master sbuff slave sbuff sdi sdo

0 10101010 01010101 0 0

1 up 0101010x 1010101x 0 1

1 down 01010100 10101011 0 1

2 up 1010100x 0101011x 1 0

2 down 10101001 01010110 1 0

3 up 0101001x 1010110x 0 1

3 down 01010010 10101101 0 1

4 up 1010010x 0101101x 1 0

4 down 10100101 01011010 1 0

5 up 0100101x 1011010x 0 1

5 down 01001010 10110101 0 1

6 up 1001010x 0110101x 1 0

6 down 10010101 01101010 1 0

7 up 0010101x 1101010x 0 1

7 down 00101010 11010101 0 1

8 up 0101010x 1010101x 1 0

8 down 01010101 10101010 1 0

This completes the 8-bit exchange of the two registers. The upper side indicates the rising edge, the lower side indicates the falling edge, and the sdi and sdo are relative to the host. When the ss pin is used as the host, the slave can pull it down to select it as the slave. When it is used as the slave, it can be used as a chip select pin. According to the above analysis, a complete transmission cycle is 16 bits, that is, two bytes, because first the host sends a command, and then the slave prepares the data according to the host's name. The host reads the data back in the next 8-bit clock cycle [page]

2. The demand for SPI bus testing

Engineers' demand for SPI bus testing and analysis mainly covers the following three aspects:

2.1 Understanding what is happening on the bus

Software engineers design the message content sent by the SPI master device, but hardware engineers need to determine whether the message is accurately transmitted to the physical line and need to understand what is really happening on the bus. The traditional way of using an oscilloscope is to first capture the signal with a probe, then convert it into "1" or "0" according to the level characteristics, and then compare it with the SPI protocol to restore it to a meaningful message frame. This method is time-consuming and labor-intensive, requires high professional skills of engineers, and the instrument utilization efficiency is very low. Engineers need the instrument to provide an automated way to directly translate the acquired waveform into easily recognizable content, and then dynamically display it on the instrument screen in different ways according to the needs of different types of engineers. For example, hardware engineers may want to view the SPI message content in binary, low-level driver engineers want to analyze the waveform in hexadecimal, and application software engineers want to understand the actual data content running on the bus in ASCII text.

2.2 Debugging Faulty Nodes on the Bus

SPI devices can achieve one-to-many connections, that is, one master device connects to multiple slave devices, and the slave device to be operated is selected through the chip select signal (SS/CS). When the master device switches the transmission object, we need to pay attention to whether the information sent by the bus is consistent with the selected slave device. It is possible that the information sent is inconsistent with the currently selected slave device.

2.3 Analyze the validity of EEPROM or Falsh memory unit

EEPROM/Falsh is a storage device widely used on various system boards. Its main function is to save the information that needs to be imported when the system is powered on, such as the main memory address, capacity, mode, various device initialization status, some system information, etc. EEPROM/Falsh devices mostly transmit data through the SPI bus. When there is an error in reading and writing EEPROM/Falsh configuration information, we not only need to know which EEPROM has a problem, but it is more meaningful to go deep into the device to locate which address unit has a problem, whether there is a problem in the data reading process or the data writing process.

3. LeCroy oscilloscopes fully meet the needs of engineers testing SPI buses

Engineering users are increasingly in need of solutions that can handle various general measurement tasks, meet the special needs of analyzing low-speed serial buses such as SPI buses, and meet limited budgets. LeCroy's full range of oscilloscope products based on the Windows operating system meet these needs. These series include WaveSurfer Xs, WaveRunner Xi, WavePro 7Zi and WaveMaster 8Zi. One of the important applications of these products is debugging serial buses. Oscilloscopes should not only be able to measure conventional items such as signal level and frequency, but also provide special software packages for more in-depth analysis and debugging of SPI buses.

The bus protocol trigger function and bus protocol decoding function of the LeCroy SPI test software package can help the project complete the equipment debugging:

3.1 Bus protocol triggering

In the interface of the LeCroy oscilloscope, enter the menu item "Trigger"->"Serial Data"->"SPI". The pop-up interface allows users to trigger the SPI message frame according to a specific mode, as shown in Figure 3 below. You can choose different data to trigger the bus according to your needs. You can choose to trigger a subset of the SPI bus standard (SPI, SIOP, SSPI). You can set the phase and polarity of the clock, and the high or low bit trigger of the data. You can enter the number of data to be triggered, and the number of bits of the data can be adjusted. You can also choose to use binary or hexadecimal as the trigger data format.

Through bus triggering, we can analyze and debug the information transmitted by the bus and possible errors.

Figure 3 LeCroy oscilloscope SPI software package setting trigger interface

3.2 Bus protocol decoding

In the LeCroy oscilloscope interface, enter the menu item "Analysis"->"Serial Decode"->"SPI", the user can decode the data content being transmitted by the bus in real time, and the decoded content can be directly displayed above the waveform in three ways: "Binary", "Hexadecimal" and "ASCII". For example, the information in Figure 4, the second 0x05 on MOSI indicates RDSR, and the read status register is checked. MISO immediately returns 0x02, indicating that the device is writable and in idle state.

By decoding the captured bus protocol, we can intuitively see whether the data transmitted on the bus is the data actually sent and received by the engineer, thereby helping debugging.

Figure 4 SPI bus decoding

In addition to being able to display the decoding results directly on the waveform, LeCroy also provides a list display of the decoding results. For example, the information in Figure 5, the list shows the relevant information of the field after decoding, and you can zoom in on the data to observe the waveform details by clicking on a row in the list.

Figure 5 SPI list display and zoom

Previous article:USB3.0 physical layer test introduction and difficulty analysis

Next article:A brief analysis of RFID testing technology

- Keysight Technologies Helps Samsung Electronics Successfully Validate FiRa® 2.0 Safe Distance Measurement Test Case

- From probes to power supplies, Tektronix is leading the way in comprehensive innovation in power electronics testing

- Seizing the Opportunities in the Chinese Application Market: NI's Challenges and Answers

- Tektronix Launches Breakthrough Power Measurement Tools to Accelerate Innovation as Global Electrification Accelerates

- Not all oscilloscopes are created equal: Why ADCs and low noise floor matter

- Enable TekHSI high-speed interface function to accelerate the remote transmission of waveform data

- How to measure the quality of soft start thyristor

- How to use a multimeter to judge whether a soft starter is good or bad

- What are the advantages and disadvantages of non-contact temperature sensors?

- Innolux's intelligent steer-by-wire solution makes cars smarter and safer

- 8051 MCU - Parity Check

- How to efficiently balance the sensitivity of tactile sensing interfaces

- What should I do if the servo motor shakes? What causes the servo motor to shake quickly?

- 【Brushless Motor】Analysis of three-phase BLDC motor and sharing of two popular development boards

- Midea Industrial Technology's subsidiaries Clou Electronics and Hekang New Energy jointly appeared at the Munich Battery Energy Storage Exhibition and Solar Energy Exhibition

- Guoxin Sichen | Application of ferroelectric memory PB85RS2MC in power battery management, with a capacity of 2M

- Analysis of common faults of frequency converter

- In a head-on competition with Qualcomm, what kind of cockpit products has Intel come up with?

- Dalian Rongke's all-vanadium liquid flow battery energy storage equipment industrialization project has entered the sprint stage before production

- Allegro MicroSystems Introduces Advanced Magnetic and Inductive Position Sensing Solutions at Electronica 2024

- Car key in the left hand, liveness detection radar in the right hand, UWB is imperative for cars!

- After a decade of rapid development, domestic CIS has entered the market

- Aegis Dagger Battery + Thor EM-i Super Hybrid, Geely New Energy has thrown out two "king bombs"

- A brief discussion on functional safety - fault, error, and failure

- In the smart car 2.0 cycle, these core industry chains are facing major opportunities!

- The United States and Japan are developing new batteries. CATL faces challenges? How should China's new energy battery industry respond?

- Murata launches high-precision 6-axis inertial sensor for automobiles

- Ford patents pre-charge alarm to help save costs and respond to emergencies

- New real-time microcontroller system from Texas Instruments enables smarter processing in automotive and industrial applications

- [Sipeed LicheeRV 86 Panel Review] 6-socket to achieve communication between different processes

- Usage diagram of various Arduino basic components

- [Transfer] C compiler version and predefined macros for system judgment

- AD21 interactive fast manual layout skills PCB reposition selected components in sequence reposition selected c...

- Diode frequency multiplier circuit, transistor frequency multiplier circuit

- [Silicon Labs BG22-EK4108A Bluetooth Development Evaluation] + Environment Construction SimplicityStudio-5

- 【National Technology N32G430】06 Comprehensive debugging, RTC, analog IIC, serial port

- Why GaN is the super power of 5G

- Book Review: Fundamentals of Power Supply Design

- CMOS circuit design issues under normal operating current

Signal Integrity and Power Integrity Analysis (Eric Bogatin)

Signal Integrity and Power Integrity Analysis (Eric Bogatin)

京公网安备 11010802033920号

京公网安备 11010802033920号