Knowledge Points Summary

The prototype of the page read function of nand flash is void nf_readpage(unsigned int block,unsigned int page,unsigned char *dstaddr), and its function is to read 1 page (for K9F2G, 1 page is equal to 2KB) of the contents from the page page of the block block of nand flash, and store it at the address pointed to by the pointer dstaddr. Some people may say, since nf_readpage can read 1 page of data to the specified address, and the address of sdram is 0x30000000, it can be used directly to copy the code of nand flash to sdram. The answer is of course yes! But there is a premise, the content copied to sdram must be within 2KB, once it exceeds 2KB, you need to borrow the RdNF2SDRAM() function. I believe that this explanation can make you understand the difference and connection between the two functions.

Let's talk about absolute address and relative address. First of all, we know that k9f2g has 2048 blocks, each block has 64 pages, and each page has 2K bytes. What we usually say is the relative address, such as the 2nd block and the 3rd page is a relative address. And the absolute address = block number * 64 + page number, for example, the 2nd block and the 3rd page in front is converted to an absolute address of 131 (131=2*64+3).

The following is an explanation of the RdNF2SDRAM() function:

Line 113: From line 117, we can see that i here refers to the relative address.

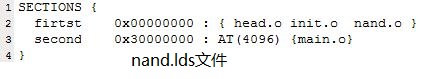

Line 114: The starting address in the nand flash. Here, 4096 represents bytes. The memory size of k9f2g is 256Mbyte. The reason why start_addr=4096 here is because we defined the address of the main.c file at 4096 in the nand.lds file. As shown in the figure below:

If AT(4096) is changed to AT(5120), then start_addr here is equal to 5120. Also note that 4096byte is 4KB here. Why is it defined after 4KB of nand flash? Because the hardware circuit will automatically move the first 4KB of the nand flash to the stepping stone for execution. If it is defined after 3KB, the main.c function will be executed directly, and there is no need to copy it.

| Address Lines | [A28:A18] | [A17:A12] | [A11:A0] |

| Address indication | Block Address | Page address | Offset address within the page |

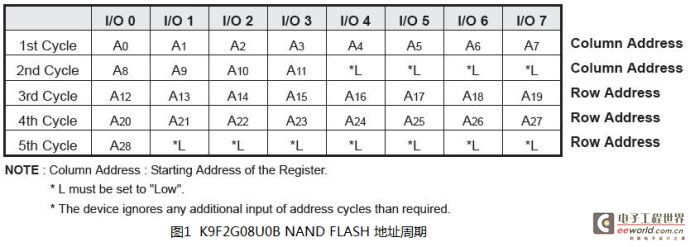

Whether in the nand flash page read function or the write function, you need to send the address to the address register, as shown in the following figure:

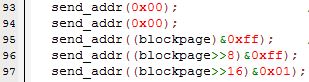

Why is this the case? Since the page read and write functions are performed in units of pages, each time you have to start at the 0th byte of the page, that is, the offset address within the page is 0, so the lower 12 bits of the address line can be set to 0, such as lines 93 and 94.

Line 95, at this time it is in the third address cycle, so you need to send the A12-A19 bits of blockpage (blockpage is the absolute address of the page at this time), so just AND the blockpage with 0xff. It is important to note that the absolute address of the page is represented by A28-A12, and has nothing to do with A11-A0.

Line 96, at this time it is in the third address cycle, so it is necessary to send the A20-A27 bits of blockpage (at this time blockpage is the absolute address of the page), so it is sufficient to shift the blockpage right by 8

bits and AND it with 0xff. Line 97, at this time it is in the third address cycle, so it is necessary to send the A28 bit of blockpage (at this time blockpage is the absolute address of the page). As can be seen from Figure 1, although 8 bits are sent at this time, only the 0th bit is valid, and the other bits are invalid. Therefore, shift the blockpage right by 16 bits, and then AND it with 0x1, and only keep the 0th bit.

The clock of mini2440 development board

Compile and generate bin file, download and run.

Code source file

Baidu Wenku pdf address: http://wenku.baidu.com/view/85e30572168884868662d603

PDF file download address: http://download.csdn.net/detail/mybelief321/5234586

Source code download address: http://download.csdn.net/detail/mybelief321/ 5234602

Previous article:Bare metal code of mini2440 interrupt modified by Wei Dongshan

Next article:ARM assembly instruction MCR/MRC learning

Recommended ReadingLatest update time:2024-11-23 11:24

- Popular Resources

- Popular amplifiers

- Naxin Micro and Xinxian jointly launched the NS800RT series of real-time control MCUs

- How to learn embedded systems based on ARM platform

- Summary of jffs2_scan_eraseblock issues

- Application of SPCOMM Control in Serial Communication of Delphi7.0

- Using TComm component to realize serial communication in Delphi environment

- Bar chart code for embedded development practices

- Embedded Development Learning (10)

- Embedded Development Learning (8)

- Embedded Development Learning (6)

Professor at Beihang University, dedicated to promoting microcontrollers and embedded systems for over 20 years.

Professor at Beihang University, dedicated to promoting microcontrollers and embedded systems for over 20 years.

- Intel promotes AI with multi-dimensional efforts in technology, application, and ecology

- ChinaJoy Qualcomm Snapdragon Theme Pavilion takes you to experience the new changes in digital entertainment in the 5G era

- Infineon's latest generation IGBT technology platform enables precise control of speed and position

- Two test methods for LED lighting life

- Don't Let Lightning Induced Surges Scare You

- Application of brushless motor controller ML4425/4426

- Easy identification of LED power supply quality

- World's first integrated photovoltaic solar system completed in Israel

- Sliding window mean filter for avr microcontroller AD conversion

- What does call mean in the detailed explanation of ABB robot programming instructions?

- STMicroelectronics discloses its 2027-2028 financial model and path to achieve its 2030 goals

- 2024 China Automotive Charging and Battery Swapping Ecosystem Conference held in Taiyuan

- State-owned enterprises team up to invest in solid-state battery giant

- The evolution of electronic and electrical architecture is accelerating

- The first! National Automotive Chip Quality Inspection Center established

- BYD releases self-developed automotive chip using 4nm process, with a running score of up to 1.15 million

- GEODNET launches GEO-PULSE, a car GPS navigation device

- Should Chinese car companies develop their own high-computing chips?

- Infineon and Siemens combine embedded automotive software platform with microcontrollers to provide the necessary functions for next-generation SDVs

- Continental launches invisible biometric sensor display to monitor passengers' vital signs

- [Mill MYB-YT507 development board trial experience] tkinter Button learning

- Learn MSP430G2755 Main Bootloader UART Porting

- Please advise on the wiring method of the hot wire sensor MR516

- Award-winning live broadcast | ADI motor control solutions

- EEWORLD University Hall - From the Natural World to the Intelligent Era

- [Xianji HPM6750EVKMINI Review] 1# Hardware Introduction and Development Environment Construction

- How can an electric mosquito swatter kill mosquitoes without harming people? Is it because the voltage is high and the time is short? Isn't that related to ESD?

- Competition sharing, Xiaobai unboxing

- LTC3407 DC-to-DC Regulator

- Calculation of Series Resistance Value in Voltage Stabilization Circuit

Follow me Season 2 Episode 3 Mission Code

Follow me Season 2 Episode 3 Mission Code Automotive Electronics S32K Series Microcontrollers: Based on ARM Cortex-M4F Core

Automotive Electronics S32K Series Microcontrollers: Based on ARM Cortex-M4F Core

京公网安备 11010802033920号

京公网安备 11010802033920号