At present, the Ethernet protocol has been widely used in various computer networks, such as office LANs, industrial control networks, the Internet, etc., and is still developing. Single chip microcomputer or microcontroller (MCU) (also known as embedded system) has been widely used in various fields. At present, most systems are based on MCU as the core, and cooperate with monitoring, servo, and indicating equipment to achieve certain functions. If the embedded system can be connected to the Internet, information can be transmitted to any place in the world conveniently and cheaply. Therefore, how the microcontroller controls the Ethernet network card to transmit data, and how to load the TCP/IP protocol to connect to the Internet, these are some challenging issues [1, 2].

One of the most researched solutions for using microcontrollers to access the Internet is to use microcontrollers to drive ISA bus network cards or drive Ethernet control chips based on the ISA bus. However, in recent years, with the disappearance of the ISA bus on desktop computers (the standards after PC98 have canceled the ISA bus), the number of ISA bus devices has been decreasing, and many manufacturers of ISA network card chips have stopped producing ISA network card chips. In computers, most devices use the PCI bus. Therefore, how to manufacture low-cost PCI bus Ethernet interface devices and how to use microcontrollers to drive PCI bus network cards have become urgent needs in current computer industrial control systems. However, it is almost impossible to use an 8-bit microcontroller with only a 16-bit address bus and an 8-bit data port to directly drive a PCI bus network card with a 32-bit address data multiplexing bus and other various signal lines.

To this end, in this article, the PCI 9054 interface chip is used as a bridge between the microcontroller and PCI devices. The reliable communication task between the microcontroller and the PCI network card is designed and implemented, and the main hardware interface circuit and main program original code are provided.

1PCI9054 chip introduction[3]

1.1 PCI9054 main features

PCI9054 is an advanced PCI I/O accelerator produced by the American PLX Company. It adopts advanced PLX data pipeline structure technology. The PCIV2,2-compliant 32-bit 33 MHz bus master interface controller achieves PCI burst transfer speeds of up to 132 Mb/s. The universal bus master control interface is equipped with an advanced data pipeline architecture (Data Pipe Architecture(tm)), including 2 DMA engines, programmable target, initiator data transfer mode and PCI information transfer functions.

1.2 PCI9054 local bus working mode introduction

The local bus connected to the PCI9054 chip has three working modes: M mode, C mode and J mode. The mode selection pin can be used to select, among which the C mode timing is relatively simple. For this reason, this program design chooses PCI 9054 to work in C mode. When PCI9054 works in C mode, its data transmission adopts direct data transmission method. According to the control method of data transmission, it is divided into 3 transmission modes, as shown in Table 1.

|

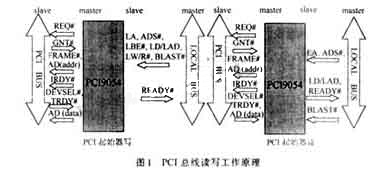

This solution is designed to use the PCI initializer mode, controlling the PCI9054 chip through the local microcontroller, and then driving the network card on the PCI bus through the PCI9054 chip. The PCI9054 chip here is like a bridge, connecting two different bus devices. Its reading and writing working principle is shown in Figure 1.

|

1.3 Introduction to PCI9054 registers

PCI9054 provides 5 types of registers internally: PCI configuration register, local configuration register, runtime RUNTIME register, DMA register and I2O information register. In the design of this solution, we mainly use two types of configuration registers: PCI configuration register and local configuration register. The functions of these two registers are briefly introduced below.

The PCI configuration register is what we often call the PCI configuration space. It provides some information for configuring PCI. Among them, VenderID, DeviceID, RevisionID, HeaderType, and ClassCode are used to identify PCI devices. The command register (Command) contains device control bits, including allowing memory read and write responses, etc. The status register (Status) is used to record PCI bus related events. The PCI configuration register provides 6 base address registers. These base addresses are within the physical address range in the system. BASE0 and BASE1 are the base addresses used to access other configuration registers. BASE1 is the base address for other configuration registers mapped to the PCI side. The base address of memory, BASE2 is the base address of other registers mapped to PCI side I/O. Therefore, the LOCAL configuration register and the other three registers can be accessed through PCI-side memory and PCI-side I/O. The four spaces of BASE2~5 provide access to 4 chips connected to the local end (of course it can be less than 4). They translate the local end chip into a PCI address through the local end address (set in the LOCAL configuration register), and also It is to map the local chip to the system's memory or I/O port. In this way, using a program to operate this memory (or I/O) is actually an operation on the local chip.

The local-side configuration register provides some information about the local-side. In the design of this solution, the local-side MCU read and write instructions and cycles are mainly converted into PCI-side read and write instructions and cycles by configuring the local-side configuration register. It is equivalent to mapping the chip and memory on the PCI side network card to the local side, and uniformly addressing the memory on the local side. In this way, as long as the microcontroller can access the memory on the local side, it can be used to access the network card on the PCI bus.

PCI9054 requires a configuration chip E?2PROM to work, so as to configure PCI 9054 when the PCI card is powered on. It mainly configures the VendorID and DeviceID of the PCI card, which are used by the system to identify the PCI card. In addition, other registers are also needed, mainly for initializing PCI 9054. The local registers can also be read and written by the local CPU and configured directly.

2RTL8029 network card introduction

RTL8029 is a 32-bit PCI bus network card that complies with the Ne2000 standard and follows the IEEE802.3 protocol. According to the function, it can be divided into: receiving function module, CRC generating module, sending function module, address recognition module, FIFO control module, protocol logic array module and DMA and buffer control module. Programming the network card enables communication between any site within the LAN. Familiarity with the network card interface circuit is the first prerequisite for programming the network card. The network card interface circuit function can be divided into two parts: one is connected to the computer PCI bus, including data bus reading and writing, address bus driving, interrupt control signal generation, memory reading and writing signals, and the introduction of I/O port signals; the second is The internal operations of the network card include reading and writing the buffer SRAM, controlling the RTL8029AS chip, reading the station address PROM and reading the boot ROM, etc. By analyzing the working principle of the network card, the interface signal lines can be reduced to the minimum.

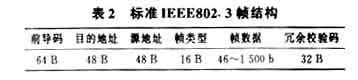

Ethernet is equivalent to a link layer connection, so the transmission unit of Ethernet can be called a frame. The Frame length of 10 Mb Ethernet is 64~1518 b. Its format is shown in Table 2.

|

The preamble is a code added by the network adapter to enable the receiving adapter to identify the beginning of the MAC frame when the network adapter sends it. High-level users do not need to consider it. The 32-bit CRC, or redundant check code, is the check mechanism used by Ethernet. Now the generation and detection of CRC can be completed by the network adapter, so users do not need to consider this field. Frame type, this field determines what protocol the Ethernet frame data uses, such as ARP is 0x0806, IP is 0x0800, etc. From another perspective, this field can also be regarded as the field that indicates the identity of the Ethernet frame itself. Therefore, when processing MAC frames, it is necessary to decide which upper-layer protocol to send the data to based on the data in this field. In the IEEE 802?3 protocol, this field indicates the length of the Ethernet data. Since the two protocols have different definitions of this field, the network adapter card does not interpret this field. Programmers must program the software to handle this field.

3 Scheme Design

(1) The hardware structure of this scheme is shown in Figure 2.

In addition to the 80C51 microcontroller and PCI9054, the main chips used in the system include MAX232 (serial port level conversion), 24C02 (I2C bus E? 2PROM), 74HC373 (8-bit latch), 62256 (32K RAM), EPM7096 (CPLD), 93C46 (E2PROM, used to initialize PCI9054). Among them, 62256 (external 32K RAM) does not need to be used. It can be replaced by the RAM on the network card. However, the access to the RAM on the network card is more complicated and the speed will be slower than adding 62256. The purpose of using external RAM is to increase the data transmission speed of the microcontroller and handle the complex TCP/IP protocol. Since the Ethernet data packet can be up to more than 1500 bytes, the 80C51 microcontroller cannot store such a large packet and can only put it in external RAM. At the same time, the external RAM is also used as the input and output buffer of the serial port to enable the microcontroller to have high-speed data throughput capabilities. 24C02 is the E2PROM of the I2C bus, which is used to store some user settings, such as IP address, gateway, etc. The purpose of using CPLD in this program is to convert the 8-bit data and 16-bit address of the 80C51 microcontroller into 32-bit data and address. Because when PCI9054 works in initializer mode, it requires the local bus to be 32-bit. Here, it is very simple to implement such an external logic with CPLD. MAX232 is a serial port level conversion circuit. Data can be input from the serial port to the microcontroller, and the microcontroller then transmits the data through the network card.

|

(2) Software design

Programming the network card is to program and control various registers in the network interface control chip RTL8029AS, so as to complete the correct sending and receiving of data packets. All microcontroller programs are compiled in C51 language, which has the characteristics of strong readability, good portability and short development cycle. The code usage efficiency is also relatively high.

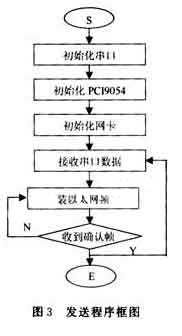

The main program can be divided into two parts: PCI9054 chip initialization, network communication and serial communication: The PCI9054 chip initialization process is to correctly program and configure the PCI side configuration register and local side configuration register of the PCI9054 chip to realize the local side microcontroller and PCI side. For the seamless connection of the network card, these two registers can be initialized either by programming the 93C46 or by directly programming the local CPU. The network communication process can be divided into three parts: network card initialization, sending control and receiving control. The main program block diagram is shown in Figure 3.

|

The PCI9054 chip initialization process is to initialize the relevant registers of the PCI9054 chip. These registers include DMRR, DMLBAM, PCICR, CNTRL, etc.

(1) PCICR[2∶0]=111B. Allows the PCI initializer (local side) to access the PCI bus. PCI9054 can respond to I/O access.

(2) DMPBAM[1∶0]=11. Allows the PCI initializer to access PCI9054 memory and I/O ports.

(3) DMRR = FFF00000H. Set

the accessible memory range of the PCI initializer side (4) to 1MB.

(5) DMLBAI = 40000000H. Set the local end base address

(6) DMPBAM[1]=1 for the PCI Initiator to PCI I/O Configuration register. Allow the local I/O port to access the PCI Initiator to PCI I/O Configuration register

DMCFGA [23:0] = 005010, DMCFGA [31] = 1.

The network card initialization process is to initialize the network card related registers. These registers include CR, DCR, RBCR PSTART, PSTOP, ISR, IMR, PAR0~PAR5, MAR0~MAR5D, etc. PSTART The address of the starting page of the receive buffer. PSTOP The end page address of the receive buffer (this page is not used for reception). BNRY points to the last read page (read pointer) CURR current reception end page address (write pointer).

(1) CR=0x21: Select page 0 register and put the RTL8029 chip offline;

(2) DCR=0x8: 32-bit memory access;

(3) RBCR0=0, RBCR1=0: Number of bytes transferred during remote DMA operation Clear;

(4) RCR=0xc0, the received frame is stored in the buffer;

(5) TCR=oxe2: loop test status;

(6) PSTART=0x4C, PSTOP=0x80; construct the buffer;

(7) ISR =0xff; clear the interrupt register;

(8) CR=0x61: select page 1;

(9) Set the network card address PAR0~PAR5

(10) Set the multi-access register MAR0~MAR5;

(11) CURR=0x4d: Initialize the current page register ;

(12) TCR=0xE0: The transmitter is in normal working status.

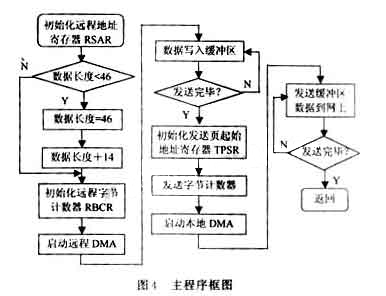

Sending control process In the network, the process of frame transmission is the process in which the sender encapsulates the data to be sent into frames according to the frame format requirements, and then sends them to the transmission line of the network through the network card. The sending program block diagram is shown in Figure 4.

|

Reception control process The frame reception process is divided into two steps [3]:

the first step is to have the local DMA store the frame in the receive buffer;

the second step is to have the remote DMA read the frame in the receive buffer into the memory. That is, the data frames on the network are received and stored in the receiving buffer of the network card, and then the host program reads the frames in the buffer and stores them in the memory. The reception of frames is automatically completed by the network card, and only the relevant registers and PSTART, PSTOP, CURR and BNRY need to be properly initialized. Before the frame is read in, the corresponding registers RSAR and RBCR must be initialized, and then the remote DMA read operation and the host program's read port operation are started. In order to obtain the data length, first read in 18 B of data, and then read in the complete frame according to the length of the valid data. To start the remote DMA read operation, CR=0AH should be set. The remote DMA will read 1 B from the DMA address of the receiving buffer and send it to the I/O data port, and the host program will read it into the memory.

This process will continue until the RBCR register is 0.

4 Conclusion

This article proposes a method that uses 8-bit microcontroller 80C51 and PCI bus master I/O accelerator chip 9054 to drive the PCI bus network card to realize the connection between RS232 serial devices and Ethernet to transmit control signaling and data files, and realize the microcontroller Internet access design, related hardware design, and corresponding driver programming. The entire solution has a simple structure and is easy to implement, shortening the development cycle and reducing system development costs.

Previous article:PIC series microcontroller application design and examples

Next article:Design of automatic solar tracker based on PIC16F877A

Recommended ReadingLatest update time:2024-11-16 17:29

- Popular Resources

- Popular amplifiers

-

Siemens PLC from Beginner to Mastery with Color Illustrations (Yang Rui)

Siemens PLC from Beginner to Mastery with Color Illustrations (Yang Rui) -

Siemens S7-1200-PLC Programming and Application Tutorial (3rd Edition) (Edited by Shi Shouyong)

Siemens S7-1200-PLC Programming and Application Tutorial (3rd Edition) (Edited by Shi Shouyong) -

Siemens Motion Control Technology and Engineering Applications (Tongxue, edited by Wu Xiaojun)

Siemens Motion Control Technology and Engineering Applications (Tongxue, edited by Wu Xiaojun) -

Modern Compiler Principles C Language Description (Ampel)

Modern Compiler Principles C Language Description (Ampel)

Professor at Beihang University, dedicated to promoting microcontrollers and embedded systems for over 20 years.

Professor at Beihang University, dedicated to promoting microcontrollers and embedded systems for over 20 years.

- Innolux's intelligent steer-by-wire solution makes cars smarter and safer

- 8051 MCU - Parity Check

- How to efficiently balance the sensitivity of tactile sensing interfaces

- What should I do if the servo motor shakes? What causes the servo motor to shake quickly?

- 【Brushless Motor】Analysis of three-phase BLDC motor and sharing of two popular development boards

- Midea Industrial Technology's subsidiaries Clou Electronics and Hekang New Energy jointly appeared at the Munich Battery Energy Storage Exhibition and Solar Energy Exhibition

- Guoxin Sichen | Application of ferroelectric memory PB85RS2MC in power battery management, with a capacity of 2M

- Analysis of common faults of frequency converter

- In a head-on competition with Qualcomm, what kind of cockpit products has Intel come up with?

- Dalian Rongke's all-vanadium liquid flow battery energy storage equipment industrialization project has entered the sprint stage before production

- Allegro MicroSystems Introduces Advanced Magnetic and Inductive Position Sensing Solutions at Electronica 2024

- Car key in the left hand, liveness detection radar in the right hand, UWB is imperative for cars!

- After a decade of rapid development, domestic CIS has entered the market

- Aegis Dagger Battery + Thor EM-i Super Hybrid, Geely New Energy has thrown out two "king bombs"

- A brief discussion on functional safety - fault, error, and failure

- In the smart car 2.0 cycle, these core industry chains are facing major opportunities!

- The United States and Japan are developing new batteries. CATL faces challenges? How should China's new energy battery industry respond?

- Murata launches high-precision 6-axis inertial sensor for automobiles

- Ford patents pre-charge alarm to help save costs and respond to emergencies

- New real-time microcontroller system from Texas Instruments enables smarter processing in automotive and industrial applications

- [SAMR21 New Gameplay] 24. Usage of I2C

- AD17 There is a problem with copper laying on a four-layer board

- Static Timing Analysis Basics and Applications

- Cost-effective 0-10V analog signal isolation technology: based on Y capacitor isolation

- HPM6700/6400 display control system (LCD and 2D graphics acceleration unit, LVGL)

- How to use Segger Embedded Studio to develop the HPM6750?

- 485 Point-to-Many Communication Problem

- The program of the microcontroller is lost, what's going on?

- EEWORLD University Hall----Audio Amplifier for Smart Speaker

- Qorvo Expands 1.8 GHz DOCSIS 4.0 Portfolio

Siemens PLC from Beginner to Mastery with Color Illustrations (Yang Rui)

Siemens PLC from Beginner to Mastery with Color Illustrations (Yang Rui) Siemens S7-1200-PLC Programming and Application Tutorial (3rd Edition) (Edited by Shi Shouyong)

Siemens S7-1200-PLC Programming and Application Tutorial (3rd Edition) (Edited by Shi Shouyong)

京公网安备 11010802033920号

京公网安备 11010802033920号