I2C (Inter IC BUS) is a bus developed by Philips for connecting chips. The I2C bus uses two signal lines for data transmission, one is the serial data line (SDA) and the other is the serial clock line (SCL). The I2C bus allows several compatible devices (such as memory, A/D converter, D/A converter, LCD driver, etc.) to share the bus. The maximum number of devices that the I2C bus can theoretically allow is limited to the total capacitance of all devices on the bus (including the capacitance of the connection itself and the lead-out capacitance of the connection end) not exceeding 400pF. All devices on the bus rely on the address signal sent by the SDA line for addressing, and no chip select line is required. At any time, the bus can only be controlled by one master device, and each slave device starts data transmission when the bus is idle. The standard mode rate of I2C bus data transmission is 100kbps, the fast mode rate is 400kbps, and the high-speed mode rate is 3.4Mbps.

Designing digital systems with VHDL and CPLD has incomparable advantages over traditional methods, and it has become the most effective means of large-scale integrated circuit design. For simplicity, this article uses VHDL to design the standard mode of I2C bus control circuit.

1 Data transmission on the I2C bus

The I2C bus contains two lines, the clock line SCL and the data line SDA. SCL is generated by the host. The data transmission process of the I2C bus is shown in Figure 1. The transmission process is as follows: First, the host generates a start bit, and then transmits the first byte. The highest bit MSB of the data is transmitted first in the 8-bit data, and the lowest bit LSB is the read/write indicator bit. 1 indicates that the host reads, and 0 indicates that the host writes. The high 7-bit address allows the host to address 128 slave devices.

After receiving the first byte of data, the slave sends a response bit, and the master sends the second byte of data after receiving the response bit. After the data is sent, the end bit is generated, and the data transmission is completed. During data transmission, SDA is allowed to switch only when the clock SCL is low. When SCL is high, SDA must be stable. At this time, the level of SDA is the value transferred by the bus.

When SCL is high, the SDA line switches from high to low to indicate the start bit, and the SDA line switches from low to high to indicate the stop bit. The start bit and stop bit are generated by the host. After the start bit is generated, the bus is in a busy state. After the stop bit appears and a certain period of time has passed, the bus enters an idle state. After each byte sent by the transmitter, the receiver must generate a response bit. The driving clock of the response bit is generated by the host, and the receiver pulls the SDA line low to generate a response bit. If the host is the receiver, when the last byte is received, the response bit is 1, notifying the slave to end the transmission, otherwise the response bit is 0. When the slave cannot respond to the slave address (for example, it is executing some real-time functions and cannot receive or send), or responds to the slave address but cannot receive more data bytes after a period of transmission, the slave can notify the host to terminate the current transmission by using the response bit as 1, so the host generates a stop bit to terminate the transmission, or generates a repeated start bit to start a new transmission.

The data transmitted on the SDA line must be 8 bits, and the number of bytes that can be sent each time is unlimited. If the slave needs to complete some other functions (such as executing an internal interrupt service routine) before receiving or sending the next data byte, the slave can keep SCL at a low level, forcing the host to enter a waiting state. When the slave is ready to receive or send the next data byte, it releases SCL and data transmission continues.

Both SDA and SCL are bidirectional lines, connected to the power supply through a pull-up resistor when in use. When the bus is idle, both lines are high level, and the output stage of the device connected to the bus must be open drain or open collector, so that the bus can perform the "wired AND" function.

After the host sends the first byte, there are three possible changes in the data transmission direction: (1) the transmission direction remains unchanged, such as the host writing to the slave; (2) the transmission direction changes, such as the host reading data from the slave; (3) the transmission direction changes multiple times, such as the host reading and writing data to the slave multiple times.

2 Clock Synchronization and Arbitration

The I2C bus can only have one host at any time. When two or more devices on the I2C bus want to become the host at the same time, arbitration is required; the purpose of clock synchronization is to provide a certain clock for arbitration. The synchronization and arbitration of the clock SCL are performed through "wire and". The low level time of SCL depends on the host with the longest low level time, and the high level time depends on the host with the shortest high level time.

The arbitration process is carried out on the data line SDA. When SCL is high, if there is a master sending a low level on the SDA line, the master sending the high level will turn off the output stage. Because the state of the bus is different from that inside itself, the master sending the low level wins the arbitration. Arbitration can last for multiple bits. In the actual communication process, the first stage of arbitration compares the address bit. If multiple masters address the same slave, they continue to compare the data bit (master is the transmitter) or the response bit (master is the receiver). Since the address and data on the I2C bus are determined by the master that wins the bus, no information is lost during the arbitration process. If a master has a slave function, it must immediately switch to the slave state when it loses arbitration because it may be addressed by other masters.

3 I2C bus controller design

The main function of the I2C bus controller is to provide an interface between the microcontroller (μC) and the I2C bus, and to provide physical layer protocol conversion for the communication between the two. In the serial application system, peripheral devices (such as serial E2PROM, LCD, real-time clock, etc.) are connected to the I2C bus, and then connected to the μC through the I2C bus controller. Its typical application, such as the control system of many color TVs now, is based on the I2C bus. In order to make the design clear, this article divides the design of the controller into two parts. One part is the microcontroller (μC) interface, and the other part is the I2C interface, as shown in Figure 2.

The μC interface mainly includes the status register (MBSR), control register (MBCR), address register (MADR), data register (MBDR) and address decoding/bus interface module. The status register indicates the current status of the I2C bus controller, such as whether the transmission is completed, whether the bus is busy, etc. The control register is the main way for μC to control the I2C bus controller. By setting 0/1, the I2C bus controller is enabled, interrupt enabled, master/slave mode selection, start bit generation and other operations are completed. The address register stores the address of the I2C bus controller when it is a slave. The data register is used to store received data or data to be sent.

The core of the I2C interface is the master state machine, which controls the operation of the entire I2C interface. The modules directly connected to the I2C bus include the start/stop bit generation module, the I2C Header register, the I2C data register, and the arbitration and start/stop bit detection module. When the controller is the Master, the start/stop bit generation module is used to generate the start bit and stop bit on the I2C bus; the I2C data register is used to save the data transmitted on the bus; the arbitration and start/stop bit detection module is used to perform arbitration and detect the start/stop bit on the I2C bus to provide input for the master state machine. Other modules include: the I2C status register, which is used to record the status of the I2C bus; the address comparison module, which is used to compare whether the address transmitted on the bus is consistent with the slave address of the local machine. If they are consistent, it means that other hosts are addressing this controller, and the controller must immediately switch to the slave state and send a response bit at the same time.

3.1 μC interface design

The μC interface is used to connect the I2C interface circuit and μC, mainly to realize the signal interaction handshake mechanism between the two. When designing, the state machine provided by VHDL can be used to describe the working state switching in the signal interaction mechanism, as shown in Figure 3(a).

The addresses of the four registers used in the μC interface circuit are 24 bits. The upper 16 bits are the base address (MBASE) of the I2C bus controller, occupying the address space of the μC, and the lower 8 bits are used to distinguish different registers. The register itself is 8 bits. Figure 3 (b1) is the control register, and Figure 3 (b2) is the status register. The figure shows the meaning of each bit.

3.2 I2C interface design

The I2C interface is used to connect the μC interface circuit and the I2C bus. It consists of two state machines: one is the I2C interface master state machine, which is used to perform send and receive operations; the other is the "SCL/SDA/STOP generation" state machine. When the I2C bus controller is the host, this state machine generates SCL/START/STOP signals.

The I2C interface is used to drive and receive the I2C bus. When the I2C bus controller is the host, the I2C interface must drive the bus according to the I2C bus specification; when the bus controller is the slave, the I2C must be able to correctly receive signals that meet the I2C bus specification. The I2C design specification defines the timing of the bus in detail, and the specific values of these parameters in different modes are clearly specified. The state transition of the "SCL/START/STOP generation" state machine is shown in Figure 4, and the transition diagram of the I2C interface master state machine is shown in Figure 5.

4 Simulation and Hardware Implementation

The simulation tool used in this paper is Mentor's ModelSim Plus 6.0 SE, which has a significant advantage in providing a mixed language simulation environment and has been widely used in the industry. In order to test and verify the function of the system, this paper uses the VerilogHDL simulation model (AT24C02.v) of the AT24C02 E2PROM chip (256B 8bit) using the I2C bus protocol provided by Atemel as the slave device object, and uses the VerilogHDL language to build a testbench (test vector) to simulate the designed I2C bus controller.

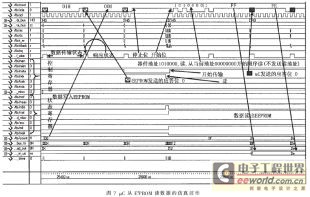

Figures 6 and 7 are simulation waveforms of μC writing/reading data to E2PROM through I2C bus controller (write data FFH~0HH into address 0~255 units, and then read them out in sequential reading mode). When writing to E2PROM, the address of the starting unit to be written needs to be given (00H in Figure 6); when reading sequentially from E2PROM, the starting unit address does not need to be given and reading starts from the current address (after writing 256B data in this article, the address pointer returns to 0). The relevant states and data have been marked in the figure. It can be seen that the designed bus controller fully meets the timing requirements of the standard I2C serial protocol.

The system implementation platform designed in this paper uses the XC95216-10-PQ160 CPLD chip of Xilinx Company, with a total number of logic gates of 4 800. After synthesis, adaptation, layout and routing, the device resources occupied are: macro units 120/216 (56%), registers 111/216 (52%), function blocks 331/432 (77%), product term distributors 544/1080 (51%). It can be seen that the system occupies about half of the resources, which is quite streamlined. After the entire system is downloaded to the CPLD, it runs normally at a clock frequency of 2MHz.

Previous article:Design of variable speed colored light controller based on VHDL

Next article:Application of SPI bus technology based on LPC2103

- Popular Resources

- Popular amplifiers

- Molex leverages SAP solutions to drive smart supply chain collaboration

- Pickering Launches New Future-Proof PXIe Single-Slot Controller for High-Performance Test and Measurement Applications

- CGD and Qorvo to jointly revolutionize motor control solutions

- Advanced gameplay, Harting takes your PCB board connection to a new level!

- Nidec Intelligent Motion is the first to launch an electric clutch ECU for two-wheeled vehicles

- Bosch and Tsinghua University renew cooperation agreement on artificial intelligence research to jointly promote the development of artificial intelligence in the industrial field

- GigaDevice unveils new MCU products, deeply unlocking industrial application scenarios with diversified products and solutions

- Advantech: Investing in Edge AI Innovation to Drive an Intelligent Future

- CGD and QORVO will revolutionize motor control solutions

- Innolux's intelligent steer-by-wire solution makes cars smarter and safer

- 8051 MCU - Parity Check

- How to efficiently balance the sensitivity of tactile sensing interfaces

- What should I do if the servo motor shakes? What causes the servo motor to shake quickly?

- 【Brushless Motor】Analysis of three-phase BLDC motor and sharing of two popular development boards

- Midea Industrial Technology's subsidiaries Clou Electronics and Hekang New Energy jointly appeared at the Munich Battery Energy Storage Exhibition and Solar Energy Exhibition

- Guoxin Sichen | Application of ferroelectric memory PB85RS2MC in power battery management, with a capacity of 2M

- Analysis of common faults of frequency converter

- In a head-on competition with Qualcomm, what kind of cockpit products has Intel come up with?

- Dalian Rongke's all-vanadium liquid flow battery energy storage equipment industrialization project has entered the sprint stage before production

- Allegro MicroSystems Introduces Advanced Magnetic and Inductive Position Sensing Solutions at Electronica 2024

- Car key in the left hand, liveness detection radar in the right hand, UWB is imperative for cars!

- After a decade of rapid development, domestic CIS has entered the market

- Aegis Dagger Battery + Thor EM-i Super Hybrid, Geely New Energy has thrown out two "king bombs"

- A brief discussion on functional safety - fault, error, and failure

- In the smart car 2.0 cycle, these core industry chains are facing major opportunities!

- Rambus Launches Industry's First HBM 4 Controller IP: What Are the Technical Details Behind It?

- The United States and Japan are developing new batteries. CATL faces challenges? How should China's new energy battery industry respond?

- Murata launches high-precision 6-axis inertial sensor for automobiles

- Ford patents pre-charge alarm to help save costs and respond to emergencies

- Circuit type selection for beginners of homemade power amplifier

- 【AT-START-F403A Review】2. Transplant AN0028--Locate HardFault (including simplified version project files)

- 【Silicon Labs Development Kit Review】Secure Code Testing

- Wireless chip faster than 5G is born

- I think the company is wasting money hiring me

- [DIY] Use mosquito repellent to modify wifi repeater, wifi signal booster

- Capacitive Touch Self-Capacitance Buttons, Sliders, Wheels, and Proximity Sensor Demo Board

- How is this comparator with hysteresis implemented?

- Precautions for using chip ferrite beads

- Introduction to Electromagnetic Compatibility by Clayton R.Paul

KA22131D+

KA22131D+

京公网安备 11010802033920号

京公网安备 11010802033920号