introduction

The IEEE 1149.1 boundary scan test standard (commonly referred to as JTAG, 1149.1 or "dot 1") is an industry standard method for testing the characteristics of complex ICs and circuit boards. Most complex electronic systems use the IEEE1149.1 (JTAG) standard in one way or another. To better understand this method, this article will explore how JTAG has been used in system development and design over the years, and use past experience or investment in JTAG access to drive the design to the next generation.

Most complex electronic systems use the IEEE 1149.1 (JTAG) standard in one way or another. If the system uses a complex FPGA or CPLD, then the hardware is almost certainly set up through the JTAG port. If the system uses an emulation tool to debug hardware or software, then the emulation tool is likely to talk to the microprocessor through the JTAG port. And if the system uses ICs packaged in ball grid arrays (BGAs), then JTAG is also the most effective way to test the connection between the BGA device and the underlying printed circuit board.

ICs and boards that support the EEE 1149.1 boundary scan test standard have a 4-wire serial bus that supports JTAG testing (the fifth line is an optional reset line) - TDI (test data input), TDO (test data output), TMS (test mode select) and TCK (test clock). This bus mainly supports structural testing of connections such as solder joints, circuit board vias, short circuits and opens. In addition, many CPLD and FPGA manufacturers also use JTAG as a standard method for in-system programming and configuration of their devices. JTAG not only supports structural (interconnect) testing, but is now a standard method for configuration, programming and mixed-signal testing at the system level.

But most design teams prefer not to use JTAG all at once in new designs, but rather to slowly transition to full use of the JTAG interface in a more manageable way. Some team disciplines make extensive use of the JTAG interface, while others only use a very limited part of it. But each discipline adjusts JTAG according to its own needs. Under the combined effect of various disciplines, several different generations of JTAG applications have been developed, each with its own characteristics and certain enhanced functions.

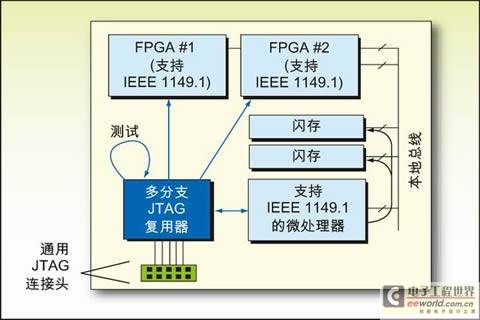

Figure 1: Second generation JTAG application: Using a JTAG multidrop multiplexer to simplify access to multiple JTAG chains.

Because there are various JTAG access requirements, it is imperative that development teams adopt a cross-regulatory JTAG access strategy to maximize the capabilities of JTAG access. This strategy is necessary to achieve a standard approach that can be reused and on which the next generation of products can be built. To better understand this approach, we will explore how JTAG has been used in system development and design over different generations, with the goal of leveraging past experience or investment in JTAG access to drive design to the next generation.

The various stages of JTAG application

In the first phase of JTAG adoption, only certain board features and functions were used, and little work was done to organize and standardize the method.

This is the simplest method, which requires almost no investment in software tools, and usually uses free tools provided by IC manufacturers. JTAG at this stage usually has no or very limited diagnostic functions, and there is no software for generating test or programming vectors. At this time, JTAG access is only used to configure CPLD or program flash memory during production. It can also be used for testing of slightly more complex boards.

However, this is not the lowest cost approach. Because each discipline is likely to use a separate JTAG header for its own needs, multiple JTAG headers will be used on a circuit board, increasing cost and board space. In addition, each discipline may develop its own "home-made" software tools and hardware to interact with JTAG features, which are redundant to other disciplines. Therefore, products developed using this approach are affected by their custom development and are difficult to transfer to new generations of products. If used in production, this approach will also increase cost because it requires multiple insertions.

Many development teams are stuck with this generation of JTAG implementations. Ultimately, as system complexity continues to increase, a JTAG access strategy is necessary to remain competitive.

Second Generation JTAG Applications

In the second generation of JTAG applications, different development team rules govern the adoption of JTAG functionality on new board designs. This phase of JTAG adoption requires a certain level of investment in ATPG (automatic test program generation) software tools (such software tools have robust diagnostic capabilities) to manage the development and delivery of programming and test vectors. Suppliers of these ATPG tools provide support and consulting services from simple per-task vector generation to full-service multi-seat software support for production.

Add a strategic IC device, the JTAG multiplexer, to each board to eliminate multiple 1149.1 headers on the board and manage multiple JTAG paths. This JTAG multiplexer typically takes up less board space than a JTAG header, but simplifies the isolation of components and the organization of scan paths required to improve access efficiency.

For example, developers may want to isolate FPGAs from different vendors in different scan chains to simplify the process of accessing JTAG using tools provided by each vendor. Alternatively, we may want to put the microprocessor in a separate scan chain to maximize the microprocessor's operating speed when the simulation tool is debugging the software or writing programs in flash memory. ATPG vendors provide good support for these devices, so software support is usually simple and directly provides a turnkey solution.

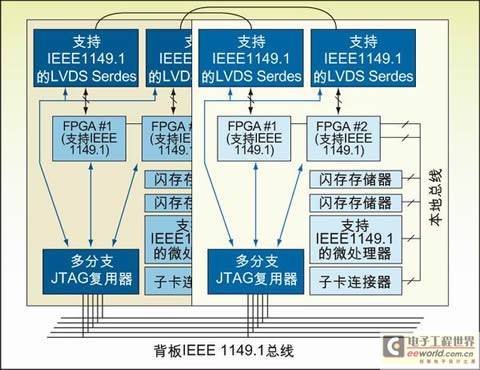

Figure 2: Third generation J: Extends the JTAG bus across the entire backplane to connect multiple boards.

Today our second generation designs all have a single JTAG access point, and in this basic configuration all emulation, configuration and 1149.1 testing of the entire board can be done in one insertion, on a test station, using a PC based system. [page]

A new application of the JTAG bus emerges at this stage - the ability to take advantage of JTAG access throughout the product lifecycle. For example, a vector image of the entire board level can be archived to allow the board to be reprogrammed or debugged when field service is required. The same access can also be used to upgrade FPGA firmware in the field, or to diagnose problems in a FRU (field replaceable unit). Equipment returned to the factory for failure analysis can also use the same set of vector images (and factory or development test stations) to isolate the problem.

If there is a downside to this generation of JTAG applications, it is that development teams often still have a single-board mentality. This is a common mentality that the design team's responsibility is limited to the board and its interface. However, without the ability to move to third-generation JTAG, this JTAG application has a bottleneck that limits the ability to use JTAG to achieve multiple boards.

Third Generation JTAG Applications

The next generation of JTAG access was achieved when the features of JTAG could be used at the system level for multiple boards on a backplane. In this environment, JTAG functionality at the board level could still be implemented independently, but inter-board functionality could also be utilized. This generation of JTAG applications not only facilitated collaboration between design teams with different disciplines on a single board, but also between different board design teams in the entire system. If a JTAG multiplexer was used in the previous generation of JTAG applications, the multiplexer supported multi-drop access. An addressing scheme was used to allow the serial JTAG bus to be used in a multi-drop configuration to provide support for multiple boards. Once JTAG was able to access multiple boards on a backplane, system-level configuration or programming was possible (for example, JTAG could access multiple boards in parallel).

If the driver/receiver pair allows for full-speed JTAG-accessible BIST (built-in self-test), the integrity of the backplane interconnects between boards can be tested, or high-speed LVDS serial links between boards can be verified. Or if these high-speed interconnects are capacitively coupled and the driver/receiver supports it, IEEE 1149.6 testing can be performed.

All of these JTAG functions can be accessed using the same equipment as the second generation - a PC-based JTAG station. The PC-based JTAG station acts as a JTAG master, connected to the JTAG connector on the backplane through a separate set of lines. The master is responsible for driving the test vectors and managing the JTAG access to the devices on the entire backplane.

One of the most interesting new features added to third generation JTAG applications is that the entire system can be accessed through this sideband JTAG channel while the system is running. With this feature, many system-level functions can be realized, such as online "health" status monitoring, fault prediction, fault detection, fault insertion (for failover testing or redundancy testing), and diagnostics.

Fourth Generation JTAG Application

When the transfer and management of test vectors occurs within the system, the highest level of JTAG application is reached, that is, the fourth generation. The fourth generation JTAG application uses an on-board JTAG master controller to drive the backplane JTAG bus. At the same time, on-board memory is used to store test vectors, and a microprocessor is used to drive the JTAG master controller. The multi-board system-level master controller can be located on a separate board, or a master controller can be set on each board for enhanced control performance.

By the fourth generation, all the functions of previous generations of JTAG applications can be implemented remotely, including programming, configuration, interconnect testing and diagnosis, which greatly reduces the cost of field service and support. When the firmware of a field system needs to be upgraded, the new configuration file is downloaded directly to the JTAG master controller, and then the JTAG master controller sends it to the target device through the backplane JTAG bus. Of course, as long as the master controller is disabled during production, a PC-based JTAG access station can still be used, which further enhances flexibility and provides the most access options at all levels of integration.

JTAG access can be initiated externally or internally, or by some system event, such as system power-up or power reset.

Conclusion

The biggest hurdle in JTAG adoption and integration so far has been getting people to realize the need for a strategy based on multiple development disciplines and convincing managers that such a strategy can make economic sense. Once that step is taken and ATPG support and JTAG multiplexing devices are adopted, it will be easier to evaluate or implement new JTAG features incrementally, step by step or generation by generation. Furthermore, if the development team can build on previous experience with JTAG, they will be able to better leverage the power of the JTAG bus.

Increasing the complexity of the JTAG architecture does not have to be a burden on the system. On the contrary, it can fully realize the full value of JTAG as a widely supported, industry-standard method for system-level testing, programming, configuration, and health status monitoring of modern complex electronic systems.

Previous article:Application of Fiber Optic Sensors in Measurement Technology

Next article:ATE Promotes WiMAX RF Testing

- Popular Resources

- Popular amplifiers

- From probes to power supplies, Tektronix is leading the way in comprehensive innovation in power electronics testing

- Seizing the Opportunities in the Chinese Application Market: NI's Challenges and Answers

- Tektronix Launches Breakthrough Power Measurement Tools to Accelerate Innovation as Global Electrification Accelerates

- Not all oscilloscopes are created equal: Why ADCs and low noise floor matter

- Enable TekHSI high-speed interface function to accelerate the remote transmission of waveform data

- How to measure the quality of soft start thyristor

- How to use a multimeter to judge whether a soft starter is good or bad

- What are the advantages and disadvantages of non-contact temperature sensors?

- In what situations are non-contact temperature sensors widely used?

- LED chemical incompatibility test to see which chemicals LEDs can be used with

- Application of ARM9 hardware coprocessor on WinCE embedded motherboard

- What are the key points for selecting rotor flowmeter?

- LM317 high power charger circuit

- A brief analysis of Embest's application and development of embedded medical devices

- Single-phase RC protection circuit

- stm32 PVD programmable voltage monitor

- Introduction and measurement of edge trigger and level trigger of 51 single chip microcomputer

- Improved design of Linux system software shell protection technology

- What to do if the ABB robot protection device stops

- Huawei's Strategic Department Director Gai Gang: The cumulative installed base of open source Euler operating system exceeds 10 million sets

- Download from the Internet--ARM Getting Started Notes

- Learn ARM development(22)

- Learn ARM development(21)

- Learn ARM development(20)

- Learn ARM development(19)

- Learn ARM development(14)

- Learn ARM development(15)

- Analysis of the application of several common contact parts in high-voltage connectors of new energy vehicles

- Wiring harness durability test and contact voltage drop test method

- Simple performance optimization under DSP

- Constant current source composed of field effect tube

- Help: How to use two power supplies to drive the same load

- How are the positive and negative bias voltages generated in this circuit?

- Common mode radiation electromagnetic interference noise suppression

- "Operational Amplifier Parameter Analysis and LTspice Application Simulation" Reading Notes 4 - Beautiful Diamond

- EEWORLD University Hall----Live Replay: Maxim-E-Loomeng explains wearable health monitoring in simple terms

- How to use transistors, field effect transistors, and IGBTs?

- How does 5G achieve such a high transmission rate?

- Selection of RF power tube

UA730HCQM

UA730HCQM

京公网安备 11010802033920号

京公网安备 11010802033920号