In recent years, many CFAR methods have appeared, but not many are actually used. By comparing four representative methods, a constant false alarm processing method that can be implemented and has good detection performance is obtained.

1 Constant false alarm detection method

The constant false alarm detection method uses an adaptive threshold instead of a fixed threshold, and this adaptive threshold can be adaptively adjusted according to the size of the background noise, clutter and interference of the detected point. If the background noise, clutter and interference are large, the adaptive threshold is adjusted higher; if the background noise, clutter and interference are small, the adaptive threshold is adjusted lower to ensure a constant false alarm probability. Therefore, the key to designing radar constant false alarm detectors is to obtain this adaptive threshold method.

There are four common constant false alarm detectors. The unit average constant false alarm (CA-CFAR) detector provides the optimal or quasi-optimal detection of non-fluctuating and Swerling fluctuating targets. However, it will cause an increase in false alarm rate at the edge of clutter, which will lead to a decrease in detection performance. The detection performance at the edge of clutter will be significantly worse. The average selection of small constant false alarm detector (SO-CFAR) is proposed for interference targets, but it is only effective in the case of large interference targets. When two large interferences with little difference appear on both sides of the detection unit, the performance deteriorates, so this solution has great limitations. The average selection of large constant false alarm detector (GO-CFAR) can significantly eliminate the phenomenon of increased false alarm in the clutter transition zone of the ordinary unit average logarithmic constant false alarm circuit. In the case of a single target and uniform clutter background, GO-CFAR is the best among these methods.

2 Constant false alarm circuit design

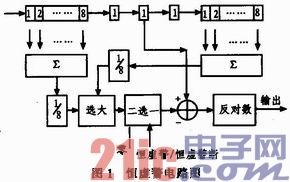

The landing radar constant false alarm circuit adopts the average selection of large constant false alarm detection method. The reference unit N of the constant false alarm detector is 16, as shown in Figure 1.

The design idea is: subtract the average value of the noise from the amplitude of the detection point (adjusted by the false alarm potentiometer), and then perform correlation operations on the signals of the seven adjacent distance units. If it exceeds the false alarm threshold, it will be treated as a useful target signal, output a high level, and open the real-time signal selection branch; if it is lower than the false alarm threshold, it will be treated as a false alarm signal, output a low level, close the real-time signal selection branch, and prevent the video signal from being output. In the figure, there is an empty unit on each side of the measured signal unit, so that the target signal itself does not participate in the estimation of the clutter mean, which can avoid the influence of the measured unit on the clutter intensity estimation value.

[page]

3 Implementation Circuit

ADI's ADSP TS201 processor has a large-capacity memory integrated on-chip and has the signal processing performance of both ASIC and FPGA, which can support the implementation of this design. Its implementation circuit composition is shown in Figure 2.

The first-in-first-out register module FIFO1 stores the echo data of the first 8 distance units, and the first-in-first-out register module FIFO2 stores the average value of the sum of the echo data of the last 8 distance units. The input data enters the chip, and after the accumulation circuit (using the scheme of adding new values and subtracting old values), the sum of the data of the first 8 distance units is entered into the register Rag1 when the CP4 pulse arrives. At the same time, the average value of the sum of the data of the last 8 distance units is also taken out from FIFO2 and stored in the register Rag2. The larger of the two is selected and stored in the register Pag5. At the same time, the measured data is also stored in the register Rag4. The two data are subtracted, and the difference is sent out of the chip, and then through the anti-logarithmic circuit to obtain the constant false alarm output.

The data accumulator of 8 distance units should complete the initialization process within the first 8 distance units of zero distance: add the new value and subtract zero. After 8 distance units, the accumulator register will keep the sum of the data of the first 8 distance units. Starting from the 9th distance unit, the "add new and subtract old" operation will be performed, so that the accumulator and register always save the sum of the data of the latest 8 distance units. In this way, only after 19 distance units, the average value of the sum of the data of the last 8 distance units is valid. Therefore, two clear signals need to be generated inside the FPGA: the FIFO1 output register clear signal is CLR1, and the FIFO2 output register clear signal is CLR2. The heading antenna and the glide antenna of the radar work alternately at a frequency of 1 Hz. When the antenna is switched, the data of the other antenna scanning is still retained in its memory. These data need to be discarded, and the new data after scanning should be stored and continuously updated. When the information of antenna switching is received, two clear signals are generated: CLR1 and CLR2, which clear the two memories respectively.

The DC circuit is estimated when the radar is inactive and 16 distance units are taken. When the level is in constant false alarm and non-constant false alarm working states, the DC level remains basically unchanged.

4 Simulation Verification

Visual DSP++, a platform specially developed for ADI's DSP devices, is used for programming simulation to verify the function of the designed constant false alarm circuit. A set of radar raw data is input, processed, and the detector is verified based on the output waveform. The input signal waveform is shown in Figure 3, and the output signal waveform is shown in Figure 4.

As shown in Figure 3, the target signal is buried in various noises and must be filtered to obtain the required signal waveform. The radar signal data is input into the simulation system. From the output signal waveform in Figure 4, the waveform is relatively ideal and achieves the expected goal.

Through simulation verification, it is found that the output signal has filtered out most of the clutter, and the obtained signal is basically consistent with the required target signal. The result is relatively ideal, indicating that the design is relatively reasonable.

5 Conclusion

This paper focuses on introducing a method for implementing constant false alarm processing of landing radar, and designs the circuit on FPGA. Finally, it is verified through simulation and achieves good results.

Previous article:Design and implementation of marine survey and measurement monitoring system based on Beidou satellite

Next article:Design of Universal Test System for Electronic Time Fuze Based on PCI-9846

- Keysight Technologies Helps Samsung Electronics Successfully Validate FiRa® 2.0 Safe Distance Measurement Test Case

- From probes to power supplies, Tektronix is leading the way in comprehensive innovation in power electronics testing

- Seizing the Opportunities in the Chinese Application Market: NI's Challenges and Answers

- Tektronix Launches Breakthrough Power Measurement Tools to Accelerate Innovation as Global Electrification Accelerates

- Not all oscilloscopes are created equal: Why ADCs and low noise floor matter

- Enable TekHSI high-speed interface function to accelerate the remote transmission of waveform data

- How to measure the quality of soft start thyristor

- How to use a multimeter to judge whether a soft starter is good or bad

- What are the advantages and disadvantages of non-contact temperature sensors?

- Innolux's intelligent steer-by-wire solution makes cars smarter and safer

- 8051 MCU - Parity Check

- How to efficiently balance the sensitivity of tactile sensing interfaces

- What should I do if the servo motor shakes? What causes the servo motor to shake quickly?

- 【Brushless Motor】Analysis of three-phase BLDC motor and sharing of two popular development boards

- Midea Industrial Technology's subsidiaries Clou Electronics and Hekang New Energy jointly appeared at the Munich Battery Energy Storage Exhibition and Solar Energy Exhibition

- Guoxin Sichen | Application of ferroelectric memory PB85RS2MC in power battery management, with a capacity of 2M

- Analysis of common faults of frequency converter

- In a head-on competition with Qualcomm, what kind of cockpit products has Intel come up with?

- Dalian Rongke's all-vanadium liquid flow battery energy storage equipment industrialization project has entered the sprint stage before production

- Allegro MicroSystems Introduces Advanced Magnetic and Inductive Position Sensing Solutions at Electronica 2024

- Car key in the left hand, liveness detection radar in the right hand, UWB is imperative for cars!

- After a decade of rapid development, domestic CIS has entered the market

- Aegis Dagger Battery + Thor EM-i Super Hybrid, Geely New Energy has thrown out two "king bombs"

- A brief discussion on functional safety - fault, error, and failure

- In the smart car 2.0 cycle, these core industry chains are facing major opportunities!

- The United States and Japan are developing new batteries. CATL faces challenges? How should China's new energy battery industry respond?

- Murata launches high-precision 6-axis inertial sensor for automobiles

- Ford patents pre-charge alarm to help save costs and respond to emergencies

- New real-time microcontroller system from Texas Instruments enables smarter processing in automotive and industrial applications

- Received the board and posted the [Qinheng RISC-V core CH582] development board

- Interesting Facts (1) Diode Reverse Recovery

- [Rawpixel RVB2601 development board trial experience] Breathing light and red and blue warning light

- Novice Question

- [Automatic clock-in and walking timing system based on face recognition] Unboxing Post 2: ESP32-EYE development board unboxing experience

- Evaluation Weekly Report 20211206: Anxinke UWB indoor positioning module is here, Qinheng CH582 is coming, RCSN plays AT32F437

- I encountered some difficulties in the process of making a magnetically controlled lamp for a model, and I would like to ask for help from an expert.

- Evaluation of domestic FPGA Gaoyun GW1N-4 series development board - Software Part 3

- Hi3518 Rebirth (Part 3) http+mjpeg bug fix in minihttp

- Advantages of the STOP function in low-noise data acquisition applications

Theory and Application of Multi-source Information Fusion

Theory and Application of Multi-source Information Fusion

京公网安备 11010802033920号

京公网安备 11010802033920号