, the system requires fast speed, good real-time performance, and high data processing accuracy. This paper plans the overall solution of the high-speed data acquisition system based on this principle, and uses the TMS320VC5509 DSP chip + CPLD controllable logic produced by TI as the core part of the system. The system mainly consists of 4 parts: DSP minimum system, CPLD module, signal conditioning and A/D conversion module, display module, and host computer system. The system framework diagram is shown in Figure 1.

Among them, the input signal can be in various forms, such as audio signals, encoded digital signals, compressed image signals, or signals output by various sensors. Then it is input into the A/D converter for analog-to-digital conversion after filtering and amplification circuits, and finally input into the DSP for calculation and processing.

In addition, the DSP can communicate and process data with the host computer, and can also expand external devices such as displays and keyboards to operate the system more conveniently.

The system consists of DSP, power supply and reset circuit, clock circuit, EMIF bus interface and simulation interface. In addition, it can be connected to peripheral modules such as CPLD, A/D, display, HPI host interface, etc., and the entire hardware system is basically completed. The following will select the various parts of the hardware.

1 Selection of DSP chip

In the design of DSP system, the selection of DSP chip is very important. Only when the appropriate DSP is selected can the next step of peripheral circuit design be carried out. In general, the selection of DSP chip is determined according to the needs of the system, mainly considering the processing speed, power consumption, capacity of program memory and data memory, and on-chip resources, such as the number of timers, number of I/O ports, number of terminals, number of DMA channels, etc.

This article selects the DSP chip produced by TI. At present, TI has three series of mainstream DSP chips, namely C2000, C5000, and C6000 series. The C2000 series chips are generally used in the control field; the C5000 series is a 16-bit fixed-point DSP with a speed of 40-200 MIPS, programmable, low-power and high-performance DSP, mainly used for wired or wireless communications; the C6000 series is a high-performance DSP. It combines the current DSP's high cost performance and low power consumption, but the price is relatively high.

In summary, the TMS320VC5509 chip produced by TI can be selected as the DSP chip of this system. The following briefly summarizes the main features of the TMS320CV5509 chip:

1) The TMS320VC5509 DSP is a high-performance, low-power fixed-point DSP. Its internal bus consists of 1 program bus, 3 data buses, and two data write buses. These buses enable the DSP to achieve high performance of reading 3 data and writing two data in one cycle. Its core voltage is 1.6 V when the clock frequency is 200 MHz, and the pin voltage is in the range of 2.7 to 3.3 V. The lower core voltage and pin voltage realize the low power consumption of DSP.

2) TMS320VC5509 DSP has rich on-chip peripheral functions, including dual-channel 10-bit A/D converter, 1 external memory interface (EMIF) that can access asynchronous memory and synchronous memory, 3 multi-channel buffered serial ports (MCBSP), USB interface, I2C interface, master-slave device (HPI) interface, etc. The rich peripherals and pins lay the foundation for the expansion of DSP peripherals.

2 System hardware equipment selection and design

2.1 A/D conversion module

In the data acquisition system, the A/D conversion module is the most important part of the system. Its performance directly affects the quality of the entire system. When selecting an A/D converter, the following aspects should be considered: resolution, conversion accuracy, conversion time and converter price.

Since this article is designed for a high-speed data acquisition system, the AD conversion chip ADS5422 from TI is selected after comprehensive consideration.

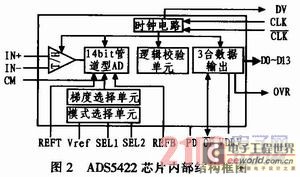

ADS5422 is a 14-bit high-speed AD conversion chip with a maximum sampling frequency of up to 62 Msps. It is powered by a single -5 V power supply. When the sampling frequency is 10 MHz, its maximum dynamic range is 82 dB, and the maximum signal-to-noise ratio reaches 72 dB. Its digital output can be directly connected to a 5 V or 3.3 V CMOS chip. The peak-to-peak value of the analog input is 4 V, and 0.5-4.5 V analog quantities can be directly input. The package form is a 64-pin flat square package.

AD can accept 3 V or 5 V TTL or CMOS levels. DSP can provide clock signals for AD converters, and various characteristic quantities of the input clock can be set by software, including clock frequency, high-level width, etc., which can basically meet the clock signal requirements of AD5422. [page]

The internal structure block diagram of the ADS5422 chip is shown in Figure 2.

The analog signal input of A/D can be single-ended input or differential input. Compared with the two methods, the single-ended input method has simple wiring, but poor noise resistance, while the differential input method has strong noise resistance, which can minimize signal noise and electromagnetic interference.

2.2 DSP power supply design

The TMS320VC5509 chip DSP adopts low-voltage separation power supply, which can greatly reduce the power consumption of the DSP chip. The chip core is powered by 1.8 V voltage, and the external I/O is powered by 3.3 V voltage. Based on this, TI's TPS73HD318 chip can be selected. This chip is a dual-output low-dropout (LDO) regulator with a maximum current of 750 mA. The dual output of TPS7 0451 can be configured into two different outputs, outputting 1.8 V and 3.3 V voltages respectively. Figure 3 is a schematic diagram of the system's power supply circuit.

[page]

2.3 JTAG Circuit

JTAG is a boundary-scan test method based on the IEEE 1149.1 standard. Combined with the emulator and emulation software, it can access all DSP resources, including on-chip registers and all memories, thereby providing a real-time hardware simulation and debugging environment, which is convenient for developers to debug the system. In most cases, if the connection cable between the development board and the emulator does not exceed 6 inches, the connection method in Figure 4 can be used. However, it should be noted that the EMU0 and EMU1 pins of the DSP require pull-up resistors, and the recommended value is 4.7 kΩ or 10 kΩ. If the connection cable between the DSP and the emulator exceeds 6 inches, an additional buffer drive circuit is required.

2.4 Clock Circuit

The external clock of TMS320VC5509 is input from the CLKIN pin, and this signal is modified internally to generate the output clock of the desired frequency. The clock generator sends this output clock (i.e., CPU clock) to the CPU, peripherals, and other internal modules. The CPU clock can also be divided by a programmable clock divider and output at the CLKOUT pin. There is also a clock mode register (CLKMD) in the clock generator to control and monitor the clock generator. It can control the clock generator to enter two working modes:

1) Bypass mode, the PLL is bypassed, and the frequency of the output clock is equal to the frequency of the input clock divided by 1, 2, or 4.

2) Lock mode, the input clock can be multiplied or divided by a coefficient to obtain the desired output frequency, and the output clock phase is locked with the input signal.

In the locked mode, the output frequency is calculated by the following formula:

Output frequency = (PLL MULT / (PLL DIV + 1)) × input clock frequency

Here, the clock generator can be selected to work in the locked mode, that is, PLL ENABLE of CLKMD is 1, and the external oscillator crystal can be 10~20 MHz. According to the external oscillator crystal and the internal clock signal of DSP, the corresponding PLLMULT and PLL DIV values can be calculated. Figure 5 shows the external clock circuit of DSP.

[page]

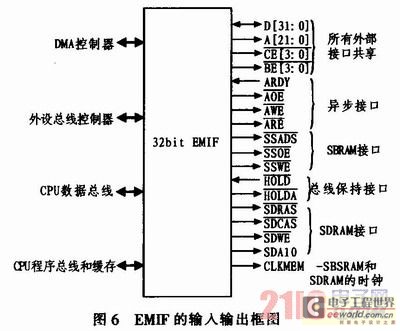

2.5 DSP external memory expansion

In the TM320VC5509 chip, there is an external memory interface (EMIF), which provides a seamless interface for three types of memory: asynchronous memory, including ROM, FLASH and asynchronous SRAM; synchronous burst SRAM (SBSRAM), which works at 1 or 1/2 times the CPU clock frequency; synchronous DRAM (SDRAM), which can work at 1 or 1/2 times the CPU clock frequency, and can expand the memory according to system needs. Figure 6 is the input and output block diagram of EMIF.

For example, DSP can be expanded with FLASH, and FLASH can be used as its external program memory for the bootloader (BOOTLOAD) when DSP is powered on. Its function is to load the program stored in FLASH into DSP for execution. In connection with DSP, the address and data bus of FLASH can be connected to the EMIF interface bus of DSP, and the chip select signal of FLASH can be connected to the CE1 pin of DSP, configured as CE1 space, and the CE1 pin is low level after power-on reset. In addition, the read and write signals of FLASH are respectively connected to the read and write signal pins of EMIF interface.

Of course, according to the needs of the system, the EMIF interface can also be used to expand other memories. For specific methods, please refer to the relevant technical manual.

2.6 Other peripheral hardware circuits

1) According to the requirements of the system, the DSP system can be expanded with a liquid crystal display module. At present, there are many types of liquid crystal display modules, and users can completely choose a suitable liquid crystal display module according to their own needs.

However, since LCD is a typical slow device (relative to DSP), it will take a lot of time to interface with a high-speed microprocessor, which is not allowed. If the DSP processing margin is small, you can consider using CPLD to design a bidirectional fast channel between DSP and LCD to realize the control of LCD, that is, send the data processed by DSP to CPLD, and then CPLD controls and simulates the read and write timing of LCD to complete the display of data, which can greatly save DSP resources.

2) On the development board of the system, a signal light can be added to indicate the power supply status of the minimum system. When the power indicator light is abnormal, the power can be cut off in time to protect the circuit from damage. Usually, you can set a +5 V power indicator light (normal power supply of the circuit board), a voltage conversion output 3.3 V indicator light (normal I/O power supply), a voltage conversion output 1.8 V indicator light (normal core power supply) and other signal indicators.

3 Summary

This article briefly introduces the main hardware design of the data acquisition system with TMS320VC5509 chip as the core processor. In practical applications, the appropriate hardware circuit should be designed according to the system needs, and then the software and algorithm should be written to meet the system requirements.

In addition, the system can be further improved according to the requirements of different signal processing: such as adding a USB controller, improving the bus function and further studying the expansion of external memory, so that the system can be more widely used in complex engineering fields.

Previous article:Circuit design and implementation of laser spot measurement system

Next article:Design of Dynamic Weighing Signal Acquisition System

- Keysight Technologies Helps Samsung Electronics Successfully Validate FiRa® 2.0 Safe Distance Measurement Test Case

- From probes to power supplies, Tektronix is leading the way in comprehensive innovation in power electronics testing

- Seizing the Opportunities in the Chinese Application Market: NI's Challenges and Answers

- Tektronix Launches Breakthrough Power Measurement Tools to Accelerate Innovation as Global Electrification Accelerates

- Not all oscilloscopes are created equal: Why ADCs and low noise floor matter

- Enable TekHSI high-speed interface function to accelerate the remote transmission of waveform data

- How to measure the quality of soft start thyristor

- How to use a multimeter to judge whether a soft starter is good or bad

- What are the advantages and disadvantages of non-contact temperature sensors?

- Innolux's intelligent steer-by-wire solution makes cars smarter and safer

- 8051 MCU - Parity Check

- How to efficiently balance the sensitivity of tactile sensing interfaces

- What should I do if the servo motor shakes? What causes the servo motor to shake quickly?

- 【Brushless Motor】Analysis of three-phase BLDC motor and sharing of two popular development boards

- Midea Industrial Technology's subsidiaries Clou Electronics and Hekang New Energy jointly appeared at the Munich Battery Energy Storage Exhibition and Solar Energy Exhibition

- Guoxin Sichen | Application of ferroelectric memory PB85RS2MC in power battery management, with a capacity of 2M

- Analysis of common faults of frequency converter

- In a head-on competition with Qualcomm, what kind of cockpit products has Intel come up with?

- Dalian Rongke's all-vanadium liquid flow battery energy storage equipment industrialization project has entered the sprint stage before production

- Allegro MicroSystems Introduces Advanced Magnetic and Inductive Position Sensing Solutions at Electronica 2024

- Car key in the left hand, liveness detection radar in the right hand, UWB is imperative for cars!

- After a decade of rapid development, domestic CIS has entered the market

- Aegis Dagger Battery + Thor EM-i Super Hybrid, Geely New Energy has thrown out two "king bombs"

- A brief discussion on functional safety - fault, error, and failure

- In the smart car 2.0 cycle, these core industry chains are facing major opportunities!

- Rambus Launches Industry's First HBM 4 Controller IP: What Are the Technical Details Behind It?

- The United States and Japan are developing new batteries. CATL faces challenges? How should China's new energy battery industry respond?

- Murata launches high-precision 6-axis inertial sensor for automobiles

- Ford patents pre-charge alarm to help save costs and respond to emergencies

- FPGA_Journey_Flowing Light.pdf

- 28335 Procedure

- TI Precision Labs - Motor Drivers

- Improving LED Human-Machine Interface Design Using RGBW LED Drivers

- TMU Introduction and Usage

- Tracking 0 ~ ± 15V regulated power supply

- The reason why there is a big difference in efficiency between electromagnetic excitation motors and permanent magnet motors

- Do you also design a power supply for pulse loads in this way? If you have any questions, please come in~

- 111 uses of Tektronix 3 Series MDO mixed domain oscilloscopes. Do you know them all?

- Talk about the MSP430 library about UART asynchronous serial port

Data Acquisition System

Data Acquisition System Interactive Design between Arduino and LabVIEW

Interactive Design between Arduino and LabVIEW

京公网安备 11010802033920号

京公网安备 11010802033920号