This project is a solution verification version design for the Lichuang Mall AD9850BRSZ-REEL ( product number: C480623 ).

This project is a sample project for the Solicitation Order for Lichuang EDA open source hardware platform solution verification module .

AD9850 is a direct frequency synthesizer produced by AD company with a maximum clock of 125MHz and using advanced CMOS technology. It is mainly composed of three parts: programmable DDS system, high-performance digital-to-analog converter (DAC) and high-speed comparator. It can realize full digital Programmable frequency synthesis.

The AD9850 chip includes high-speed DDS, 10-bit DAC, and frequency/phase data register. Data input register. Comparator, etc., under the 125MHz reference clock, the AD9850 can generate a 32-bit frequency adjustment control word through the high-speed DDS core chip to make the output frequency of the AD9850 reach 0.0291Hz; and can provide 5bits of phase control bits, which can make the output The phase changes in increments of 180°.90°.45°.22.5°.11.25° or any combination thereof. The circuit structure of the AD9850 allows the generation of an output with a frequency value that is half of the reference clock, and the output frequency can be numerically controlled It changes at a rate of 23,000,000 new frequencies per second. The comparator in the AD9850 chip is a device that can receive the DAC conversion output after external low-pass filtering and produce a low-jitter square wave output. Therefore, the AD9850 is used as a clock generator. The device is very convenient. Frequency/Phase Data Register. The data input register inputs and updates the frequency control word under the control of the external frequency update clock and word load clock, so that the chip outputs the required frequency and phase.

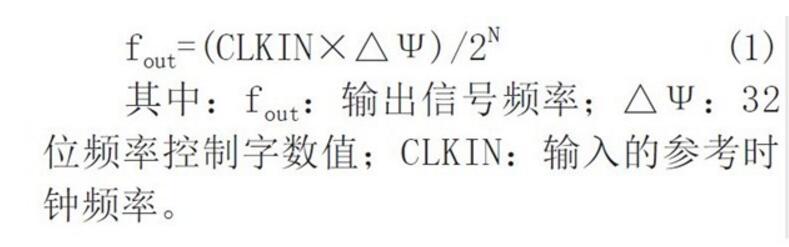

AD9850 uses a 32-bit phase accumulator. The relationship between input, output, reference clock and frequency control word is as follows:

AD9850 has a 40-bit control word, 32 bits for frequency control, and 5 bits for phase control. 1 bit is used for power sleep (Powerdown) control, and 2 bits are used to select the working mode. These 40-bit control words can be input to the AD9850 in parallel mode or serial mode. In the parallel loading mode, the available data is input to the register through the 8-bit bus D0...D7, and after repeated 5 times, the rising edge of FQ-UD Load the 40-bit data from the input register into the frequency/phase data register (update the DDS output frequency and phase), and at the same time reset the address pointer to the first input register. Then load 8-bit data on the rising edge of W-CLK, and point the pointer to the next input register. After 5 consecutive rising edges of W-CLK, the edge of W-CLK will no longer take effect until the reset signal or FQ-UD The rising edge resets the address pointer to the first register. In the serial input mode, the rising edge of W-CLK serially shifts in one bit of data from pin 25. After shifting 40 bits, the output frequency and phase can be updated with an FQ-UD pulse.

The reset (RESET) signal of the AD9850 is active high, and the pulse width is not less than 5 reference clock cycles. The reference clock frequency of the AD9850 is generally much higher than the clock frequency of the microcontroller, so the reset (RESET) terminal of the AD9850 can be directly connected to the reset terminal of the microcontroller. The two control bits used to select the working mode, whether parallel or serial, are best written as 00. 10, 01 in parallel and 10, 01, 11 in serial are reserved control words for factory testing. Inadvertently Use may result in unpredictable consequences.

Welded finished product

Connect to the microcontroller for testing, serial sine wave 1kHz output

2kHz output

244kHz output

245kHz output

After simple verification, the AD9850 controlled by an external microcontroller can accurately output the desired frequency. Due to the bandwidth of the oscilloscope, higher frequencies were not tested.

All reference designs on this site are sourced from major semiconductor manufacturers or collected online for learning and research. The copyright belongs to the semiconductor manufacturer or the original author. If you believe that the reference design of this site infringes upon your relevant rights and interests, please send us a rights notice. As a neutral platform service provider, we will take measures to delete the relevant content in accordance with relevant laws after receiving the relevant notice from the rights holder. Please send relevant notifications to email: bbs_service@eeworld.com.cn.

It is your responsibility to test the circuit yourself and determine its suitability for you. EEWorld will not be liable for direct, indirect, special, incidental, consequential or punitive damages arising from any cause or anything connected to any reference design used.

Supported by EEWorld Datasheet