Abstract: This paper introduces a system structure that uses DSP chip TMS320C6711D as the processing core and high-speed A/D chip ADS8364 to realize multi-channel synchronous sampling and analysis of power system. The hardware design of the system is introduced in detail. Through testing and use, it is shown that the design is easy to use, has good real-time performance, strong anti-interference, high measurement accuracy, and excellent cost performance. It can be widely used in power systems.

Keywords: DSP; AC synchronous sampling; power quality

The collection of basic electricity is undoubtedly an important link as a prerequisite for real-time control, monitoring, and dispatching automation of power systems. How to accurately and quickly collect and analyze various analog quantities in the power system to achieve real-time alarm or even prevent accidents is a hot topic in power system research.

The sampling and analysis system described in the article uses the TMS320C6711D of TI, an American company, as the main computing core device. This chip has a high-speed floating-point computing capability of 900 MHz FLOPS and an instruction set similar to RISC. It uses the VeloeiTI advanced VLIW structure core: 8 independent functional units, 6 ALUs, 2 multipliers, and floating-point support for IEEE standard single-precision and double-precision floating-point operations. It can execute 8 32-bit instructions per cycle and has 32 32-bit general registers.

The core of the A/D conversion circuit is the chip ADS8364, which is a high-speed, low-power, 6-channel synchronous sampling conversion device. It is an analog-to-digital conversion chip with a 16-bit high-speed parallel interface. Each ADS8364 consists of 3 ADCs with a conversion rate of 250 ks·s-1. Each ADC has 2 analog input channels, and each channel has a sample-and-hold device. The 3 ADCs can form 3 pairs of analog inputs, and the input signals can be sampled and held simultaneously. In addition, the pins also have a 2.5 V voltage interface that can be used to provide a reference voltage. Since the 6 channels can be sampled simultaneously, it is suitable for applications where multiple signals need to be collected simultaneously.

When ADS8364 uses a 5 MHz external clock to control the conversion, its sampling rate is 250 kHz, which corresponds to a maximum throughput of 4 μs, that is, sampling and conversion take a total of 20 clock cycles. Therefore, in order to obtain the maximum output data rate, the data can be read during the next conversion.

1 System design based on DSP and high-speed A/D

The entire system can be divided into four parts: three-phase synchronous phase-locked circuit, A/D conversion circuit, DSP core circuit and HPI bus connection. It realizes data acquisition and various core algorithms, and can transmit the calculated data in real time through the high-speed data bus (HPI). The schematic diagram is shown in Figure 1.

1.1 Three-phase synchronous phase-locked circuit

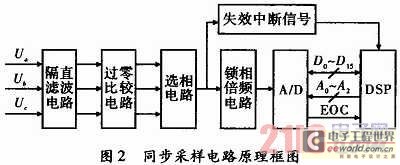

The synchronous circuit mainly completes the function of frequency tracking. This circuit can ensure that 256 sampling signals are provided to the A/D within one power frequency cycle, thereby realizing the function of synchronous phase-locked.

As shown in Figure 2, the voltage signal obtained through the voltage transformer passes through the DC isolation filter circuit, and then enters the zero-crossing comparator to obtain a TTL-level square wave signal with the same frequency as the input signal. After that, it passes through the shaping circuit to obtain a CMOS-level square wave with a steep rising edge, regular waveform and the same frequency as the input voltage signal, and enters the phase selection circuit.

The phase selection circuit can automatically select the phase with voltage, and generate a zero-crossing signal based on the voltage of the selected phase to provide it to the subsequent PLL circuit to achieve 256 times phase-locked frequency sampling. In the case of frequency changes, the circuit can also ensure 256 points of sampling per cycle. The phase selection circuit takes the voltage of phase A as the most prioritized phase. When there is voltage in phase A, the zero-crossing signal of phase A is used as the synchronization signal to lock phases B and C; after phase A loses power, the zero-crossing signal of phase B is used as the synchronization signal to lock phase C; phases A and B lose power at the same time, and the zero-crossing signal of phase C is used as the synchronization signal. When the synchronization signal is switched between phases, due to the delay of the circuit parameters and the line itself, a locked blank will appear. At this time, an interrupt signal will be generated to notify the DSP, and the DSP will provide the synchronous sampling signal for this blank time. When all three-phase voltages are lost, the DSP will autonomously generate a synchronous sampling signal and perform 256-point sampling at a 50 Hz power frequency, as shown in Figure 2.

1.2 A/D analog-to-digital conversion circuit

Analog conversion, signal conditioning and A/D conversion constitute the entire A/D analog-to-digital conversion circuit. This circuit is the basis of the entire sampling system. It realizes the signal isolation and conversion of the secondary side of the voltage transformer and current transformer suitable for A/D sampling, as shown in Figure 2. The A/D converter converts the conditioned analog signal into the corresponding binary digital information that can be recognized by the DSP.

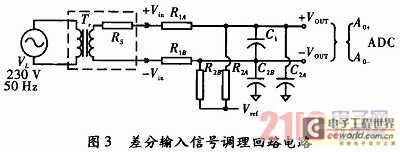

The transformer signal adopts a differential input method, which has a strong anti-interference ability. The schematic diagram of its connection is shown in Figure 3. When the ±Vin input is a maximum AC signal of -2.5 to 2.5 V and Vref uses a +2.5 V reference, the conditioned output ±Vout range is 0 to 5 V. The circuit parameters can just meet the input requirements of the selected A/D chip ADS8364.

After the A/D conversion is completed, an interrupt signal EOC is generated to notify the DSP to read the data. After the DSP selects the corresponding A/D chip and related channels through the address, it reads back the 16-bit data. The DSP uses the real-time data of the three-phase voltage and three-phase current collected by the A/D converter as the basis for calculation.

[page]

1.3 DSP core circuit

DSP and its peripheral interface circuit are the core of the whole system, which consists of 32-bit floating-point DSP, oscillator + phase-locked frequency multiplier, voltage monitoring and watchdog circuit, off-chip SDRAM, off-chip Flash, off-chip ferroelectric memory, etc. As shown in Figure 4, the circuit realizes the power-on reset, watchdog, voltage detection and system reset functions of the extended management chip of the whole system.

The external 25 MHz oscillator provides synchronized 150 MHz and 3.125 MHz operating clocks to the DSP and AD converter respectively through a frequency multiplication chip and a binary counter.

After the DSP is powered on and reset, it first automatically loads the Bootload program of the first 1 kB of Flash through EDMA, and writes the entry address of the subsequent loading program in the Bootload program to realize the automatic loading of the application. After that, the SDRAM is self-checked to avoid abnormal operation or data errors caused by SDRAM unit errors. At the same time, SDRAM is also the place where the DSP stores A/D sampling data, performs intermediate and final results of data calculation output, and caches communication data.

FRAM can save data when power is off, and the number of read and write times exceeds 1012, and it can write without delay. The FRAM is connected through the McBSP interface of the DSP to store parameters such as the DC offset of each analog channel of the ADC, the data of the precision correction, and the wiring method during operation.

The data processed by the DSP interacts with the host computer through its internal integrated host interface (HPI). The host can access the shared RAM randomly or in blocks through DMA or EDMA7.

2 Software Design of Sampling System

The software design of the system is based on the TMS320C6711D chip instruction set, making full use of its high speed, support for floating-point operations, pipeline operations, etc. It adopts mixed programming of C language and assembly language, and follows the programming ideas of modularization, top-down, and gradual refinement. The program uses modular design, mainly including three modules: acquisition module, main loop module and HPI interaction protocol module. The flow charts are shown in Figures 5 to 7 respectively.

In the main loop module, the DSP's CPU and peripherals are first initialized and self-checked. After the system is initialized, the DSP continues to output software synchronization signals. The CPLD determines whether the ADC sampling signal is the synchronous sampling signal output by the hardware or the sampling signal output by the DSP; and stores the self-check results in the self-check result area of the HPI interactive protocol module for the expansion MCU to read.

In the interrupt service subroutine, DSP reads the data obtained after ADC conversion into the allocated data buffer. After the total acquisition time is up, the data ready flag is used to notify the main loop module that data can be extracted for calculation. The main loop module processes the data, then calls each calculation subroutine to calculate the basic quantity of the power system and other indicators of power quality, and stores the calculation results in the buffer. After a main loop is completed, the results are moved to the data interaction area of HPI for the expansion MCU to read. The program flowchart is shown in Figures 5 to 7.

3 Conclusion

This system has passed various functional tests and has been successfully used in the power quality monitoring products of a well-known domestic electric meter company. It accurately detects various power quality parameters such as voltage and current effective value, power, 2 to 50 voltage and current harmonics effective value, phase, voltage fluctuation and flicker, three-phase imbalance, etc. The basic accuracy reaches 0.2 level, and the harmonic monitoring accuracy reaches A level. This design scheme is easy to use, has good real-time performance, strong anti-interference ability, high measurement accuracy, and excellent cost performance. It can be widely used in power systems.

Previous article:Restaurant Customer Service Terminal

Next article:DSP applications expand to heavy equipment

- Huawei's Strategic Department Director Gai Gang: The cumulative installed base of open source Euler operating system exceeds 10 million sets

- Analysis of the application of several common contact parts in high-voltage connectors of new energy vehicles

- Wiring harness durability test and contact voltage drop test method

- Sn-doped CuO nanostructure-based ethanol gas sensor for real-time drunk driving detection in vehicles

- Design considerations for automotive battery wiring harness

- Do you know all the various motors commonly used in automotive electronics?

- What are the functions of the Internet of Vehicles? What are the uses and benefits of the Internet of Vehicles?

- Power Inverter - A critical safety system for electric vehicles

- Analysis of the information security mechanism of AUTOSAR, the automotive embedded software framework

Professor at Beihang University, dedicated to promoting microcontrollers and embedded systems for over 20 years.

Professor at Beihang University, dedicated to promoting microcontrollers and embedded systems for over 20 years.

- Innolux's intelligent steer-by-wire solution makes cars smarter and safer

- 8051 MCU - Parity Check

- How to efficiently balance the sensitivity of tactile sensing interfaces

- What should I do if the servo motor shakes? What causes the servo motor to shake quickly?

- 【Brushless Motor】Analysis of three-phase BLDC motor and sharing of two popular development boards

- Midea Industrial Technology's subsidiaries Clou Electronics and Hekang New Energy jointly appeared at the Munich Battery Energy Storage Exhibition and Solar Energy Exhibition

- Guoxin Sichen | Application of ferroelectric memory PB85RS2MC in power battery management, with a capacity of 2M

- Analysis of common faults of frequency converter

- In a head-on competition with Qualcomm, what kind of cockpit products has Intel come up with?

- Dalian Rongke's all-vanadium liquid flow battery energy storage equipment industrialization project has entered the sprint stage before production

- Allegro MicroSystems Introduces Advanced Magnetic and Inductive Position Sensing Solutions at Electronica 2024

- Car key in the left hand, liveness detection radar in the right hand, UWB is imperative for cars!

- After a decade of rapid development, domestic CIS has entered the market

- Aegis Dagger Battery + Thor EM-i Super Hybrid, Geely New Energy has thrown out two "king bombs"

- A brief discussion on functional safety - fault, error, and failure

- In the smart car 2.0 cycle, these core industry chains are facing major opportunities!

- The United States and Japan are developing new batteries. CATL faces challenges? How should China's new energy battery industry respond?

- Murata launches high-precision 6-axis inertial sensor for automobiles

- Ford patents pre-charge alarm to help save costs and respond to emergencies

- New real-time microcontroller system from Texas Instruments enables smarter processing in automotive and industrial applications

- My creative plan and functional implementation plan

- The more I read, the more I like these sentences. Each sentence is more philosophical than the last, and each sentence is very inspiring.

- 【Want to buy】College students want to buy ATmega16 development board

- AC-DC controllers, gate drivers, digital isolators

- kernel make zImage compilation failed

- Importance of CMTI parameter for isolation driver selection

- May I ask, what is the difference between ICP programming, JTAG programming and SWD programming?

- 2019 Tektronix OPEN-DAY opens: Hold your DUT and test thoroughly

- The relationship between FPGA memories

- Show off the Sony headphones I got from EEWORLD

Key technologies for inverter control of new energy access to smart grids

Key technologies for inverter control of new energy access to smart grids Three-Phase 11 kW PFC + LLC Electric Vehicle On-Board Charging (OBC) Platform User Manual (ONSEMI Semiconductor)

Three-Phase 11 kW PFC + LLC Electric Vehicle On-Board Charging (OBC) Platform User Manual (ONSEMI Semiconductor)

京公网安备 11010802033920号

京公网安备 11010802033920号