Li Mingyang, Bai Peng

(School of Engineering, Air Force Engineering University, Xi'an 710038, Shaanxi)

0 Introduction

In signal acquisition and processing, we are often only concerned with signals with narrow bandwidth and strong periodic characteristics. At this time, broadband noise becomes a harmful component that must be filtered out. The spectrum of the signal carries the most essential characteristics of the source, but the actual acquired signal is inevitably affected by broadband noise or broadband interference. How to quickly and efficiently eliminate these noises and interferences and enhance the target spectrum line is of great significance in the field of signal processing. ALE uses the periodicity of narrowband signals and the weak correlation of broadband noise to adaptively extract signals from noise under the condition that the signal characteristics are unknown. It is widely used in target recognition and feature extraction. FPGA occupies an important position in the field of digital signal processing due to its high design flexibility, high-speed data processing capabilities, and rich on-chip resources. Here, FPGA is used as the core part of digital signal processing. Pipeline structure and distributed algorithm are effective ways to fully utilize the high-speed processing capabilities of FPGA and realize complex digital signal processing algorithms. The core part of ALE constructs an FPGA pipeline structure that uses the LMS (Least Mean Square LMS) algorithm to achieve adaptive spectrum line enhancement and hardware implementation.

1 Principle of Adaptive Filtering

Adaptive filtering is relative to fixed filters. The filtering frequency of fixed filters is fixed, while the filtering frequency of adaptive filters automatically adapts to the input signal and changes, so its application range is wider. Adaptive filters are the best filters that meet certain criteria. This filter can automatically update its weight coefficients according to the changes of the input signal without any prior statistical knowledge about the signal and noise to meet the needs of optimal filtering. Adaptive filters can not only process stationary random signals but also non-stationary random signals. These characteristics make adaptive filters widely used in signal processing fields such as interference elimination, prediction, inversion, and identification.

The principle of adaptive filtering includes two aspects: one is the adaptive algorithm for adjusting the filter coefficients, and the other is the filter structure. The adaptive filtering algorithm is to set a certain criterion so that the difference between the filtered output signal and the reference signal is minimized under this criterion. The Wiener criterion is widely used in adaptive filtering, and its solution is the Wiener solution. The filter structure is a way to implement the adaptive algorithm. Seeking efficient filter structure has always been the focus of research on adaptive filtering. The FIR transverse structure is the most common filter structure. Designing a pipeline for the hardware of the lateral structure filter is an effective way to realize high-speed adaptive filtering in FPGA. Therefore, the pipeline is used in this design to realize the adaptive filter of ALE. The principle of the adaptive filter is shown in Figure 1. Among them, x(n) is the input signal, y(n) is the output signal, d(n) is the reference signal, and e(n) is the error signal.

The LMS algorithm is an easy-to-implement, robust and widely used algorithm. It uses the negative error energy gradient to update the weight coefficient of the filter. Its steady-state solution is still the Wiener solution. The algorithm recursive formula is as follows:

Among them: Xj is the input signal; Wj is the weight coefficient of the adaptive filter; dj is the reference signal; ej is the error; μ is a gain constant used to control the adaptive speed and stability.

2 ALE principle and its Matlab simulation

2.1 ALE principle

ALE belongs to the category of adaptive filtering, but in the design of adaptive filters for spectral line enhancement, there is no external reference signal available. At this time, the original input signal is connected to a delay line with a fixed delay as a reference signal, taking advantage of the fact that the narrowband signal has obvious periodicity while the broadband noise has poor periodicity. After a delay of a period of time, the correlation function of the narrowband signal will be significantly stronger than the broadband noise. As long as the selected delay △ is long enough, the correlation between the broadband noise of the reference signal and the broadband noise of the original input will be rapidly weakened, while the correlation of the narrowband periodic signal will not be affected. According to the adaptive filtering theory, ALE filtering will have a learning process, and the learning process is the process in which the error signal tends to decrease continuously. When the learning process enters a steady state, the filter output is the source narrowband periodic signal and a random error, and the error can reach a very small amplitude by selecting a suitable step size factor. The ALE schematic diagram is shown in Figure 2.

2.2 Matlab simulation of ALE

Matlab is an effective tool for digital signal processing and simulation. Using Matlab for simulation at the beginning of the design can effectively evaluate the final effect of the design and provide strong theoretical support for the entire design process. First, Matlab is used to simulate the ALE implemented by the LMS algorithm, and the effectiveness of the algorithm in the ALE system is proved from the time domain waveform and processing time of the simulation results. The sine wave mixed with Gaussian white noise is used as the input signal of the spectral line enhancement filter. Figure 3 is a partial simulation result of the algorithm using Matlab. It can be seen that the original periodic signal cannot be judged at all based on the input signal mixed with noise. After a learning process of 0 to 100 time length, the filter output signal has obvious periodicity, the broadband noise is effectively filtered out, and the narrowband signal is filtered out. This period of time only requires μs level processing time in the high-speed FPGA, which meets the real-time requirements.

3 System Structure

The ALE system generally includes: analog/digital conversion, FPGA core processing, off-chip RAM, power supply, etc. The front end uses TLC5510 to complete the acquisition of analog signals and transmits them to FPGA in the form of digital signals. The FPGA part is the core of the entire system, which realizes the timing control of the analog/digital converter, the internal data cache FIFO, the on-chip clock synthesis, the spectral line enhancement algorithm and the off-chip RAM control. The data after spectral line enhancement is stored in the off-chip RAM chip CY7C1021V. The power supply provides the 3.3 V and 5 V required by the entire system and the reference voltage of TLC5510. The system structure is shown in Figure 4.

TLC5510 is a high-speed analog/digital converter from TI, which can be used in video processing, high-speed data conversion and other fields. Its conversion rate reaches 20 Mb/s. The high-speed AD chip is used to match the high-speed processing capability of FPGA. EP2C8F256C6 is a CycloneⅡ series FPGA produced by Altera. It has 162 Kb of on-chip memory and 36 18×18 b on-chip multipliers, which can be used to implement complex digital signal algorithms. The on-chip memory is based on the popular M4K memory block and can support a wide range of configurations, including RAM, ROM, first-in first-out (FIFO) buffers, and single-port and dual-port modes. On-chip multipliers are ideal for low-cost digital signal processing (DSP) applications. These multipliers can be used to implement general DSP functions such as finite impulse response (FIR) filters, fast Fourier transforms, correlators, encoders/decoders, and numerically controlled oscillators (NCOs). EP2C8F256C6 provides advanced external memory interface support, allowing developers to integrate external single data rate (SDR), double data rate (DDR), DDR2 SDRAM devices and second generation 4x data rate (QDRⅡ) SRAM devices. The chip has a clock management module, which uses PLL to realize on-chip clock synthesis, so that the data processing rate is much higher than the signal acquisition rate to meet the real-time requirements. The sampling control of TLC5510 is first implemented inside the FPGA. The sampling signal must first be stored in the on-chip FIFO. After each ALE algorithm iteration is completed, the data in the FIFO is taken out and the processing data is updated. The data to be processed is processed by signal delay processing and LMS adaptive filtering algorithm to obtain a spectral enhanced signal. The on-chip clock synthesis module provides the clock signal for the system, and uses the on-chip PLL to multiply and divide the crystal oscillator clock to provide a 600 MHz clock inside the chip and a 10 MHz clock for the off-chip TLC5510 and RAM. In order to ensure data accuracy. The data processed by ALE is output as a 16-bit binary digital signal. The off-chip memory uses a 64K×16b static RAM chip CY7C1021V, and its read/write control timing is also implemented by FPGA.

3.1 Control of TLC5510

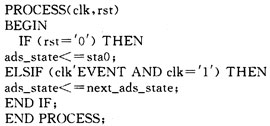

TLC5510 is an 8-bit high-speed analog-to-digital converter that samples in a pipeline mode. It starts and completes one sampling in each clock cycle. The sampling is performed on the falling edge of the clock, and the conversion result is output after 2.5 clock cycles. In the design, according to the sampling timing, a state machine is used to describe the sampling control process to achieve sampling control. The VHDL code for state alternation is as follows:

The VHDL code for sampling data output is as follows:

3.2 Sampling signal delay

In order to achieve delay, three buffers are opened in the FPGA chip, namely input, delay, and weight buffers. The sampled data is first stored in the on-chip data cache FIFO and enters the standby state. The delay buffer implements a delay of △ length, and the weight buffer stores weights. Among them, the addresses of the delay buffer and the input buffer are continuous. The length of the delay buffer is determined by the delay △, and the length of the input buffer and the weight buffer is determined by the dimension of the weight. The implementation of the buffer is to define the vectors of stored data in the program written in VHDL language. The data types of these data vectors are defined as follows:

Among them: ARRAY_N1BIF defines the data type of the filter parameter vector; ARRAY_N1BIYX defines the data type of the delayed signal vector; ARRAY_N1BIT defines the data type of the input signal vector; ARRAY_N2BIT defines the data type of the signal vector after spectral line enhancement; W1 is the width of the sampled data, which is 8 here; Delay is the delay length; L is the filter order.

3.3 LMS algorithm core module

This is the core part of the design and also the difficulty in the design. Using FPGA to implement complex digital signal processing is not as simple as in DSP. It is necessary to consider timing synchronization, data width and how to round. This design uses a 16-order adaptive filter to implement ALE. The initial weights of the filter are all 0. It is iteratively updated according to the algorithm of formula (3). A large number of multiplication operations are used in the algorithm implementation. Calling the multiplier macro function module lpm_mult embedded in the chip makes it faster and more efficient to implement these multiplication operations. The lpm_mult module inputs the sampled 8-bit data. Since the result of multiplying two 8-bit binary numbers in the multiplication operation is a 16-bit binary number, the design outputs the processing result as a 16-bit binary number. In order to improve the speed of adaptive filtering, the design adopts a pipeline filter structure. The pipeline structure can significantly improve the processing speed, but it consumes more hardware resources, especially hardware multipliers. If the length of the LMS FIR filter is L, 2L general multipliers are required. In the design, L=16, and there are 36 on-chip multipliers in the chip that can meet the processing requirements. The compilation results show that the consumption of other resources used in the LMS core algorithm in the chip is less than or equal to 6% of the total consumption, and the remaining resources can be used for timing control such as sampling and output in the chip. The block diagram of the pipeline structure of the LMS algorithm hardware implementation is shown in Figure 5.

The VHDL code for calling the multiplier in the pipeline structure is as follows:

4 Simulation results analysis

The partial simulation results of the VHDL program on the QuartusⅡ software are shown in Figure 6, and the simulation data in the figure is expressed in decimal. Because the simulation results are not convenient for drawing graphics similar to those in Matlab, the data of the simulation results are compared with the Matlab simulation results. Through line comparison, it is found that the processing results are generally consistent with Matlab, but the amplitude is somewhat attenuated overall. This is because the low bits of the processing results are truncated in the FPGA, while the Matlab simulation environment uses floating point form and has a long data bit number. The processing accuracy is much higher than that of FPGA, and there is a large truncation error in the FPGA design. The simulation results show that it is feasible to implement ALE based on FPGA.

5 Conclusion

The system uses FPGA chips plus a small amount of peripheral circuits to complete the adaptive spectral line enhancement of the signal. By calling the FPGA on-chip multiplier and on-chip memory, the adaptive spectral line enhancement of the LMS algorithm is completed, and the simulation results are consistent with the theory. Most modern digital signal processing algorithms require a large number of multiplication operations. Calling the FPGA on-chip multiplier is a fast, efficient and economical means to implement these algorithms, which makes it possible to implement complex signal processing algorithms on FPGA. The pipeline structure is an effective means to sacrifice resources to increase speed in hardware design. Effective use of pipelines can significantly improve resource utilization and processing speed. This design can achieve high-speed and accurate spectral line enhancement, and has certain practical significance in the field where broadband noise needs to be filtered out to extract a single spectral line.

Previous article:Wireless Subsystem Using FPGA Coprocessing

Next article:Design of photoelectric anti-interference circuit based on FPGA

- Popular Resources

- Popular amplifiers

- Huawei's Strategic Department Director Gai Gang: The cumulative installed base of open source Euler operating system exceeds 10 million sets

- Analysis of the application of several common contact parts in high-voltage connectors of new energy vehicles

- Wiring harness durability test and contact voltage drop test method

- Sn-doped CuO nanostructure-based ethanol gas sensor for real-time drunk driving detection in vehicles

- Design considerations for automotive battery wiring harness

- Do you know all the various motors commonly used in automotive electronics?

- What are the functions of the Internet of Vehicles? What are the uses and benefits of the Internet of Vehicles?

- Power Inverter - A critical safety system for electric vehicles

- Analysis of the information security mechanism of AUTOSAR, the automotive embedded software framework

Professor at Beihang University, dedicated to promoting microcontrollers and embedded systems for over 20 years.

Professor at Beihang University, dedicated to promoting microcontrollers and embedded systems for over 20 years.

- Innolux's intelligent steer-by-wire solution makes cars smarter and safer

- 8051 MCU - Parity Check

- How to efficiently balance the sensitivity of tactile sensing interfaces

- What should I do if the servo motor shakes? What causes the servo motor to shake quickly?

- 【Brushless Motor】Analysis of three-phase BLDC motor and sharing of two popular development boards

- Midea Industrial Technology's subsidiaries Clou Electronics and Hekang New Energy jointly appeared at the Munich Battery Energy Storage Exhibition and Solar Energy Exhibition

- Guoxin Sichen | Application of ferroelectric memory PB85RS2MC in power battery management, with a capacity of 2M

- Analysis of common faults of frequency converter

- In a head-on competition with Qualcomm, what kind of cockpit products has Intel come up with?

- Dalian Rongke's all-vanadium liquid flow battery energy storage equipment industrialization project has entered the sprint stage before production

- Allegro MicroSystems Introduces Advanced Magnetic and Inductive Position Sensing Solutions at Electronica 2024

- Car key in the left hand, liveness detection radar in the right hand, UWB is imperative for cars!

- After a decade of rapid development, domestic CIS has entered the market

- Aegis Dagger Battery + Thor EM-i Super Hybrid, Geely New Energy has thrown out two "king bombs"

- A brief discussion on functional safety - fault, error, and failure

- In the smart car 2.0 cycle, these core industry chains are facing major opportunities!

- The United States and Japan are developing new batteries. CATL faces challenges? How should China's new energy battery industry respond?

- Murata launches high-precision 6-axis inertial sensor for automobiles

- Ford patents pre-charge alarm to help save costs and respond to emergencies

- New real-time microcontroller system from Texas Instruments enables smarter processing in automotive and industrial applications

- How long will the battle between community owners and communication base stations last?

- Please tell me the winding method and other parameters of the EE8 transformer that can increase 0.7V to 7V

- Conversion between CC2640R2F projects

- Pengfeng Technology RVBoards-Nezha (RISC-V SBC) Allwinner Development Board Introduction Part 3

- [Repost] A few simple steps to help you understand the MCU timing diagram

- Cadence Certus Closure Solution is a new generation chip-level convergence solution. Welcome to learn more!

- What is the progress of domestic NPU chips?

- How is JTAG used for chip testing?

- Talk about downloading the DSP28335 register manual

- 4W PLC Power Supply Reference Design with Wide Input Voltage Range

LMV824MX/NOPB

LMV824MX/NOPB

京公网安备 11010802033920号

京公网安备 11010802033920号