1 Introduction

The signal source is an important part of the radar system. Radar systems often require that the signal source is stable, reliable, easy to implement, has pre-distortion function, and the signal generation and signal parameter changes are simple and flexible. This article uses DSP and CPLD to design the control part of the signal source. On the one hand, it can take advantage of the flexibility of DSP software control, and on the other hand, it can take advantage of the high speed, high integration and programmability of CPLD hardware. This method can make full use of software support to generate and load arbitrary waveform data, and can easily control signal parameters and modify waveform data at will, while ensuring high-speed, flexible and controllable signal generation.

2 System structure

The waveform storage direct reading method is adopted, which is a method of directly generating analog signals by performing digital-to-analog conversion on the stored waveform sampling data. Figure 1 shows the system structure of the signal source. This signal source can work in both online and offline modes. When working online, the waveform data is loaded from the microcomputer, controlled by the DSP, and written into the SRAM through the data channel in the CPLD. After reading back and verifying, it is sent from the SRAM to the digital/analog conversion device at high speed to generate the radar signal. When working offline, the waveform data can be loaded from the EEPROM when the system is powered on. A set of waveform data can be stored in the EEPROM, or multiple sets of data can be stored to facilitate application.

3 Hardware implementation

3.1 Interface design between TMS320F206 and EEPROM

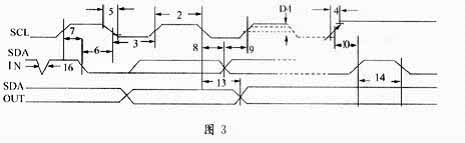

In the actual system, the DSP uses TI's TMS320F206 chip, and the EEPROM uses Microchip's 24LC256 CMOS serial EEPROM (Figure 2). TMS320F206 is a fixed-point, static CMOS digital signal processor. It adopts the advanced Harvard structure, with on-chip peripherals, on-chip memory and dedicated operation instruction set. These features make this device flexible and convenient to use. The operating voltage of 24LC256 is 2.5V ~ 5.5V, the capacity is 32K×8bit, it is a two-wire serial interface bus, and the standard is compatible with I2CTM. SCL is the clock input pin of 24LC256, and SDA is its serial address/data input/data output pin. 24LC256 provides an operation mode for reading sequential address contents. Its internal address pointer is incremented by 1 after each read operation is completed. This address pointer allows the contents of the entire memory to be read continuously and sequentially during a read operation. The timing is shown in Figure 3.

In the design, the general I/O port IO2 of TMS320F206 is simulated as the clock of SCL, and IO3 is responsible for writing data to and reading from 24LC256 (the interface between TMS320F206 and 24LC256 is shown in Figure 1). When working offline, the process is as shown in Figure 4.

3.2 CPLD design

The programmable logic device uses CPLD of XILINX Company, model number is XC95288XL-6TQ144C. The device is a 144-pin TQFP package with 288 macro cells inside and a maximum operating clock of 151MHz. The internal logic of XC95288XL is divided into three parts: communication between TMS320F206 and the microcomputer interface, high-speed address counting, and generation of SRAM chip select read and write signals.

3.2.1 Communication between TMS320F206 and microcomputer interface through CPLD

The communication between TMS320F206 and the microcomputer interface adopts the parallel interface protocol (EPP), which mainly completes loading data from the microcomputer to SRAM and reading data back from SRAM to the microcomputer. The whole process adopts query mode for the parallel interface and interrupt mode for TMS320F206. . TMS320F206 uses  pins to receive interrupts sent by CPLD. By setting the TMS320F206 on-chip registers IRM and ICR, TMS320F206 responds to interrupts without responding. The timing is shown in Figures 5 and 6.

pins to receive interrupts sent by CPLD. By setting the TMS320F206 on-chip registers IRM and ICR, TMS320F206 responds to interrupts without responding. The timing is shown in Figures 5 and 6.

In the offline working state, when loading data from the parallel port, the microcomputer sends the data to the parallel port and sends out a  low pulse.

low pulse.  After the CPLD receives the STB arrival, it sets BUSY=1 and sends an interrupt signal. After TMS320F206 receives the interrupt, it controls the CPLD to latch the data. , and write the data to SRAM, set BUSY=0; when reading back the data from the parallel port, the microcomputer sets the parallel port to the input state, and then sends out the AUTOFEEDXT low pulse. After receiving the AUTOFEEDXT pulse, CPLD

After the CPLD receives the STB arrival, it sets BUSY=1 and sends an interrupt signal. After TMS320F206 receives the interrupt, it controls the CPLD to latch the data. , and write the data to SRAM, set BUSY=0; when reading back the data from the parallel port, the microcomputer sets the parallel port to the input state, and then sends out the AUTOFEEDXT low pulse. After receiving the AUTOFEEDXT pulse, CPLD  sets

sets  = 1 and sends an interrupt signal to TMS320F206, which is controlled by TMS320F206. CPLD reads data from SRAM and sends it to the parallel port, setting

= 1 and sends an interrupt signal to TMS320F206, which is controlled by TMS320F206. CPLD reads data from SRAM and sends it to the parallel port, setting  = 0.

= 0.

3.2.2 Design of high-speed address counter

The SRAM in the signal source works at a high-speed clock of 100MHz when generating radar waveforms, which requires the designed address counter to also work at a 100MHz clock. In synchronous counters, carry-lookahead (prescalar) technology is used to improve its performance, that is, the leading output of the front-end, high-speed counter is used as the counting enable of the subsequent low-speed counter. During implementation, we use the efficient macrocell CLBMAP provided in XILINX's EDA software to optimize wiring, thereby minimizing the internal delay of the counter. Figure 7 shows the simulation results of counter outputs Q0~Q6. Experiments show that the above measures are very effective in improving the speed of synchronous counters.

3.2.3 Generation of SRAM chip select read and write signals

The waveform storage unit is composed of two pieces of high-speed, low-power static dual-port SRAM with a capacity of 128K×18bit. The device supports multiple methods such as single read and write, pipeline read and write, triggered read and write, etc. It can read and write the high and low bytes of the same address unit separately or simultaneously. Therefore, the chip select read and write signal timing is very complex.

In this design, the SRAM chip select read and write signals are directly sent to the CPLD from the data line by the TMS320F206, without having to be generated by the complex decoding logic circuit inside the CPLD. This shows that the DSP+CPLD design is simple. Since the high-speed readout waveform data is sent to the D/A under a high-speed clock (100MHz), the chip select read signal is always valid during high-speed readout. When writing, since there will be no operation on the SRAM for a long time, in order to avoid writing erroneous data due to burrs on the clock signal line, when writing to the SRAM, the chip select write signal is only on the single clock of writing. Period is valid.

4 TMS320F206 software design

The signal source has two working modes: online and offline. There is a mode selection switch on the PCB board. TMS320F206 detects the working mode through the I/O port IO1. The TMS320F206 control program first initializes the TMS320F206 and sets each on-chip register. Then decide whether to load from EEPROM or from the microcomputer based on the value of IO1. The program flow is omitted.

5 Experimental results

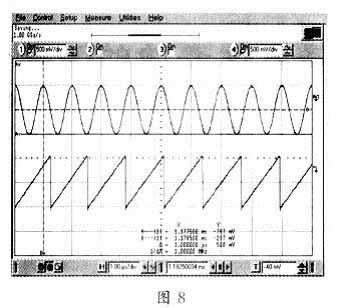

Use an oscilloscope to test the results generated by the signal source. The results are shown in Figures 8 and 9. Figure 8 shows the generated sine wave and sawtooth waveforms. Figure 9 shows the baseband waveform of the chirp signal generated in offline mode. The width is 25μs and the baseband bandwidth is 37.5MHz. After 4 times the frequency, the bandwidth can reach 300MHz.

Experimental results show that using DSP + CPLD to design the control part of the signal source has great advantages. The system is flexible and adjustable, has stable performance, complex control can be easily implemented with software, and the high-speed characteristics of the system are also satisfied.

references

1, edited by Li Bocheng et al. IBM PC microcomputer application system design. Xi'an: Xi'an University of Electronic Science and Technology Press, 1996

Previous article:Design and implementation of low-power encrypted voice hardware platform based on TMS320VC5510

Next article:Multimedia codec chip selection strategy

- Popular Resources

- Popular amplifiers

-

Dual Radar: A Dual 4D Radar Multimodal Dataset for Autonomous Driving

Dual Radar: A Dual 4D Radar Multimodal Dataset for Autonomous Driving -

A review of learning-based camera and lidar simulation methods for autonomous driving systems

A review of learning-based camera and lidar simulation methods for autonomous driving systems -

Computer Vision Applications in Autonomous Vehicles: Methods, Challenges, and Future Directions

Computer Vision Applications in Autonomous Vehicles: Methods, Challenges, and Future Directions -

Motor Control and Learning (Markus Latash, Francis Lestienne)

Motor Control and Learning (Markus Latash, Francis Lestienne)

- Huawei's Strategic Department Director Gai Gang: The cumulative installed base of open source Euler operating system exceeds 10 million sets

- Analysis of the application of several common contact parts in high-voltage connectors of new energy vehicles

- Wiring harness durability test and contact voltage drop test method

- Sn-doped CuO nanostructure-based ethanol gas sensor for real-time drunk driving detection in vehicles

- Design considerations for automotive battery wiring harness

- Do you know all the various motors commonly used in automotive electronics?

- What are the functions of the Internet of Vehicles? What are the uses and benefits of the Internet of Vehicles?

- Power Inverter - A critical safety system for electric vehicles

- Analysis of the information security mechanism of AUTOSAR, the automotive embedded software framework

Professor at Beihang University, dedicated to promoting microcontrollers and embedded systems for over 20 years.

Professor at Beihang University, dedicated to promoting microcontrollers and embedded systems for over 20 years.

- Innolux's intelligent steer-by-wire solution makes cars smarter and safer

- 8051 MCU - Parity Check

- How to efficiently balance the sensitivity of tactile sensing interfaces

- What should I do if the servo motor shakes? What causes the servo motor to shake quickly?

- 【Brushless Motor】Analysis of three-phase BLDC motor and sharing of two popular development boards

- Midea Industrial Technology's subsidiaries Clou Electronics and Hekang New Energy jointly appeared at the Munich Battery Energy Storage Exhibition and Solar Energy Exhibition

- Guoxin Sichen | Application of ferroelectric memory PB85RS2MC in power battery management, with a capacity of 2M

- Analysis of common faults of frequency converter

- In a head-on competition with Qualcomm, what kind of cockpit products has Intel come up with?

- Dalian Rongke's all-vanadium liquid flow battery energy storage equipment industrialization project has entered the sprint stage before production

- Allegro MicroSystems Introduces Advanced Magnetic and Inductive Position Sensing Solutions at Electronica 2024

- Car key in the left hand, liveness detection radar in the right hand, UWB is imperative for cars!

- After a decade of rapid development, domestic CIS has entered the market

- Aegis Dagger Battery + Thor EM-i Super Hybrid, Geely New Energy has thrown out two "king bombs"

- A brief discussion on functional safety - fault, error, and failure

- In the smart car 2.0 cycle, these core industry chains are facing major opportunities!

- The United States and Japan are developing new batteries. CATL faces challenges? How should China's new energy battery industry respond?

- Murata launches high-precision 6-axis inertial sensor for automobiles

- Ford patents pre-charge alarm to help save costs and respond to emergencies

- New real-time microcontroller system from Texas Instruments enables smarter processing in automotive and industrial applications

- [DWIN Serial Port Screen] Nucleic Acid Sampling Registration System 2: Prepare Background Image

- The zigbee terminal sets the PAN ID by pressing a button to join the set ID network

- GD32E231 DIY Part 3: LED Smooth Dimming Principle

- Far away, yet close at hand

- The power cord is too long and the power-on voltage is too high. Should I use a TVS tube?

- What is the essence of GND in the circuit?

- EEWORLD University - i.MX Linux Development Practical Guide

- Encoder Problems

- Introduction to IC Packaging and Testing Process

- TI C6000 Optimization Advanced: Loops are the most important!

Dual Radar: A Dual 4D Radar Multimodal Dataset for Autonomous Driving

Dual Radar: A Dual 4D Radar Multimodal Dataset for Autonomous Driving

京公网安备 11010802033920号

京公网安备 11010802033920号