1 MicroBlaze Architecture

MicroBlaze uses a powerful 32-bit pipeline structure, including 32 32-bit general registers and an optional 32-bit shifter, with a clock frequency of up to 150 MHz; it runs at a speed of up to 120 DMIPS on a Virtex-4 FPGA and only occupies 950 logic cells in a Virtex-II Pro FPGA. The block diagram of the MicroBlaze soft core is shown in Figure 1. It has the following basic features:

①32 32-bit general registers and 2 special registers (program counter and status flag register).

②32-bit instruction system, supporting 3 operands and 2 addressing modes.

③ Separate 32-bit instruction and data buses, compliant with IBM's OPB bus specification (a low-speed bus connected to peripherals).

④ Directly access the on-chip block memory (BRAM) through the local memory bus (LMB, local high-speed bus).

⑤ It has high-speed instruction and data cache and three-level pipeline structure (addressing, decoding, and execution).

⑥Has hardware debugging module (MDM).

⑦With 8 input and 8 output fast link interfaces (FSL).

The interface signals in the figure are described as follows:

①DOPB, the peripheral device data interface bus inside the device, is used for data exchange between the processor and the devices on the chip.

②DLMB, local block memory bus for data exchange. This bus provides a dedicated high-speed data exchange channel between the processor core and the block memory (BRAM).

③IOPB, used to implement the bus interface of the external program memory. When the program is large, a large-capacity external memory is required. This bus provides a channel for reading instructions.

④ILMB, local memory bus for instruction fetching. This bus is connected to the block memory (BRAM) inside the device to achieve high-speed instruction fetching.

⑤MFSLO~7, master device data interface, providing point-to-point communication channel.

⑥SFSLO~7, slave device data interface, provides point-to-point communication channel.

2 MicroBlaze Embedded Development Tool EDK

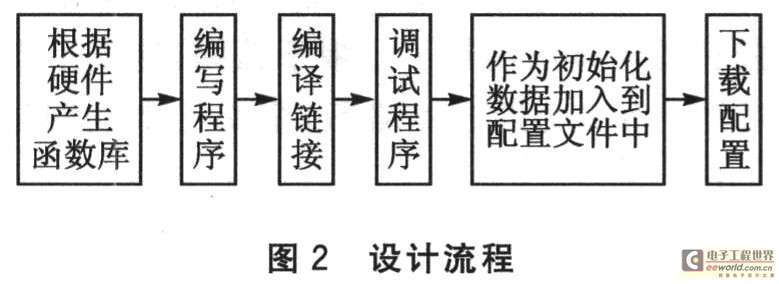

Xilinx provides a complete embedded development tool EDK (Em-bedded Development Kit). EDK is a SOPC (System On Programmable Chip) system development kit launched by Xilinx in 2003. The kit integrates a wealth of development tools and a large number of IP core resources, including hardware platform generator (PlatGen), hardware simulation model generator (SimGen), hardware debugging tool (XMD), software library generator (LibGen), application software compilation tool (GNU Compilers), software debugging tool (GNU Debuggers), etc.; IP core resources include LMB and OPB bus interfaces, external memory controller (EMC), SDRAM controller, UART interface, interrupt controller, timer, etc. All these tools and resources are managed by an integrated development environment called Platform Studio XPS (Xilinx Platform Studio) in EDK. XPS provides a friendly graphical user interface (GUI) and is very easy to use. The design process is shown in Figure 2.

[page]

[page]

3 LCD display module

The MPG240128 LCD module is a graphic dot matrix LCD that can display not only numbers, characters, but also Chinese characters and arbitrary graphics. The control chip of this module is T6963C, and the connection with the outside is only 8-bit data lines, 6 control lines and power supply. The LCD module pin description is listed in Table 1. MCtJ can realize the display control of the module by reading and writing these data lines and control lines according to the corresponding timing.

4 Interface between Microblaze and LCD module

Since the LCD module used in this article already has a display control chip T6963C, the peripheral circuit of the LCD module is relatively simple, and only the interface circuit with MicroBlaze needs to be considered. This design uses GPIO

Perform system hardware design in the XPS integrated development environment of the EDK development kit. In its interface environment, add the required IP cores, connect the system and set various parameters. Use the platform generator to generate the netlist file (.NGC) of the embedded system submodule based on the hardware description file (.MHS file), and then call Xilinx's synthesis tool XST for synthesis, thus forming the hardware model of the entire application system. [page]

This design uses GPIO to control the LCD module. EDK provides a series of API functions, which can be used to easily operate GPIO. The following are two functions:

Among them, InstancePtr is a pointer pointing to the base address of the GPIO to be controlled; Channel is the channel value, which can be 0 or 1. These two functions only affect the bits whose corresponding bits in Mask are 1. For example, XGpio_DiscreteSet(&lcd240128, 1, 0x00000001) sets LCl3240128_pin

[page]

[page]

The graphics and characters displayed by LCD are composed of dot matrix, so displaying a pixel on LCD is the basis of displaying graphics and characters. The single pixel display function is introduced as follows:

With the single pixel display function, it is very convenient to write character display function and graphic display function. Due to space limitations, we will not introduce them here.

Conclusion

This design has been verified on Xilinx Spatan3 Starter Board and achieved good results. Through the implementation of this design, it can be seen that MicroBlaze is a powerful and flexible embedded soft processor, especially its powerful user-defined logic function, which greatly facilitates system design. It can be foreseen that the SOPC development method based on embedded soft processor will have broad application prospects.

Previous article:Design and implementation of DDS chip based on model

Next article:Design of ARINC429 bus interface module based on USB

Recommended ReadingLatest update time:2024-11-16 22:56

- Popular Resources

- Popular amplifiers

-

MCU C language programming and Proteus simulation technology (Xu Aijun)

MCU C language programming and Proteus simulation technology (Xu Aijun) -

100 Examples of Microcontroller C Language Applications (with CD-ROM, 3rd Edition) (Wang Huiliang, Wang Dongfeng, Dong Guanqiang)

100 Examples of Microcontroller C Language Applications (with CD-ROM, 3rd Edition) (Wang Huiliang, Wang Dongfeng, Dong Guanqiang) -

Power Integrated Circuit Technology Theory and Design (Wen Jincai, Chen Keming, Hong Hui, Han Yan)

Power Integrated Circuit Technology Theory and Design (Wen Jincai, Chen Keming, Hong Hui, Han Yan) -

Installation and Testing of Analog Electronic Products (Edited by Chen Jingzhong and Tang Mingjun)

Installation and Testing of Analog Electronic Products (Edited by Chen Jingzhong and Tang Mingjun)

- Huawei's Strategic Department Director Gai Gang: The cumulative installed base of open source Euler operating system exceeds 10 million sets

- Analysis of the application of several common contact parts in high-voltage connectors of new energy vehicles

- Wiring harness durability test and contact voltage drop test method

- Sn-doped CuO nanostructure-based ethanol gas sensor for real-time drunk driving detection in vehicles

- Design considerations for automotive battery wiring harness

- Do you know all the various motors commonly used in automotive electronics?

- What are the functions of the Internet of Vehicles? What are the uses and benefits of the Internet of Vehicles?

- Power Inverter - A critical safety system for electric vehicles

- Analysis of the information security mechanism of AUTOSAR, the automotive embedded software framework

Professor at Beihang University, dedicated to promoting microcontrollers and embedded systems for over 20 years.

Professor at Beihang University, dedicated to promoting microcontrollers and embedded systems for over 20 years.

- Innolux's intelligent steer-by-wire solution makes cars smarter and safer

- 8051 MCU - Parity Check

- How to efficiently balance the sensitivity of tactile sensing interfaces

- What should I do if the servo motor shakes? What causes the servo motor to shake quickly?

- 【Brushless Motor】Analysis of three-phase BLDC motor and sharing of two popular development boards

- Midea Industrial Technology's subsidiaries Clou Electronics and Hekang New Energy jointly appeared at the Munich Battery Energy Storage Exhibition and Solar Energy Exhibition

- Guoxin Sichen | Application of ferroelectric memory PB85RS2MC in power battery management, with a capacity of 2M

- Analysis of common faults of frequency converter

- In a head-on competition with Qualcomm, what kind of cockpit products has Intel come up with?

- Dalian Rongke's all-vanadium liquid flow battery energy storage equipment industrialization project has entered the sprint stage before production

- Allegro MicroSystems Introduces Advanced Magnetic and Inductive Position Sensing Solutions at Electronica 2024

- Car key in the left hand, liveness detection radar in the right hand, UWB is imperative for cars!

- After a decade of rapid development, domestic CIS has entered the market

- Aegis Dagger Battery + Thor EM-i Super Hybrid, Geely New Energy has thrown out two "king bombs"

- A brief discussion on functional safety - fault, error, and failure

- In the smart car 2.0 cycle, these core industry chains are facing major opportunities!

- The United States and Japan are developing new batteries. CATL faces challenges? How should China's new energy battery industry respond?

- Murata launches high-precision 6-axis inertial sensor for automobiles

- Ford patents pre-charge alarm to help save costs and respond to emergencies

- New real-time microcontroller system from Texas Instruments enables smarter processing in automotive and industrial applications

- Supplement: Design of the lower computer for the computer room monitoring project

- Emulating an IBM PC on ESP32

- Delayed power off problem

- Understanding C language pointers

- Intelligent POS system block diagram analysis and its seven key functional module solutions

- Animation demonstrates the working principle of capacitors and the principle of capacitive sensors

- Feiling Technical Post-Only 4 steps to make Qt remote debugging easier

- AT commands in C language

- Design circuit and program based on MSP430 simple oscilloscope

- Circuit Playground Bluefruit NeoPixel Animated Remote Control

MCU C language programming and Proteus simulation technology (Xu Aijun)

MCU C language programming and Proteus simulation technology (Xu Aijun)

京公网安备 11010802033920号

京公网安备 11010802033920号