System-level power conservation and power budget optimization are key to many applications. For example, data center operators strive to control energy consumption, portable device designers seek to reduce current consumption to achieve longer battery life, and communication systems need to reduce operating temperature and improve stability. The current focus of the main specifications of power supply design is to: 1) maximize efficiency over the entire load current range; and 2) adaptively scale the output voltage according to the load needs.

Using voltage identification (VID) to adjust the output voltage is one way to meet these requirements. Of course, VID programmability has been widely used in DC/DC core voltage regulators for microprocessor applications based on the well-known adaptive voltage scaling (AVS) specification provided by Intel and AMD. However, these VID controllers are built on a multi-phase buck topology with features specifically tailored around very high current requirements.

DSPs, FPGAs, and ASICs now have similar capabilities to minimize power consumption based on device activity, power and clock domain configuration, operating mode, and operating temperature. While digital pulse width modulator (PWM) controller solutions with VID support [1] are available to meet this need, there is also a need to digitally adjust the output voltage of the ubiquitous analog controlled point-of-load (POL) regulators. In the process of adjustment, analog power supply implementations (perhaps already designed or tested on the test bench) can be easily adjusted to meet system-level power budget and cost targets that are not achievable by other solutions.

Digital output voltage regulation

Given the benefits of the above design goals, TI now offers a VID programmer [2] as an application specific standard product (ATSP). Figure 1 shows the LM10011 , which is used to complement the analog POL DC/DC solution . It includes a high-precision digitally programmable current digital-to-analog converter (IDAC) that supports mode-selectable 4-bit and 6-bit VID interfaces. The precise DC current at the IDAC_OUT pin is proportional to the 4-bit or 6-bit digital input word and can be input to the feedback (FB) node of the output regulation loop. As the input word accumulates, the IDAC_OUT current can be reduced, thereby adjusting the output voltage set point based on the regulator feedback resistor. The FB node is typically maintained at a constant voltage by the error amplifier of the analog control loop.

Figure 1 : A conventional POL regulator is paired with a current DAC to form a 6 -bit digital VID interface

Of utmost importance in this implementation is the compatibility of the VID solution with the analog POL regulator design. The POL can effectively be deployed as a slave device to the DSP. The IDAC solution is designed to help DSPs and other digital loads achieve their full power saving capabilities and reduce power consumption, such as in communications infrastructure applications. In fact, the VID solution is designed to work with any POL regulator to regulate the core voltage (VCORE) of VID-enabled processors such as KeyStone™ multicore DSPs [3] .

DSP core power supply

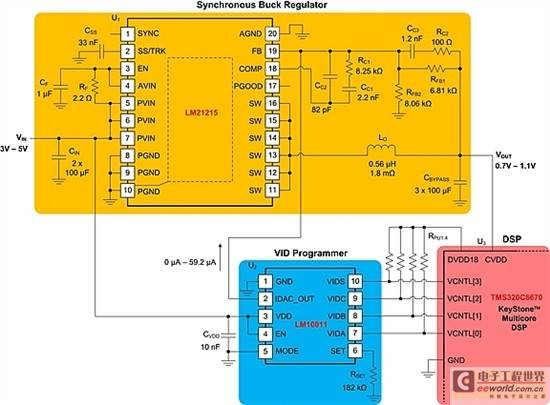

Figure 2 is a schematic diagram of a multicore DSP with core voltage CVDD supplied by a synchronous buck POL regulator. The power stage includes a 15A voltage mode regulator, a 560nH inductor, and ceramic input and output filter capacitors [2] . The 6-bit VID command from the DSP helps adjust the output voltage V OUT according to the changing performance requirements of the DSP .

Figure 2 : Powering a multicore DSP/SoC platform with core voltage rails using a synchronous buck regulator with VID -controlled adjustability

According to the system implementation shown in Figure 2 , the specific control scheme uses a 4-wire (VCNTL) interface for 6-bit VID, which allows for higher resolution or fine granularity in VID operation. The IDAC_OUT current has a maximum full-scale range of 59.2µA (VID[5:0] = 000000b = code 0). In 6-bit mode, this provides 64 settings with a resolution of 940nA and an error accuracy of better than 1%.

The output voltage is determined by the DSP to be between 0.7V and 1.103V. This equates to a V OUT regulation resolution of 403mV/63, or 6.4mV. Slew limiting prevents abrupt changes in the output. The VID deglitch filter provides noise immunity (effectively adding a small delay between the transition of the VID line and the subsequent change in the IDAC_OUT current). During startup before a VID command is received, the IDAC_OUT current can assume one of 16 discrete levels, depending on the R SET value. This allows the DSP's core voltage to power up at a variety of levels, allowing for greater system flexibility and reliability.

However, it is important to note that a specific DSP may not support all voltages or ranges. For example, for the KeyStone I DSP, the expected operating range is between codes 31 and 50 (0.905V to 1.020V) [4] . The supply voltage for the LM10011 in Figure 2 is derived from the input bus. Another option is to use a nominal 3.3V or 5V bias rail provided by the PWM controller or elsewhere in the system (if available). No level translator or glue logic is required between the DSP and the current DAC.

Figure 3 is a more detailed description of the VID interface and related timing details. VCNTL[2:0] carries two bits of data for each VID code. VID at a low or high level can be used to select the lower and upper bits respectively, while VIDS at a high level can also latch the VID command to initiate a current change in IDAC_OUT with a 40µs time constant. Therefore, each voltage adjustment requires two head-to-head accesses from the DSP to the controller. The first access writes the lower three bits and the second access writes the upper three bits.

Figure 3 : 6 -bit Mode VID Communication Timing Diagram

Using the VID GUI software [5], the output voltage waveform at startup and the transient response following the high and low VID transitions can be recorded, as shown in Figure 4. The input voltage is 5.3 V. As expected, the output voltage transition occurs on the rising edge of the VIDS signal.

Figure 4 : a) Monotonic startup to preset value; b) Output voltage following VID transition 31 dec-50 dec-31 dec .

Summarize

In this article, we briefly explore the challenges associated with DSP power budget optimization and introduce a simple method to use low-cost analog POL controllers through the VID interface. The article includes the main design considerations and circuit implementation. This method is low-complexity and easy to use, suitable for power and BOM optimized applications, which can fully meet the ever-present time-to-market and cost constraints. Simplicity, accuracy and low cost are important design criteria.

References

- Learn more about the LM92x digital power controllers ;

- LM10011 VID programmer ;

- Watch this video for an in-depth look at the first VID programmer;

- Learn more about KeyStone multi-core DSP SoCs supporting SmartReflex ;

- Download the Hardware Design Guide for KeyStone I devices ;

- Download the LM10011 GUI Design Tool software .

Previous article:Optimizing DSP power budget by adjusting voltage regulator

Next article:Design of multi-channel high-precision data acquisition circuit based on TS101 DSP link port

- Popular Resources

- Popular amplifiers

- Detailed explanation of intelligent car body perception system

- How to solve the problem that the servo drive is not enabled

- Why does the servo drive not power on?

- What point should I connect to when the servo is turned on?

- How to turn on the internal enable of Panasonic servo drive?

- What is the rigidity setting of Panasonic servo drive?

- How to change the inertia ratio of Panasonic servo drive

- What is the inertia ratio of the servo motor?

- Is it better for the motor to have a large or small moment of inertia?

Professor at Beihang University, dedicated to promoting microcontrollers and embedded systems for over 20 years.

Professor at Beihang University, dedicated to promoting microcontrollers and embedded systems for over 20 years.

- LED chemical incompatibility test to see which chemicals LEDs can be used with

- Application of ARM9 hardware coprocessor on WinCE embedded motherboard

- What are the key points for selecting rotor flowmeter?

- LM317 high power charger circuit

- A brief analysis of Embest's application and development of embedded medical devices

- Single-phase RC protection circuit

- stm32 PVD programmable voltage monitor

- Introduction and measurement of edge trigger and level trigger of 51 single chip microcomputer

- Improved design of Linux system software shell protection technology

- What to do if the ABB robot protection device stops

- Detailed explanation of intelligent car body perception system

- How to solve the problem that the servo drive is not enabled

- Why does the servo drive not power on?

- What point should I connect to when the servo is turned on?

- How to turn on the internal enable of Panasonic servo drive?

- What is the rigidity setting of Panasonic servo drive?

- How to change the inertia ratio of Panasonic servo drive

- What is the inertia ratio of the servo motor?

- Is it better for the motor to have a large or small moment of inertia?

- What is the difference between low inertia and high inertia of servo motors?

- 【GD32E503 Review】+ Littlefs Porting

- Solution to TL570x-EVM-A2 development board device node operation not permitted

- National Technology N32 MCU RF Resource Library (official, practical information)

- Raspberry Pi Pico Windows Development Environment - Compile under Visual Studio Code...

- Power circuit problem

- View Circuit-ADC and System (1)

- Teach you to understand the role of resistors in circuits

- EEWORLD University Hall----High-efficiency power architecture for smart door locks, battery-free light switches and wireless sensors

- 【E840-DTU】TCP connection

- Tank-1 test stand description (for burning and testing ESP8266 series)

5962-9456601MPA

5962-9456601MPA

京公网安备 11010802033920号

京公网安备 11010802033920号