This article is a study of the ARM processor architecture, targeting the S3C2440 model. It refers to the content of the PROGRAMMER'S MODEL section in Samsung's official technical document S3C2440.pdf.

ARM and THUMB instruction modes

S3C2440 uses armv4t instruction set, and supports both arm instruction set and thumb instruction set. Arm instruction is 32-bit, while thumb instruction is 16-bit. The reason for thumb instruction is to reduce the storage space of code.

Switching between two instruction sets

Manual switching

is because no matter whether it is the arm instruction set or the thumb instruction set, the lowest bit of the code address is redundant, because thumb is 16-bit aligned and arm is 32-bit aligned. So the last bit can be used as a reference for switching. When executing the BX instruction, if the last bit of the address is set, the following instructions are interpreted using the thumb instruction set. When jumping, the last bit is cleared and the arm instruction set is used.Automatic switching

can only use the arm instruction set in privileged mode, so when executing thumb instructions in user mode, if you jump to privileged mode, it will automatically switch to the arm instruction mode. When switching back to user mode from privileged mode, if the thumb instruction set was used before entering, it will automatically switch back to the thumb instruction set.

Data storage format

S3C2440 supports both big-endian and small-endian data storage formats. By default, the little-endian format is used for storage.

Big-endian storage

stores high bytes in low addresses and low bytes in high addresses.Little endian storage

high bytes are stored in high addresses and low bytes are stored in low addresses.

Operation Mode

ARM920T supports seven operation modes:

User Mode

Fast interrupt mode

Interrupt Mode

Manager Mode

Abort Mode

System Mode

Undefined mode

Mode switching can be done by software or automatically, such as when an interrupt occurs. Except for user mode, all other modes are privileged modes, and some resources can only be used in privileged mode.

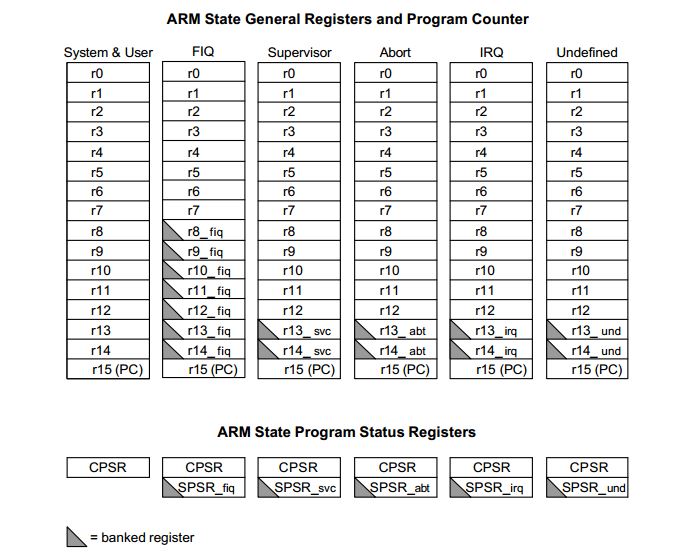

register

The ARM920T has a total of 37 registers, and not all registers are visible at the same time.

Registers in ARM mode

Registers in thumb mode

In thumb mode, not all registers are used, and registers R8-R12 are not used.

Although the R8-R12 registers cannot be used in thumb mode, the compiler can use these registers as fast storage.

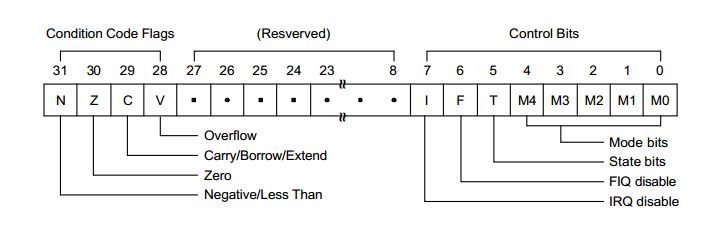

Status Register

CPSR and SPSR are two status registers in ARM920T. SPSR is used to temporarily save the value of the CPSR register.

Function of the status register

Save the most recent ALU calculation information

Controlling interrupts on and off

Set the processor mode

Exception handling

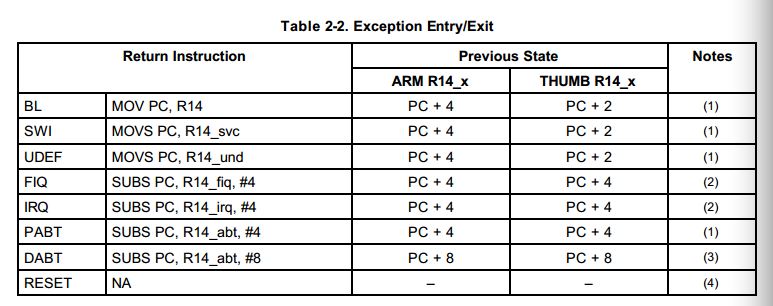

In ARM, all events that interrupt the normal execution of the program are called exceptions, and interrupts are also exceptions. When entering an exception, the hardware will automatically perform the following operations; but when exiting an exception, the following operations are implemented by our own software.

Entering an exception

1. Save the next instruction address in the appropriate LR register (whichever exception occurs will be saved in the LR register in that mode).

2. Copy the CPSR to the appropriate SPSR (whichever exception occurs will be saved in the SPSR register in that mode).

3. Set the mode bit in CPSR

4. PC gets the address from the corresponding interrupt vector table

Exit abnormally

1. Subtract an offset from the value in LR and assign it to PC

2. Copy the value of SPSR to CPSR

3. If the interrupt prohibition flag is set upon entry, clear the prohibition flag

for example:

HandleIRQ:

sub lr, lr, #4 @ Calculate the return address

stmdb sp!, { r0-r12,lr } @ Save the used registers

@ Note that the sp at this time is the sp in interrupt mode

@ The initial value is 3072 set above

ldr lr, =int_return @ Set the return address after calling ISR, namely EINT_Handle function

ldr pc, =EINT_Handle @ Call interrupt service function, int_return in interrupt.c:

ldmia sp!, { r0-r12,pc }^ @ interrupt return, ^ means copy the value of spsr to cpsr12345678910The interrupt pending bit needs to be cleared in the interrupt handling function EINT_Handle.

The following table shows the return functions that need to be executed when exiting various exceptions:

Interrupt vector table address

The following table shows the addresses of the interrupt vector table. These addresses are specified and cannot be changed by yourself.

Exception Priority

When multiple exceptions occur simultaneously, there is a fixed priority to determine which one is executed first.

high priority

1. Reset 2. Data abort 3. FIQ 4. IRQ 5. Prefetch abort123456

Low Priority

6. Undefined Instruction, Software interrupt

Previous article:Samsung CPU s3c2440 interrupt vector table problem

Next article:Analysis of s3c2440 startup process

Recommended ReadingLatest update time:2024-11-16 15:28

- Popular Resources

- Popular amplifiers

-

Detailed explanation of big data technology system: principles, architecture and practice (Dong Xicheng)

Detailed explanation of big data technology system: principles, architecture and practice (Dong Xicheng) -

Multi-port and shared memory architecture for high-performance ADAS SoCs

Multi-port and shared memory architecture for high-performance ADAS SoCs -

Machine Learning: Architecture in the Age of Artificial Intelligence

Machine Learning: Architecture in the Age of Artificial Intelligence -

Research and design of electric vehicle drive motor ECU control software based on AUTOSAR

Research and design of electric vehicle drive motor ECU control software based on AUTOSAR

Professor at Beihang University, dedicated to promoting microcontrollers and embedded systems for over 20 years.

Professor at Beihang University, dedicated to promoting microcontrollers and embedded systems for over 20 years.

- Innolux's intelligent steer-by-wire solution makes cars smarter and safer

- 8051 MCU - Parity Check

- How to efficiently balance the sensitivity of tactile sensing interfaces

- What should I do if the servo motor shakes? What causes the servo motor to shake quickly?

- 【Brushless Motor】Analysis of three-phase BLDC motor and sharing of two popular development boards

- Midea Industrial Technology's subsidiaries Clou Electronics and Hekang New Energy jointly appeared at the Munich Battery Energy Storage Exhibition and Solar Energy Exhibition

- Guoxin Sichen | Application of ferroelectric memory PB85RS2MC in power battery management, with a capacity of 2M

- Analysis of common faults of frequency converter

- In a head-on competition with Qualcomm, what kind of cockpit products has Intel come up with?

- Dalian Rongke's all-vanadium liquid flow battery energy storage equipment industrialization project has entered the sprint stage before production

- Allegro MicroSystems Introduces Advanced Magnetic and Inductive Position Sensing Solutions at Electronica 2024

- Car key in the left hand, liveness detection radar in the right hand, UWB is imperative for cars!

- After a decade of rapid development, domestic CIS has entered the market

- Aegis Dagger Battery + Thor EM-i Super Hybrid, Geely New Energy has thrown out two "king bombs"

- A brief discussion on functional safety - fault, error, and failure

- In the smart car 2.0 cycle, these core industry chains are facing major opportunities!

- The United States and Japan are developing new batteries. CATL faces challenges? How should China's new energy battery industry respond?

- Murata launches high-precision 6-axis inertial sensor for automobiles

- Ford patents pre-charge alarm to help save costs and respond to emergencies

- New real-time microcontroller system from Texas Instruments enables smarter processing in automotive and industrial applications

- Introduction to the method of board-level online compilation and downloading of C6000 DSP code

- How to draw this shape of 0.35x0.35

- EEWORLD University ---- ARM (IMX6U) bare metal video tutorial (punctual atom)

- EEWORLD University Hall----Texas Instruments field transmitter output interface/fieldbus solution

- Design of Portable Weather Instrument Based on MSP430 Microcontroller

- EEWORLD University ---- Top 5 Simple Electronic projects

- Thank you for being here, thank you EEWORLD Admin-okhxyyo and Orange Kai

- Recommended solutions to reduce Wi-Fi interference

- The MCU cannot run in DC-DC mode of BLUENRG-1

- Update the image

Detailed explanation of big data technology system: principles, architecture and practice (Dong Xicheng)

Detailed explanation of big data technology system: principles, architecture and practice (Dong Xicheng) Machine Learning: Architecture in the Age of Artificial Intelligence

Machine Learning: Architecture in the Age of Artificial Intelligence

京公网安备 11010802033920号

京公网安备 11010802033920号