0Introduction

With the advancement of technology and the continuous development of deep submicron integrated circuit technology, the integration of chips is getting higher and higher, and the scale of chips is getting larger and larger. In various chip application fields such as wireless communication and image processing, more and more system-on-chips (SoCs) choose to integrate analog circuit modules and digital circuit modules with different functions into the same chip, so as to achieve the best performance of the entire system while minimizing the cost. However, this has brought unexpected difficulties to chip testing and greatly increased the testing cost. As a bridge connecting digital systems and analog systems, ADC testing is particularly important. With the continuous improvement of ADC performance, the external environment of the chip has also become the main obstacle to ADC testing. In order to solve the above problems and more accurately test the real performance of ADC when it is integrated into SoC as an IP core, various ADC built-in self-test (Built-In-SelfTest) methods have emerged. How to accurately and efficiently provide test excitation for ADC built-in self-test is a very critical issue. This paper proposes a method for implementing a triangle wave signal generator that can be used for ADC on-chip testing. The generated triangle wave has very good linearity and can meet the test requirements of 14b high-precision ADC. The entire design is implemented using UMC 0.18μm CMOS technology with a power supply voltage of 1.8V.

1 Design Constraints of Triangle Wave Signal Generator

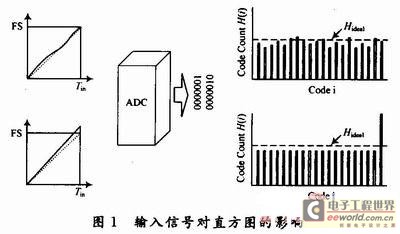

The code density histogram test method is based on statistics. When using this method to test the static characteristics of the ADC, the test excitation added must be as close to the ideal as possible. In this article, it is necessary to obtain a precise triangle wave as much as possible. If the obtained triangle wave signal has nonlinearity or gain error, then the histogram distribution of the measured code element will be uneven when the signal is used to test an ideal ADC (as shown in Figure 1). This unevenness comes from the error of the test excitation itself, so the integral nonlinearity (INL) and differential nonlinearity (DNL) of the ADC measured by this method introduce errors. In this way, the accuracy of the test results depends largely on the accuracy of the added triangle wave signal. Therefore, when designing a triangle wave generator, the linearity and amplitude of the required triangle wave generator must be determined based on the performance indicators of the ADC being tested. The triangle wave signal generator designed in this article must meet the test requirements of an ADC with an accuracy of 14b, so its accuracy requirement must not be less than 16b.

2 Principle of triangle wave signal generator

The principle of generating a triangular wave signal is to charge the capacitor with a constant positive current to obtain a uniformly rising ramp voltage. When the voltage rises to a certain value, a constant negative current is used to discharge the capacitor to obtain a uniformly falling ramp voltage. By alternating the positive and negative currents to charge and discharge the capacitor, a continuous triangular wave voltage signal can be obtained. The rising and falling slopes are determined by the ratio of the positive and negative currents to the capacitors I/C. In order to meet the requirements of ADC testing, the triangular wave signal should have good linearity and a low slope, which requires a precise small current and a large capacitor.

Figure 2 describes the principle of the triangle wave signal generator. In the figure, the operational amplifier, resistor R, and capacitor C form a square wave integrator; the comparator, resistor R1, and resistor R2 form a hysteresis comparator as a feedback control circuit. The working process of the circuit is as follows:

(1) When the comparator output level is low level VomL, capacitor C is in the charging state, and Vout continues to rise. When the value of Vout rises to make the voltage at the positive input terminal of the comparator higher than Vref, the comparator output flips and outputs high level VomH. At the same time, the current direction changes, and capacitor C enters the discharging state;

(2) When the comparator output level is high level VomH, capacitor C is in the discharge state, and Vout continues to decrease. When the value of Vout drops to the point where the voltage at the positive input of the comparator is lower than Vref, the comparator output flips and outputs low level VomL. At the same time, the current direction also flips, and capacitor C enters the charging state.

(3) Such cyclic oscillation generates a periodic continuous triangular wave voltage signal.

The threshold voltage of the output triangular wave voltage signal Vout is:

Where: Vref is the reference voltage of the negative terminal of the comparator; VomH and VomL are the high and low levels of the comparator output respectively.

From the above formula, we can see that the period T is determined by the RC constant, the peak-to-peak value Vout.pp and the high and low levels VomH and VomL of the comparator output. [page]

3 Specific circuit design and implementation

3.1 Operational Amplifier Design

The operational amplifier is a key part of the entire circuit structure, which directly determines the linearity and linear output range of the triangle wave signal generator. The operational amplifier, resistor R, and capacitor C form an integration circuit. Its main function is to keep the level at one end of the integration capacitor C stable, which requires the operational amplifier to have a higher gain; at the same time, in order to make the linear output range of the triangle wave signal generator as large as possible, the operational amplifier is required to have a larger output swing.

The operational amplifier in this article adopts a two-stage structure, as shown in Figure 3. Among them: the input stage adopts a sleeve cascode structure with a gain bootstrap circuit, including a main operational amplifier and an auxiliary operational amplifier. The main operational amplifier adopts a sleeve cascode structure with NMOS input, which has high gain, low power consumption and good frequency characteristics. The auxiliary operational amplifiers OP1 and OP2 are folded cascode fully differential structures with PMOS input and NMOS input, respectively, to further improve the gain of the operational amplifier. The second stage adopts a common source structure to improve the disadvantage of the small output swing of the sleeve cascode structure, and can also improve the open-loop gain of the operational amplifier to a certain extent. The increase in the number of stages will also introduce new zeros and poles, which will affect the stability of the operational amplifier. Therefore, compensation capacitor C must be added to ensure that the phase margin meets the requirements.

The AC amplitude-frequency and phase-frequency characteristics of the operational amplifier obtained by Spectre simulation are shown in Figure 4. Table 1 summarizes the basic performance parameters of the operational amplifier.

3.2 Hysteresis Comparator Design

The hysteresis characteristic of the hysteresis comparator is the result of the introduction of positive feedback in the comparator. The hysteresis comparator has two input thresholds. When the input voltage passes through one of the thresholds, the output voltage will change, and the input threshold will jump to another value. To change the output again, the input must reach the threshold after the jump. At the same time as the output changes, the threshold will jump back to the original value. The hysteresis comparator circuit and input-output characteristic curve used in this article are shown in Figure 5.

The two input thresholds are:

The comparator circuit in the hysteresis comparator is implemented with a two-stage open-loop op amp. Since the comparator back stage is a 2mΩ resistor, the comparator output stage resistance must be low enough to prevent the comparator output voltage from failing to reach the power supply voltage and ground voltage due to resistor voltage division. Therefore, an inverter chain with a large width-to-length ratio is added after the two-stage open-loop op amp to obtain a lower output resistance, as shown in Figure 6.

[page]

[page]

4 Simulation Results

The overall circuit of the triangle wave signal generator is simulated at the transistor level. The simulated triangle wave voltage signal range is 82mV to 1.719V, and the period is 366μs, as shown in FIG7 .

The triangle wave signal is sampled for multiple cycles, and the three voltage ranges of 0.1-1.7V, 0.2-0.6V, and 0.3-1.5V are quantized and converted using the 16b ideal ADC, and the corresponding code density histogram analysis is performed to obtain the respective DNL and INL, as shown in Figure 8. As can be seen from Figure 8, for the quantization of the 16b ideal ADC, the INL of these three different voltage ranges is below 1LSB (equivalent to INL < 24μV), which can meet the test of the static characteristics of the 14b ADC.

5 Conclusion

This paper designs a high-precision and high-linearity analog triangle wave signal generator for high-precision ADC on-chip testing, which can provide effective excitation for on-chip testing of ADC static parameters up to 14b. The simulation results show that the triangle wave voltage signal generated by the signal generator ranges from 82mV to 1.719V, the period is 366μs, INL<24μV, and the equivalent accuracy reaches more than 16b. Its amplitude and frequency can be adjusted according to specific design requirements, and its linearity is good, which can meet the test requirements of 14b high-precision ADC static parameters.

Previous article:10GBASE-T Ethernet Signal Integrity Measurement Solution

Next article:Interference problems caused by poor power grounding on oscilloscope testing

Recommended ReadingLatest update time:2024-11-16 19:40

- Popular Resources

- Popular amplifiers

- Keysight Technologies Helps Samsung Electronics Successfully Validate FiRa® 2.0 Safe Distance Measurement Test Case

- From probes to power supplies, Tektronix is leading the way in comprehensive innovation in power electronics testing

- Seizing the Opportunities in the Chinese Application Market: NI's Challenges and Answers

- Tektronix Launches Breakthrough Power Measurement Tools to Accelerate Innovation as Global Electrification Accelerates

- Not all oscilloscopes are created equal: Why ADCs and low noise floor matter

- Enable TekHSI high-speed interface function to accelerate the remote transmission of waveform data

- How to measure the quality of soft start thyristor

- How to use a multimeter to judge whether a soft starter is good or bad

- What are the advantages and disadvantages of non-contact temperature sensors?

- Innolux's intelligent steer-by-wire solution makes cars smarter and safer

- 8051 MCU - Parity Check

- How to efficiently balance the sensitivity of tactile sensing interfaces

- What should I do if the servo motor shakes? What causes the servo motor to shake quickly?

- 【Brushless Motor】Analysis of three-phase BLDC motor and sharing of two popular development boards

- Midea Industrial Technology's subsidiaries Clou Electronics and Hekang New Energy jointly appeared at the Munich Battery Energy Storage Exhibition and Solar Energy Exhibition

- Guoxin Sichen | Application of ferroelectric memory PB85RS2MC in power battery management, with a capacity of 2M

- Analysis of common faults of frequency converter

- In a head-on competition with Qualcomm, what kind of cockpit products has Intel come up with?

- Dalian Rongke's all-vanadium liquid flow battery energy storage equipment industrialization project has entered the sprint stage before production

- Allegro MicroSystems Introduces Advanced Magnetic and Inductive Position Sensing Solutions at Electronica 2024

- Car key in the left hand, liveness detection radar in the right hand, UWB is imperative for cars!

- After a decade of rapid development, domestic CIS has entered the market

- Aegis Dagger Battery + Thor EM-i Super Hybrid, Geely New Energy has thrown out two "king bombs"

- A brief discussion on functional safety - fault, error, and failure

- In the smart car 2.0 cycle, these core industry chains are facing major opportunities!

- The United States and Japan are developing new batteries. CATL faces challenges? How should China's new energy battery industry respond?

- Murata launches high-precision 6-axis inertial sensor for automobiles

- Ford patents pre-charge alarm to help save costs and respond to emergencies

- New real-time microcontroller system from Texas Instruments enables smarter processing in automotive and industrial applications

- Looking for second-hand six-axis force sensor

- Application of resettable fuse

- Detailed explanation of MSP430F149 serial port receiving and sending program

- 【Evaluation of SGP40】-SGP40 temperature and humidity test

- When choosing crystal oscillators, should we choose imported or domestic ones?

- Does anyone know how to write a DLL for a card reader/writer? Is there any relevant information?

- Still using the burning method to test fabric composition? Now there is a new method.

- How to pair MCU with FPGA to improve system efficiency?

- [National Technology N32G457 Review] 1. Brief review of the first power-on

- Helping to be efficient, green and safe, unlock the secrets of high-quality automotive design with Nexperia!

ESP32-S3 source code

ESP32-S3 source code 【Follow me Season 2 Episode 2】Arduion UR4 homework submission code

【Follow me Season 2 Episode 2】Arduion UR4 homework submission code MCU C language programming and Proteus simulation technology (Xu Aijun)

MCU C language programming and Proteus simulation technology (Xu Aijun)

京公网安备 11010802033920号

京公网安备 11010802033920号