So what are the characteristics of the PCI-E 3.0 bus? What is special about its testing? Let's discuss it here.

The purpose of developing the PCI-E Gen3 specification is to provide an effective data transmission rate twice as high as PCI-E Gen2 based on the existing cheap FR4 boards and connectors, while maintaining compatibility with the original Gen1 and Gen2 devices. Although this is a simple goal, it is not easy to achieve.

We know that the data transmission rate of PCI-E 2nd generation on each pair of differential lines is 5Gbps, which is twice the data rate of 1st generation; and PCI-E 3rd generation will double the rate of 2nd generation, so it is natural to increase the data transmission rate to 10Gbps. However, this 10Gbps brings a big problem, because PCs and servers generally use cheap FR4 PCB boards and cheap connectors for cost considerations. If the boards and connectors are not replaced, it is difficult to ensure that the 10Gbps signal can still be reliably transmitted over a long distance on the original signal path (the typical distance is 15 to 30cm). Therefore, PCI-SIG finally decided to set the data transmission rate of PCI-E 3rd generation at 8Gbps. However, 8Gbps is not twice as high as 5Gbps in 2nd generation, so the PCI-E Association decided to remove the 8b/10b encoding used in 1st and 2nd generations in the 3rd generation standard.

We know that in order to ensure data transmission density, DC balance and embedded clock in PCI-E 1 and 2, 8-bit data will be encoded into 10-bit data transmission. Therefore, the actual effective data transmission rate of 5Gbps is 5Gbps×8b/10b=4Gbps. In this way, if 8b/10b encoding is not used in PCI-E 3, its effective data transmission rate can be increased by 1 times compared with 4Gbps in 2. But here comes the problem again. If the data is not transmitted through encoding, it is difficult to ensure data transmission density and DC balance, and the clock recovery circuit at the receiving end is also easy to lose lock. In order to solve this problem, PCI-E 3 uses a scrambling method, that is, before data transmission, it is first XORed with a polynomial, so that the data on the transmission link looks more random, and the same polynomial is used to recover the data at the receiving end.

Through the above method, PCI-E Gen3 can use 8Gbps transmission rate to achieve a data transmission rate that is twice as high as 5Gbps of Gen2. In actual applications, PCI-E Gen3 bus still has data encoding, but it uses 128b/130b encoding, which has high encoding efficiency, so the loss of effective bus bandwidth is much smaller than 8b/10b encoding.

Changes in PCI-E 3.0 Transmitter and Receiver

But the problem is far from over. Even if the data rate is only 8Gbps, some new problems need to be solved to achieve reliable transmission on the original cheap PCB and connectors. The biggest problem is signal loss. FR4 board has a great attenuation on the high-frequency components of the signal. The higher the signal rate, the more high-frequency components there are, so the attenuation is greater. The figure below shows the eye diagram of the signal after the signal of different rates is transmitted through the 10-inch FR4 board PCB. We can see that the eye diagram of the 8Gbps signal is basically invisible at the receiving end, let alone effective data reception.

In order to solve this problem, de-emphasis technology is used in PCI-E generation 1 and generation 2, that is, the signal transmitter (TX) increases the amplitude of the jump bit (representing the high-frequency component in the signal) when sending the signal, so as to partially compensate for the attenuation of the high-frequency component of the transmission line, thereby obtaining a better eye diagram. PCI-E generation 1 uses -3.5db de-emphasis, and PCI-E generation 2 uses -3.5db and -6db de-emphasis. For generation 3, due to the higher signal rate, more complex de-emphasis technology is required. Therefore, in addition to increasing the amplitude of the jump bit compared to the non-jump bit, the amplitude of the bit before the jump bit should also be increased. This increased amplitude is usually called Preshoot. The following figure is an example of the impact of the pre-emphasis technology used in PCI-E generation 3 on the waveform (reference: PCI Express® Base Specification 3.0).

In order to cope with complex link environments, PCI-E Gen 3 specifies a total of 11 different combinations of Preshoot and De-emphasis. Each combination is called a Preset. In actual applications, the Tx and Rx ends can negotiate an optimal Preset value based on the signal quality received by the receiving end during the Link Training phase. The following figure shows the combination of 11 Presets (reference: PCI Express® Base Specification 3.0). For example, P4 represents no pre-emphasis, and P7 represents the strongest pre-emphasis.

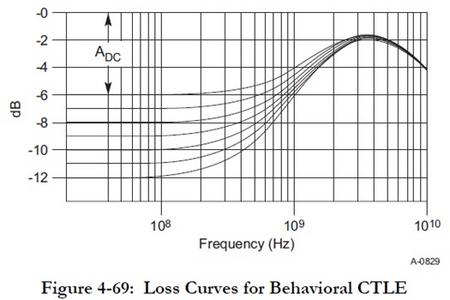

Is this enough? Experiments have shown that compensating for the high frequency of the signal at the transmitting end is not enough, so the PCI-E 3rd generation standard stipulates that the signal should be equalized at the receiving end (RX end) to further compensate for the line loss. The equalization circuit is difficult to implement. It was previously mainly used in the backplane of communication equipment or in long cable transmission. Now it is gradually being used in the computer field. For example, equalization technology is also used in USB3.0 and SATA 6G. The figure below shows the requirements for the frequency response characteristics of the equalizer in PCI-E 3.0. We can see that there are many options for the strength of the equalizer. In the Link Training stage, the TX and RX ends will negotiate an optimal combination (reference: PCI Express® Base Specification 3.0).

After combining various signal processing technologies and a lot of experiments, PCI-E 3.0 has finally achieved an effective data transmission rate twice as high as PCI-E 2 on the basis of existing FR4 boards and connectors. But we also see that PCI-E 3 chips will become more complex and the difficulty of system design will also be greater. How to ensure the reliability and good compatibility of PCI-E 3 bus has become a severe challenge for designers and testers.

Previous article:PCIE3.0 transmitter signal quality test

Next article:SAS interconnect impedance and return loss test

- Popular Resources

- Popular amplifiers

- From probes to power supplies, Tektronix is leading the way in comprehensive innovation in power electronics testing

- Seizing the Opportunities in the Chinese Application Market: NI's Challenges and Answers

- Tektronix Launches Breakthrough Power Measurement Tools to Accelerate Innovation as Global Electrification Accelerates

- Not all oscilloscopes are created equal: Why ADCs and low noise floor matter

- Enable TekHSI high-speed interface function to accelerate the remote transmission of waveform data

- How to measure the quality of soft start thyristor

- How to use a multimeter to judge whether a soft starter is good or bad

- What are the advantages and disadvantages of non-contact temperature sensors?

- In what situations are non-contact temperature sensors widely used?

- LED chemical incompatibility test to see which chemicals LEDs can be used with

- Application of ARM9 hardware coprocessor on WinCE embedded motherboard

- What are the key points for selecting rotor flowmeter?

- LM317 high power charger circuit

- A brief analysis of Embest's application and development of embedded medical devices

- Single-phase RC protection circuit

- stm32 PVD programmable voltage monitor

- Introduction and measurement of edge trigger and level trigger of 51 single chip microcomputer

- Improved design of Linux system software shell protection technology

- What to do if the ABB robot protection device stops

- Analysis of the application of several common contact parts in high-voltage connectors of new energy vehicles

- Wiring harness durability test and contact voltage drop test method

- From probes to power supplies, Tektronix is leading the way in comprehensive innovation in power electronics testing

- From probes to power supplies, Tektronix is leading the way in comprehensive innovation in power electronics testing

- Sn-doped CuO nanostructure-based ethanol gas sensor for real-time drunk driving detection in vehicles

- Design considerations for automotive battery wiring harness

- Do you know all the various motors commonly used in automotive electronics?

- What are the functions of the Internet of Vehicles? What are the uses and benefits of the Internet of Vehicles?

- Power Inverter - A critical safety system for electric vehicles

- Analysis of the information security mechanism of AUTOSAR, the automotive embedded software framework

- An indispensable element! Make fast charging design simple

- FAQ_ How to choose a high-speed crystal for BlueNRG-x

- 2021 STMicroelectronics Industry Summit Tour- Shanghai/Beijing

- Summary: RCSN Play Anxinke's new esp32s3 development board

- How should Japan deal with nuclear waste water? Give us some ideas

- RTL diagram timing, can anyone help me explain why the two outputs in this diagram are in the two-choice mode?

- Now DCDC design tools are made like this

- The disappearing boundary between MCU and MPU

- DS18B20 STM32G474 driver

- 【Fudan Micro FM33LC046N】Clock output test

KA22131D

KA22131D

京公网安备 11010802033920号

京公网安备 11010802033920号