1 Introduction

Multiple retriggering technology is used in many occasions. For example, if a gear with 30 teeth has a gear meshing coefficient of 1.2, and the stress of one tooth is measured when it is meshed multiple times, the meshing time of one tooth only accounts for 1.2/30 of the time of the gear turning one circle, and the remaining 28.8/30 of the time is in the idle state, and the idle state record is meaningless. For this reason, multiple retriggering technology is developed, with tooth stress as the internal trigger signal, and only useful signals after each trigger are recorded, with negative delay, and the idle state is not recorded. Until the storage space of the recording device is filled, the storage space can be effectively utilized to record more useful signals.

2 Overall design of multiple retriggering storage test system

2.1 Working principle of multiple retriggering storage test system

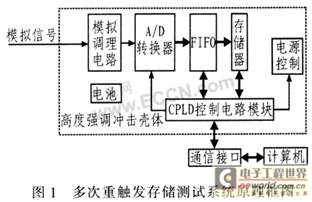

Figure 1 is a block diagram of the principle of the multiple retriggering storage test system. Its working principle is: after the measured signal is converted into an electrical signal by the sensor, it is input into the analog conditioning circuit, and then input into the A/D converter after amplification and filtering, the analog signal is converted into a digital signal, and then transmitted to the memory through the FIFO, and the computer reads the data through the communication interface. Among them, the conversion and reading clock of the A/D converter of the storage test system, the read and write clock of the FIFO and memory, and the push address clock are all controlled by the CPLD.

2.2 Implementation of negative delay

Dynamic information storage requires the real and effective recording of useful signals. According to the characteristics of the measured signal, it is necessary to record the data of the signal before the trigger in a very short time, which requires the use of negative delay technology. Negative delay is also called advance transmission, that is, the trigger acquisition time of the trigger signal is advanced for a period of time as the starting point of the transmission data. The system design uses FIFO memory to achieve negative delay. When the trigger signal does not arrive, the data output by the A/D converter is continuously written into the FIFO memory, and the data converted by the A/D converter continuously refreshes the content of the FIFO memory. Once the trigger signal arrives, the data begins to be written from the FIFO to the memory.

2.3 Selection of main components

The system design uses the AD7492 A/D converter. This device is a 12-bit high-speed, low-power, successive approximation A/D converter. At 5 V voltage and 1 MS/s rate, its average current is only 1.72 mA and power consumption is 8.6 mW; at 5 V voltage and 500 kS/s data transmission rate, the current consumption is 1.24 mA, so the device can meet the low power consumption requirements of the system. Since the total capacity of the memory designed for this system is 512 KB, a N08T163 memory with a capacity of 512 KB is selected. And the self-made FIFO memory is realized through the timing of static memory, and the power consumption is about 1/10 of similar FIFO memory. The negative delay record of the system design is 1 KB, and the N02L163WC2A memory with a capacity of 128 KB is selected. In view of the low power consumption, small size and complex control logic of the storage test system, the EPM7128BTCl44-4 CPLD of the MAX7000B series is used as the controller. The device is a high-performance, low-power CMOS CPLD with 2500 available logic gates, a pin-to-pin transmission delay of 4.0 ns, and a system operating frequency of up to 243.9 MHz.

3 Design of CPLD control circuit

The multiple re-trigger storage test system based on CPLD is mainly composed of A/D converter, memory, FIFO and controller CPLD, among which the CPLD control circuit is composed of clock, multiple re-trigger, FIFO address generation, memory address generation, memory full count, power management and computer communication modules, as shown in Figure 2.

3.1 Functions of each module of the control circuit

(1) Power management module This module mainly controls the power consumption of the system. When the system is in sleep mode, only Vcc supplies power to the CPLD; when the system enters normal working state, Vcc, VDD and VEE are simultaneously supplied, and the crystal oscillator works. When the sampling is completed, the system turns off VEE, the analog part enters sleep mode, and the crystal oscillator stops working. This module can meet the low power consumption requirements of the system.

(2) The 4 MHz signal provided by the clock module crystal oscillator is passed through four binary dividers to obtain clock signals of 2 MHz, 1 MHz, 500 kHz and 250 kHz respectively. These signals are combined to obtain the sampling signal convst of the A/D converter, the write signal of the FIFO, the read signal ffwr_adread of the A/D converter and the push address signal ff_dz of the FIFO, all of which are 250 kHz.

(3) When the external multiple re-trigger signal m_tri arrives, the open signal generated by the D flip-flop becomes high level, and the counter starts counting the clock signal ff_dz. It stops counting after counting every 8 KB, and generates a clear signal clr to clear the open signal and wait for the next trigger signal. The clock signal clkl generated by the clock signal ff_dz and the open signal is used as the push address signal and write signal when writing to the memory. The open signal is inverted and connected to the memory enable terminal.

(4) FIFO address generation module The CPLD controls the address of the FIFO by the clock module ff_dz signal. The FIFO address is pushed at the falling edge of the clock signal ff_dz. [page]

(5) Memory address generation module The multiple re-trigger module generates the clkl signal as the memory address push signal m_dz to push the address, write the converted data into the memory, stop the write operation after writing 8 KB, and wait for the next trigger signal. The memory is full of 512. KB. After that, the address push and write operation are stopped, waiting for the computer to read. When reading, the computer sends a reading pulse to the CPLD every time, the address signal advances 1 bit, and the CPLD reads 1 data from the corresponding address unit in the memory.

(6) Memory full count module When the multiple re-trigger signal m_tri arrives, the open signal becomes high level, and becomes low level after counting 8 KB, waiting for the next trigger signal. Therefore, the counter is used to count the falling edge of the open signal. After counting 64, the memory full signal tc becomes high level.

3.2 CPLD overall control circuit simulation and analysis

Figure 3 is the CPLD overall control circuit simulation diagram. In Figure 3, the trigger signal m_tri is generated 3 times. The nopen signal shows that the memory is selected 3 times. The change of the memory address signal m_addr shows that the memory records 8 KB of each trigger signal and continuously updates the FIFO data. After the first trigger signal m_tri arrives, the nopen signal becomes low, which means the memory is selected. At this time, the push address signal and write signal m_dz signal of the memory are generated, and the push address is given to the memory at the falling edge. The memory performs a write operation during the low level period. After the trigger signal m_tri arrives, the count is full of 8 KB, the nopen signal generates a high level to not select the memory, and the push address signal and write signal m_dz of the memory become high.

4 Experimental verification

The function of the test system is verified by experiment. In the experiment, 8 trigger signals are loaded to the test system and 8 consecutive acquisitions are made. Since the system is designed to sample up to 64 times, if the number of re-trigger signals does not reach 64 times, a forced reading signal needs to be manually given to the tester to end the instrument sampling. After the multiple re-trigger signals are valid for 8 times, the manual forced reading signal causes the instrument to end sampling, and the host computer software determines whether the acquired waveform amplitude corresponds to the manually adjusted amplitude. If so, it indicates that the system sampling is normal.

Experimental steps: The tester is powered on, and the red light of the tester sampling status indicator is on. Connect the programming reading line to the computer, open the programming interface, set the sampling frequency of multiple re-triggering, and use the default settings for other options. After programming is completed, unplug the programming reading line, power on the tester (ON=0), and the red light starts to flash. Connect the output of the charge calibrator to the channel end on the tester panel, set the output waveform of the charge calibrator to a sine wave, and the charge amount is 2 000 PC. Output signal, give the system a trigger signal (M_TRI=1), the red light flashes for a period of time and then stops flashing, indicating that the first sampling of the system is completed. At this time, adjust the output charge of the charge calibrator to 4 000 PC. Give the system another trigger signal, repeat the previous process, change the charge amount after each sampling is completed, until the green light is on, connect the programming reading line to the computer, read the data through the host computer software, and after the data is read, the tester is powered off (OFF=0), and the power of the tester is disconnected. Figure 4 shows the waveform of multiple re-triggering. The measured charge values obtained by converting and processing the data in Figure 4 are shown in Table 1. It can be seen from Table 1 that the amplitude of the collected waveform is consistent with the order of adjustment, and the system design meets the requirements.

5 Conclusion

The multiple re-trigger storage test system based on CPLD designed in this paper has stable performance and high measurement accuracy. It can work normally in harsh environments such as high shock, and meets the low power consumption and miniaturization requirements of the system, and realizes undistorted sampling and storage of signals. This system can record multiple re-trigger signals in real time, and each signal recording has a negative delay. When reading data, the recorded waveform can be accurately reproduced without program adjustment. Therefore, storage test technology has broad prospects in the measurement of multiple transient signals.

Keywords:CPLD

Reference address:Design of multiple re-trigger storage test system based on CPLD

Multiple retriggering technology is used in many occasions. For example, if a gear with 30 teeth has a gear meshing coefficient of 1.2, and the stress of one tooth is measured when it is meshed multiple times, the meshing time of one tooth only accounts for 1.2/30 of the time of the gear turning one circle, and the remaining 28.8/30 of the time is in the idle state, and the idle state record is meaningless. For this reason, multiple retriggering technology is developed, with tooth stress as the internal trigger signal, and only useful signals after each trigger are recorded, with negative delay, and the idle state is not recorded. Until the storage space of the recording device is filled, the storage space can be effectively utilized to record more useful signals.

2 Overall design of multiple retriggering storage test system

2.1 Working principle of multiple retriggering storage test system

Figure 1 is a block diagram of the principle of the multiple retriggering storage test system. Its working principle is: after the measured signal is converted into an electrical signal by the sensor, it is input into the analog conditioning circuit, and then input into the A/D converter after amplification and filtering, the analog signal is converted into a digital signal, and then transmitted to the memory through the FIFO, and the computer reads the data through the communication interface. Among them, the conversion and reading clock of the A/D converter of the storage test system, the read and write clock of the FIFO and memory, and the push address clock are all controlled by the CPLD.

2.2 Implementation of negative delay

Dynamic information storage requires the real and effective recording of useful signals. According to the characteristics of the measured signal, it is necessary to record the data of the signal before the trigger in a very short time, which requires the use of negative delay technology. Negative delay is also called advance transmission, that is, the trigger acquisition time of the trigger signal is advanced for a period of time as the starting point of the transmission data. The system design uses FIFO memory to achieve negative delay. When the trigger signal does not arrive, the data output by the A/D converter is continuously written into the FIFO memory, and the data converted by the A/D converter continuously refreshes the content of the FIFO memory. Once the trigger signal arrives, the data begins to be written from the FIFO to the memory.

2.3 Selection of main components

The system design uses the AD7492 A/D converter. This device is a 12-bit high-speed, low-power, successive approximation A/D converter. At 5 V voltage and 1 MS/s rate, its average current is only 1.72 mA and power consumption is 8.6 mW; at 5 V voltage and 500 kS/s data transmission rate, the current consumption is 1.24 mA, so the device can meet the low power consumption requirements of the system. Since the total capacity of the memory designed for this system is 512 KB, a N08T163 memory with a capacity of 512 KB is selected. And the self-made FIFO memory is realized through the timing of static memory, and the power consumption is about 1/10 of similar FIFO memory. The negative delay record of the system design is 1 KB, and the N02L163WC2A memory with a capacity of 128 KB is selected. In view of the low power consumption, small size and complex control logic of the storage test system, the EPM7128BTCl44-4 CPLD of the MAX7000B series is used as the controller. The device is a high-performance, low-power CMOS CPLD with 2500 available logic gates, a pin-to-pin transmission delay of 4.0 ns, and a system operating frequency of up to 243.9 MHz.

3 Design of CPLD control circuit

The multiple re-trigger storage test system based on CPLD is mainly composed of A/D converter, memory, FIFO and controller CPLD, among which the CPLD control circuit is composed of clock, multiple re-trigger, FIFO address generation, memory address generation, memory full count, power management and computer communication modules, as shown in Figure 2.

3.1 Functions of each module of the control circuit

(1) Power management module This module mainly controls the power consumption of the system. When the system is in sleep mode, only Vcc supplies power to the CPLD; when the system enters normal working state, Vcc, VDD and VEE are simultaneously supplied, and the crystal oscillator works. When the sampling is completed, the system turns off VEE, the analog part enters sleep mode, and the crystal oscillator stops working. This module can meet the low power consumption requirements of the system.

(2) The 4 MHz signal provided by the clock module crystal oscillator is passed through four binary dividers to obtain clock signals of 2 MHz, 1 MHz, 500 kHz and 250 kHz respectively. These signals are combined to obtain the sampling signal convst of the A/D converter, the write signal of the FIFO, the read signal ffwr_adread of the A/D converter and the push address signal ff_dz of the FIFO, all of which are 250 kHz.

(3) When the external multiple re-trigger signal m_tri arrives, the open signal generated by the D flip-flop becomes high level, and the counter starts counting the clock signal ff_dz. It stops counting after counting every 8 KB, and generates a clear signal clr to clear the open signal and wait for the next trigger signal. The clock signal clkl generated by the clock signal ff_dz and the open signal is used as the push address signal and write signal when writing to the memory. The open signal is inverted and connected to the memory enable terminal.

(4) FIFO address generation module The CPLD controls the address of the FIFO by the clock module ff_dz signal. The FIFO address is pushed at the falling edge of the clock signal ff_dz. [page]

(5) Memory address generation module The multiple re-trigger module generates the clkl signal as the memory address push signal m_dz to push the address, write the converted data into the memory, stop the write operation after writing 8 KB, and wait for the next trigger signal. The memory is full of 512. KB. After that, the address push and write operation are stopped, waiting for the computer to read. When reading, the computer sends a reading pulse to the CPLD every time, the address signal advances 1 bit, and the CPLD reads 1 data from the corresponding address unit in the memory.

(6) Memory full count module When the multiple re-trigger signal m_tri arrives, the open signal becomes high level, and becomes low level after counting 8 KB, waiting for the next trigger signal. Therefore, the counter is used to count the falling edge of the open signal. After counting 64, the memory full signal tc becomes high level.

3.2 CPLD overall control circuit simulation and analysis

Figure 3 is the CPLD overall control circuit simulation diagram. In Figure 3, the trigger signal m_tri is generated 3 times. The nopen signal shows that the memory is selected 3 times. The change of the memory address signal m_addr shows that the memory records 8 KB of each trigger signal and continuously updates the FIFO data. After the first trigger signal m_tri arrives, the nopen signal becomes low, which means the memory is selected. At this time, the push address signal and write signal m_dz signal of the memory are generated, and the push address is given to the memory at the falling edge. The memory performs a write operation during the low level period. After the trigger signal m_tri arrives, the count is full of 8 KB, the nopen signal generates a high level to not select the memory, and the push address signal and write signal m_dz of the memory become high.

4 Experimental verification

The function of the test system is verified by experiment. In the experiment, 8 trigger signals are loaded to the test system and 8 consecutive acquisitions are made. Since the system is designed to sample up to 64 times, if the number of re-trigger signals does not reach 64 times, a forced reading signal needs to be manually given to the tester to end the instrument sampling. After the multiple re-trigger signals are valid for 8 times, the manual forced reading signal causes the instrument to end sampling, and the host computer software determines whether the acquired waveform amplitude corresponds to the manually adjusted amplitude. If so, it indicates that the system sampling is normal.

Experimental steps: The tester is powered on, and the red light of the tester sampling status indicator is on. Connect the programming reading line to the computer, open the programming interface, set the sampling frequency of multiple re-triggering, and use the default settings for other options. After programming is completed, unplug the programming reading line, power on the tester (ON=0), and the red light starts to flash. Connect the output of the charge calibrator to the channel end on the tester panel, set the output waveform of the charge calibrator to a sine wave, and the charge amount is 2 000 PC. Output signal, give the system a trigger signal (M_TRI=1), the red light flashes for a period of time and then stops flashing, indicating that the first sampling of the system is completed. At this time, adjust the output charge of the charge calibrator to 4 000 PC. Give the system another trigger signal, repeat the previous process, change the charge amount after each sampling is completed, until the green light is on, connect the programming reading line to the computer, read the data through the host computer software, and after the data is read, the tester is powered off (OFF=0), and the power of the tester is disconnected. Figure 4 shows the waveform of multiple re-triggering. The measured charge values obtained by converting and processing the data in Figure 4 are shown in Table 1. It can be seen from Table 1 that the amplitude of the collected waveform is consistent with the order of adjustment, and the system design meets the requirements.

5 Conclusion

The multiple re-trigger storage test system based on CPLD designed in this paper has stable performance and high measurement accuracy. It can work normally in harsh environments such as high shock, and meets the low power consumption and miniaturization requirements of the system, and realizes undistorted sampling and storage of signals. This system can record multiple re-trigger signals in real time, and each signal recording has a negative delay. When reading data, the recorded waveform can be accurately reproduced without program adjustment. Therefore, storage test technology has broad prospects in the measurement of multiple transient signals.

Previous article:Simplifying Boundary Scan Testing with PLDs

Next article:Crystal and mask quality control inspection

- Popular Resources

- Popular amplifiers

Recommended Content

Latest Test Measurement Articles

- From probes to power supplies, Tektronix is leading the way in comprehensive innovation in power electronics testing

- Seizing the Opportunities in the Chinese Application Market: NI's Challenges and Answers

- Tektronix Launches Breakthrough Power Measurement Tools to Accelerate Innovation as Global Electrification Accelerates

- Not all oscilloscopes are created equal: Why ADCs and low noise floor matter

- Enable TekHSI high-speed interface function to accelerate the remote transmission of waveform data

- How to measure the quality of soft start thyristor

- How to use a multimeter to judge whether a soft starter is good or bad

- What are the advantages and disadvantages of non-contact temperature sensors?

- In what situations are non-contact temperature sensors widely used?

MoreSelected Circuit Diagrams

MorePopular Articles

- LED chemical incompatibility test to see which chemicals LEDs can be used with

- Application of ARM9 hardware coprocessor on WinCE embedded motherboard

- What are the key points for selecting rotor flowmeter?

- LM317 high power charger circuit

- A brief analysis of Embest's application and development of embedded medical devices

- Single-phase RC protection circuit

- stm32 PVD programmable voltage monitor

- Introduction and measurement of edge trigger and level trigger of 51 single chip microcomputer

- Improved design of Linux system software shell protection technology

- What to do if the ABB robot protection device stops

MoreDaily News

- Analysis of the application of several common contact parts in high-voltage connectors of new energy vehicles

- Wiring harness durability test and contact voltage drop test method

- From probes to power supplies, Tektronix is leading the way in comprehensive innovation in power electronics testing

- From probes to power supplies, Tektronix is leading the way in comprehensive innovation in power electronics testing

- Sn-doped CuO nanostructure-based ethanol gas sensor for real-time drunk driving detection in vehicles

- Design considerations for automotive battery wiring harness

- Do you know all the various motors commonly used in automotive electronics?

- What are the functions of the Internet of Vehicles? What are the uses and benefits of the Internet of Vehicles?

- Power Inverter - A critical safety system for electric vehicles

- Analysis of the information security mechanism of AUTOSAR, the automotive embedded software framework

Guess you like

- stm8

- Grab and run! EPOS implementation in unmanned retail stores

- EEWORLD University Hall----Introduction to Isolation Topology

- I would like to ask why this compensation circuit can achieve advance compensation.

- Please recommend a single chip analog to PWM solution

- CC3200 module first article - wlan_ap routine test

- How to self-test the fault of resistor parallel circuit?

- Single-supply applications

- Share a problem of MOS tubes being frequently damaged.

- CMOS Analog Integrated Circuit Design and Simulation.pdf

BA728FT2

BA728FT2

京公网安备 11010802033920号

京公网安备 11010802033920号