Practical Information | What is PCB Reflow? High-Speed Signal Reflow Path Analysis

▲ For more exciting activities, please click on the blue words above and follow us!

The basic concept of reflow

After all, both the driver and receiver are specified as voltage-mode devices, so why consider current?

In fact, basic circuit theory tells us that signals are transmitted by electric current, or more specifically, the movement of electrons. One of the characteristics of electron flow is that electrons never stay anywhere. No matter where the current flows, it must come back. Therefore, the current always flows in a loop, and any signal in the circuit exists in the form of a closed loop .

For high-frequency signal transmission, it is actually a process of charging the dielectric capacitor sandwiched between the transmission line and the DC layer.

Impact of Reflux

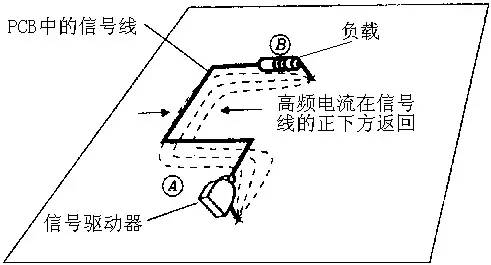

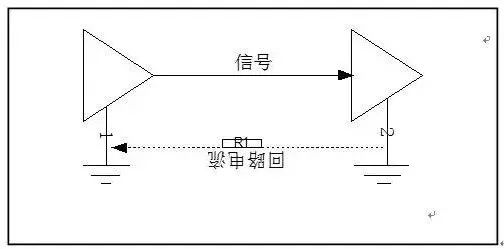

When the current starts from the signal driver, flows through the signal line, and is injected into the signal receiving end, there is always a return current in the opposite direction: starting from the ground pin of the load, passing through the copper plane, flowing to the signal source, and forming a closed loop with the current flowing through the signal line.

The noise frequency caused by this current flowing through the copper clad plane is equivalent to the signal frequency. The higher the signal frequency, the higher the noise frequency.

Logic gates do not respond to the absolute input signal, but to the difference between the input signal and a reference pin. Single-terminated circuits react to the difference between the incoming signal and its logic ground reference plane, so disturbances on the ground reference plane are as important as disturbances on the signal path. Logic gates respond to the input pin and the designated reference pin, and we don't know which is the designated reference pin (usually the negative supply for TTL and the positive supply for ECL, but not always), so the interference immunity of differential signals can have a good effect on ground bounce noise and power plane sliding.

IC1 is the signal output terminal, IC2 is the signal input terminal (to simplify the PCB model, it is assumed that the receiving terminal contains a bottom connection resistor), and the third layer is the ground layer. The ground of IC1 and IC2 both come from the third layer ground layer. The upper right corner of the TOP layer is a power plane, which is connected to the positive pole of the power supply. C1 and C2 are the decoupling capacitors of IC1 and IC2 respectively. The power supply and ground pins of the chip shown in the figure are the power supply and ground of the transmitting and receiving signal ends.

At low frequency, if the S1 terminal outputs a high level, the entire current loop is that the power supply is connected to the VCC power plane through a wire, then enters IC1 through the orange path, then comes out from the S1 terminal, enters IC2 through the R1 terminal through the second layer of wire, then enters the GND layer, and returns to the negative pole of the power supply through the red path.

At high frequencies, the distribution characteristics of the PCB will have a great impact on the signal. The ground return current we often talk about is a problem that is often encountered in high-frequency signals. When there is an increased current in the signal line from S1 to R1, the external magnetic field changes rapidly, causing the nearby conductor to induce a reverse current. If the ground plane of the third layer is a complete ground plane, then a current marked by a blue dotted line will be generated on the ground plane. If the TOP layer has a complete power plane, there will also be a return along the blue dotted line on the TOP layer. At this time, the signal loop has the smallest current loop, the energy radiated outward is the smallest, and the ability to couple external signals is also the smallest. The skin effect at high frequencies also radiates the least energy outward, and the principle is the same.

Since the high-frequency signal level and current change very quickly, but the change cycle is short, the energy required is not very large, so the chip is powered by the decoupling capacitor closest to the chip. When C1 is large enough and the reaction is fast enough (with a very low ESR value), the orange path on the top layer and the red path on the GND layer can be regarded as non-existent (there is a current corresponding to the power supply of the entire board, but not the current corresponding to the signal in the figure).

Therefore, according to the environment constructed in the figure, the entire path of the current is: positive pole of C1 → VCC of IC1 → S1 → L2 signal line → R1 → GND of IC2 → via → yellow path of GND layer → via → negative pole of capacitor.

It can be seen that there is a brown equivalent current in the vertical direction of the current, and a magnetic field will be induced in the middle. At the same time, this ring surface can easily couple to external interference.

If the signal in the figure is a clock signal, and there is a set of 8-bit data lines in parallel, powered by the same power supply of the same chip, the current return path is the same.

If the data line level flips in the same direction at the same time, a large reverse current will be induced on the clock. If the clock line is not well matched, this crosstalk is enough to have a fatal impact on the clock signal. The intensity of this crosstalk is not proportional to the absolute value of the high and low levels of the interference source, but proportional to the current change rate of the interference source. For a purely resistive load, the crosstalk current is proportional to:

dI/dt=dV/(T¬10%-90%*R)

The dI/dt (current change rate), dV (swing amplitude of the interference source) and R (interference source load) in the formula all refer to the parameters of the interference source. If it is a capacitive load, dI/dt is inversely proportional to the square of T¬10%-90%.

From the formula, we can see that the crosstalk of low-frequency signals is not necessarily smaller than that of high-frequency signals. In other words, a 1KHz signal is not necessarily a low-speed signal. The edge situation should be considered comprehensively. For a signal with a very steep edge, it contains many harmonic components and has a large amplitude at each frequency multiple point.

Therefore, when selecting devices, you should also be careful not to blindly choose chips with fast switching speeds. This will not only increase the cost, but also increase crosstalk and EMC problems.

Any adjacent power layer or other plane can be used as the return plane of the signal as long as there is a suitable capacitor at both ends of the signal to provide a low-reactance path to GND. In ordinary applications, the IO power supply of the chip corresponding to the transmitter and receiver is often consistent, and there is generally a 0.01-0.1uF decoupling capacitor between each power supply and the ground, and these capacitors are just at both ends of the signal, so the return effect of the power plane is second only to the ground plane. If other power planes are used for return, there is often no low-reactance path to the ground at both ends of the signal. In this way, the current induced in the adjacent plane will find the nearest capacitor to return to the ground. If this "nearest capacitor" is far away from the starting end or the terminal, the return flow will also have to go through a "long journey" to form a complete return path, and this path is also the return path of the adjacent signal. The same return path has the same effect as the common ground interference, which is equivalent to the crosstalk between the signals.

For some unavoidable cross-power split situations, you can cross-connect capacitors or RC series high-pass filters (such as 10 ohm resistors in series with 680p capacitors, the specific value depends on the type of signal, that is, to provide a high-frequency return path and isolate the low-frequency crosstalk between the planes) at the cross-split. This may involve adding capacitors between power planes, which seems a bit funny, but it is definitely effective. If some specifications do not allow it, you can connect capacitors to the ground on both planes at the split.

In the case of using other planes for return current, it is best to add a few small capacitors to the ground at both ends of the signal to provide a return current path. However, this approach is often difficult to achieve because most of the surface space near the terminal is occupied by matching resistors and chip decoupling capacitors.

Return current noise is one of the main sources of noise on the reference plane, so it is necessary to study the path and flow range of the return current.

Return path theory

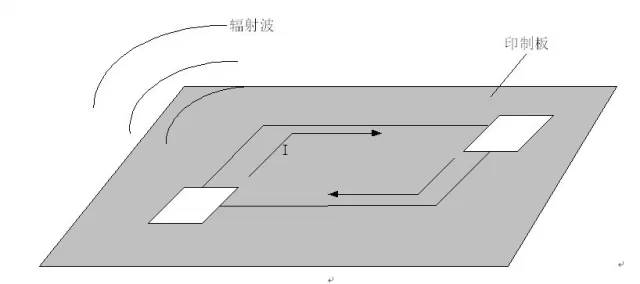

The following figure shows a line in a printed circuit board. Current flows through the wire. Usually, we only see the wires on the surface for transmitting signals, from the driver to the receiver. In fact, current can only flow in a loop. The transmission line is visible to us, but the path for the current to return is usually invisible. They

usually flow back through the ground plane and the power plane

. Since there is no physical line, the loop path becomes difficult to estimate and it is difficult to control them.

As shown in Figure 3.1, each wire and its loop on the PCB board constitute a current loop. According to the principle of electromagnetic radiation, when a sudden current flows through the wire loop in the circuit, an electromagnetic field will be generated in space and affect other wires. This is what we usually call radiation. In order to reduce the impact of radiation, we should first understand the basic principles of radiation and the parameters related to radiation intensity.

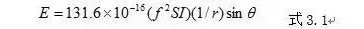

These loops are equivalent to small antennas in operation, radiating magnetic fields into space. We simulate this using the radiation generated by a small loop antenna. Suppose the current is I, the area of the small loop is S, and the electric field strength measured in the far field of free space r is:

From equation 3.2, we know that the radiation is proportional to the loop current and loop area, and proportional to the square of the current frequency.

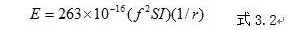

The return current path in a printed circuit board is closely related to the frequency of the current. According to basic circuit knowledge, DC or low-frequency current always flows in the direction with the least impedance; and high-frequency current always flows in the direction with the least inductive reactance when the resistance is constant.

If the influence of holes and grooves formed by vias on the copper plane is not considered, the path with the least impedance, that is, the path of low-frequency current, is composed of arc lines on the ground copper plane, as shown in Figure 3.2. The current density on each arc line is related to the resistivity of the arc line.

For the transmission line, the return path with the smallest inductive reactance, that is, the high-frequency current return path, is on the copper plane directly below the signal wiring, as shown in Figure 3.3. Such a return path minimizes the space area surrounded by the entire loop, which also minimizes the magnetic field intensity radiated into space by the loop antenna formed by this signal (or the ability to receive space radiation).

Formula 3.3

Formula 3.3

Figure 3.3 Transmission line return current density distribution

According to formula 3.3, Table 3.1 lists the percentage of return current flowing through the strip area with a width of centered on the center of the transmission line as a percentage of all return currents.

Assuming 0.035 inches, the current returning through the area beyond 0.035 inches from the transmission line only accounts for 13% of the total return current, and only 6.5% is distributed to one side of the transmission line, and the density is very small. Therefore, it can be ignored.

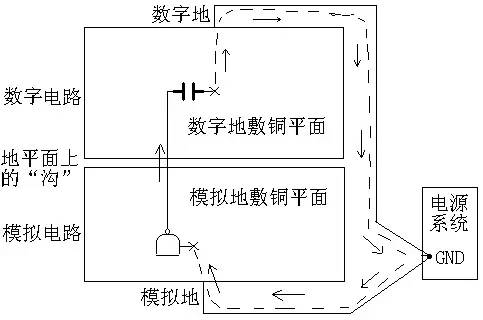

-

When there is a continuous, dense, and complete copper plane under the signal wiring, the noise interference of the signal return current on the copper plane is local. Therefore, as long as the principle of localized layout and wiring is followed, that is, the distance between digital signal lines, digital devices and analog signal lines, analog devices is artificially increased to a certain extent, the interference of digital signal return current on analog circuits can be greatly reduced.

-

High-frequency transient return current flows back to the driver through the plane (ground plane or power plane) adjacent to the signal trace. The terminal load of the driver signal trace is connected between the signal trace and the plane (ground plane or power plane) adjacent to the signal trace.

-

The larger the surrounding area of the power and ground lines on the printed circuit board, the greater their radiation energy. Therefore, by controlling the return path, we can minimize the surrounding area and thus control the degree of radiation.

Solutions to the reflux problem

There are usually three aspects that cause reflow problems on PCB boards:

chip interconnection, copper surface cutting, and via jumping

. These factors are analyzed in detail below.

4.1 Reflow Problems Caused by Chip Interconnection

When a digital circuit is working, a transition between high and low voltage will occur, which will cause a transient load current to flow from the power supply into the circuit or from the circuit into the ground.

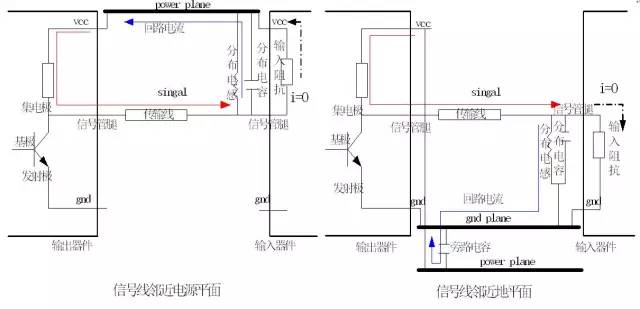

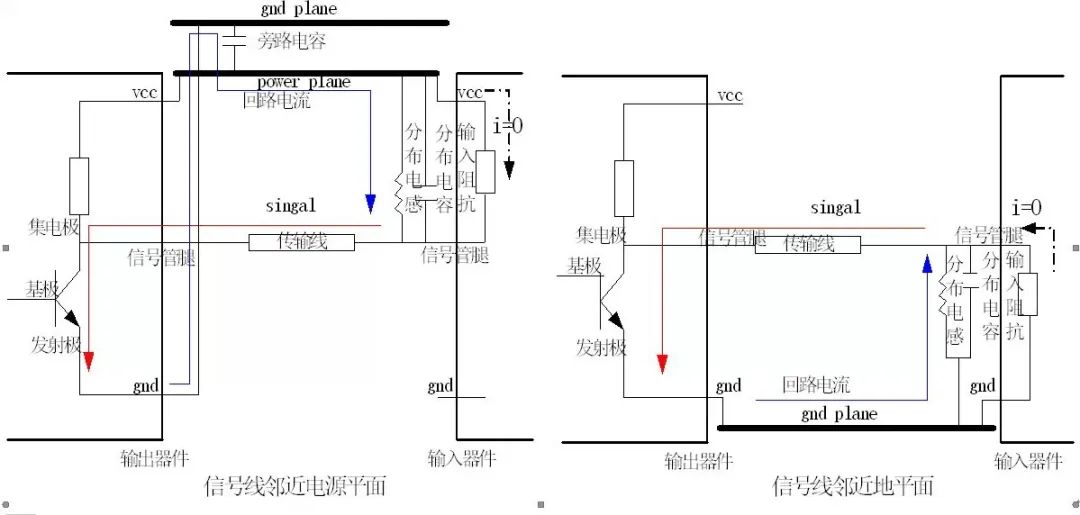

For digital devices, the input resistance of its pin can be considered infinite, which is equivalent to an open circuit (i.e., i=0 in the figure below). In fact, the loop current returns through the distributed capacitance and distributed inductance generated by the chip, power supply, and ground plane. The following analysis takes the collector output circuit as an example of the internal circuit of the output signal.

① The signal line is close to the power plane

The driver end charges the transmission line composed of the signal trace, the power plane and the terminal load. The current enters the device from the power pin of the driver and flows from the output end of the driver to the load end.

The high-frequency transient return current flows back to the output of the driver on the power plane under the signal trace. The return current directly passes through the power plane and enters the driver from the power pin of the driver, forming a current loop.

②Signal routing is close to the ground plane

The driver charges the transmission line composed of the signal trace, the power plane and the terminal load. The current enters the device from the power pin of the driver and flows from the output end of the driver to the load end.

4.1.2 The driver changes from high level to low level

This is equivalent to the output pin absorbing the current on the transmission line.

① The signal trace is close to the power plane

② The signal line is close to the ground plane

4.2 Solution to the reflow problem caused by copper clad cutting

4.3 Solution to the reflow problem caused by vias

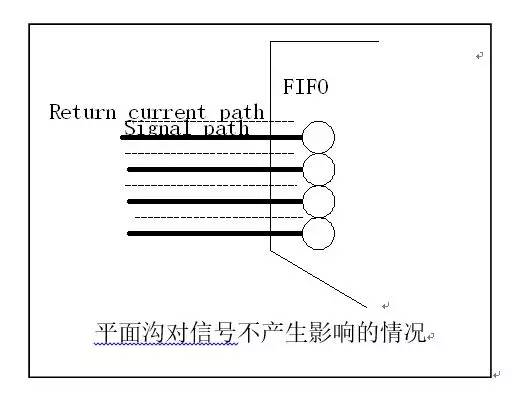

4.3.1 Grooves formed by vias

When routing signals on a printed circuit board, if it is a multi-layer board, many signals must be connected by changing layers. At this time, a large number of vias are used. If the vias are densely arranged on the power or ground plane, sometimes many vias will be connected together to form a so-called groove, as shown in the figure. First, we should analyze this situation to see if the return flow needs to pass through the groove. If the return flow of the signal does not need to pass through the groove, it will not hinder the return flow. If the loop circuit has to bypass this groove to return, the antenna effect formed will increase sharply, causing interference to the surrounding signals. Usually, after the coating data is generated, we can adjust the places where the vias are too dense and the grooves are formed, so that there is a certain distance between the vias.

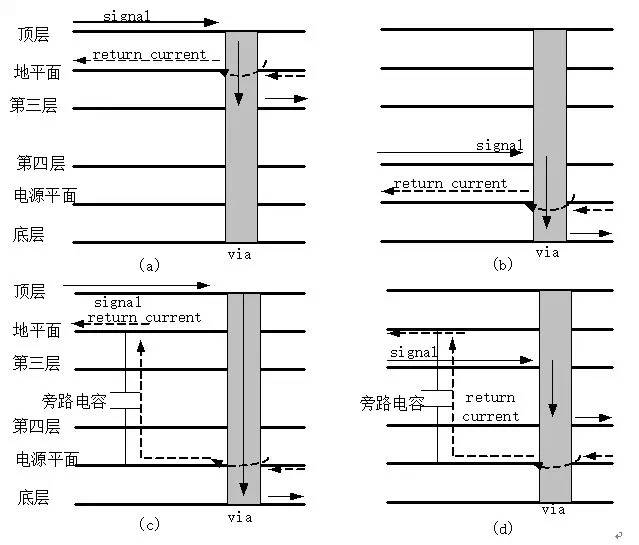

4.3.2 Layer skipping phenomenon caused by vias

Let's take a six-layer board as an example for analysis. The six-layer board has two coating layers, the second layer is the ground layer, and the fifth layer is the power layer. Therefore, the signal return of the surface layer and the third layer is mainly in the ground layer; the return of the bottom layer and the fourth layer is mainly in the power layer.

There are six possibilities when changing layer wiring:

-

Surface layer <-> third layer

-

Surface<->Fourth Layer

-

Surface<->Base

-

Third floor <-> Fourth floor

-

Third floor <-> bottom floor

-

Fourth floor<->bottom floor

These six possible situations can be divided into two categories according to the situation of their loop current: the situation where the loop current flows on the same layer and on different layers, that is, whether there is a layer skipping phenomenon.

① When loop current flows on the same layer

Including the surface layer <-> the third layer, the fourth layer <-> the bottom layer.

In this case, the loop current flows on the same layer. However, according to the principle of electrostatic induction, the internal electric field strength of a complete conductor in an electric field is zero, and all currents flow on the surface of the conductor. The ground plane and the power plane are actually such a conductor.

The vias we use are all through holes. The holes left when these vias pass through the power and ground planes provide a path for the current to flow through the upper and lower surfaces of the coating layer. Therefore, the return path of these signal lines is very good and no measures need to be taken to improve it.

②Circuit current flows on different layers

Including surface layer <-> fourth layer, surface layer <-> bottom layer, third layer <-> fourth layer, third layer <-> bottom layer.

The following takes the surface layer <-> bottom layer and the third layer <-> fourth layer as examples to analyze the reflux situation.

Signals with layer jumping phenomenon require some bypass capacitors to be added near the dense via area, usually 0.1uf magnetic chip capacitors, to provide a return path.

Disclaimer: This article is reprinted from the Internet, and the copyright belongs to the original author. If the videos, pictures, and texts used in this article involve copyright issues, please leave a message at the end of the article to let us know, and we will deal with it as soon as possible! The content of this article is the original author's point of view, and does not mean that this public account agrees with its point of view and is responsible for its authenticity.

Reply to any content you want to search in the official , such as problem keywords, technical terms, bug codes, etc., and you can easily get relevant professional technical content feedback . Go and try it!

Since the WeChat official account has recently changed its push rules, if you want to see our articles frequently, you can click "Like" or "Reading" at the bottom of the page after each reading, so that each pushed article will appear in your subscription list as soon as possible.

Or set our public account as a star. After entering the public account homepage, click the "three dots" in the upper right corner, click "Set as Star", and a yellow five-pointed star will appear next to our public account name (the operation is the same for Android and iOS users).

京公网安备 11010802033920号

京公网安备 11010802033920号