Introduction

There are many ways to obtain image sources in image processing systems, and there are also various sensors for the same image. The more popular sensors now include CCD, CMOS, CIS, etc. These sensors have different image data output formats. For example, CCD outputs analog signals, which require A/D sampling to obtain the digital image signals required for image processing; while CMOS sensors directly output digital signals. This will inevitably have a great impact on the versatility of the image processing system. When the image sensor is changed or the resolution of the image is changed, the image processing system will be modified accordingly, which greatly limits the application scope and versatility of the dedicated image processing board.

Since television technology has been widely popularized for a long time, in order to ensure the versatility of television, the world has already made unified regulations on the analog video signals that can be used. In Europe and China, analog video signals mainly adopt the PAL format; while in North America and Japan, analog video signals mainly adopt the NTSC format. It is precisely because of the unification of analog video signal formats that many technologically mature image acquisition devices, such as cameras, cameras, etc., have output interfaces for analog video signals.

This design plan aims to take advantage of the above-mentioned favorable conditions and propose an image acquisition solution based on the TMS320C6x11 series DSP. It uses the unity of analog video signals to realize the random replacement of image devices with standard analog video signal output interfaces without the need for image processing. Make modifications to the system's hardware and software. At the same time, this solution also needs to provide a relatively universal digital video interface that can adapt to the interface of the TMS320C6xll series DSP. The main technical requirements of this design are:

① Support standard analog video input interface, which can decode standard analog video signals to obtain digital image data;

② Without reducing the image format, the image acquisition speed is fast and meets a certain real-time performance. Requirements;

③ It takes up less CPU time, allowing the image acquisition process to be completed independently in the background;

④ The digital image interface has good versatility and can be universally interchanged on the TMS320C6u1l series of platforms.

1 Overall scheme design

1.1 Scheme selection

At present, the main methods of decoding analog video signals are: using A/D sampling analog video signals and using a dedicated analog video signal decoder. The former solution requires fewer external chips and only requires an A/D conversion chip; however, it requires a large amount of CPU time. During the image acquisition process, the CPU basically has no extra time to process the image. This problem often results in the image processing system running out of time to process the image. The latter solution uses a specialized analog video signal decoder, which requires some additional interface chips, but can save a lot of CPU time. The image acquisition process can be completed in the background, basically without CPU intervention. This advantage is very attractive to image processing systems, especially processing systems with relatively complex algorithms (such as video surveillance systems), so this plan decided to use the latter.

One of the difficulties in this solution is that the amount of data in the digital video signal decoded from the analog video signal is very large, and since it is a real-time video signal, the data output rate is also very high; but on the contrary, the readout rate of the DSP external memory interface is slower. In order to solve this problem, this solution adopts two buffering methods. The first is to use high-speed FIFO to temporarily buffer data to alleviate the speed difference, but such buffering is not enough to balance the speed difference between the two.

Therefore, the idea of "interlaced sampling" was proposed in this plan. Usually, interlaced sampling will reduce the resolution. For example, sampling one line of data every four lines will reduce the number of lines in the vertical direction of the image to 1/4 of the original. This is not what the design wants, so in order to ensure the resolution of the image, the design interleaves the line data of the entire image into multiple samples while sampling interlaced lines, and then recombines it into a complete image. This not only plays the role of buffering speed difference, but also ensures the resolution of the image.

The final idea of this solution is to use FIFO to temporarily store a row of image data, and the video decoder directly writes the image data to FIF0. When valid image data is written into the FIFO, the CPLD issues an interrupt request to the DSP; at the same time, after receiving the interrupt request, the DSP starts the DMA mode to read a line of image data from the FIFO into its external RAM for storage. CPLD mainly completes the implementation of "interlaced sampling", controls the decoder to write data to the FIFO, and the DSF to read data from the FIFO.

In addition, this solution is currently mainly aimed at PAL standard analog signals. The size of the image transmitted by the PAL analog signal is 720×576 pixels. The following design is mainly developed for the video signal of this format. If you need to decode NSTC and other video signals, you only need to make some modifications to the software.

1.2 System block diagram

In this solution, the analog video signal decoder uses Philips' SAA7111A. For the PAL standard analog video signal, one line of image data has 720 pixels; at the same time, because the YUV component uses 4:2:2 sampling, 1440 bytes of storage space is required to store one line of data. Since FIFO is needed to temporarily store 1 row of data in this solution, the storage depth of FIFO must be greater than 1440 bytes. Finally, the high-speed FIFO selected is IDT72V23l from IDT, which has a storage depth of 2K×9 bits. At the same time, Laittice's CPLD-LC4128V is also used as an intermediate logic interface to control the completion of "interlaced sampling", the decoder's writing operation to the FIFO, and the DSP's reading operation to the FIFO. The system block diagram is shown in Figure 1.

2 硬件方案设计

2.1 芯片介绍

本方案选用SAA7111A作为前端视频解码器。SAA71llA视频解码器是双通道模拟预处理电路、自动钳位和增益控制电路、时钟产生电路、数字多标准解码器、亮度/对比度/饱和度控制电路、彩色空间矩阵的组合,是一款功能完善的视频处理器。SAA711lA只需要单一的3.3V电源供电,与C6x11的I/O电压一致。SAA7111A接收CVBS(复合视频)或S-video模拟视频输入,可以将PAL、SECAM、NTSC模式的彩色视频信号解码为CCIR-60l/656兼容的彩色数字分量值,器件功能通过I2C接口控制。

SAA7111A的主要性能特点如下:

◆4路模拟输入一一4路CVBS或2路Y/C或1路Y/C和2路CVBS;

◆主通道静态增益可编程,自动增益控制选择的CVBS或Y/C通道;

◆2个8位视频CMOS模数转换器;

◆片上时钟产生器,只需要24.576 MHz单一时钟输入;

◆自动探测50 Hz和60 Hz场频,自动在PAL和NTSC标准间切换;

◆可以处理PALBGHI、PALN、PAL M、NTSC M、NTSC N、NTSC 4.43、NTSC-Japan和SECAM信号。从以上特点可以看出,SAA7111A功能强大,性能全面,可以满足各种视频转换处理的需要,完全符合本系统的要求。SAA7111A已经在各种视频处理系统中得到广泛的应用,技术性能已得到充分的证明。采用SAA7111A具有很高的性价比。

2.2 DSP与FOFO接口技术

TMS320C6xll的外部存储器接口(EMIF)提供了功能十分强大的外部接口,可以实现与诸多种类的存储器的无缝接口,如SBSRAM、SDRAM、SRAM、ROM等等。但是其对FIFO的接口并不能做到真正的无缝接口,需要增加一些外部逻辑来调整它们之间的时序。

本方案中采用的FIFO一一IDT72V23,是标准的同步FIFO,具有两个独立的读写时钟——RCLK、WCLK;同时还具有读写控制信号WENl、WEN2、REN1和REN2。

对于本设计而言,要求DSP从FIFO中将数据读出,故关键考虑DSP对IDT72V23l的读时序。图2是IDT72V31数据读出的时序。

图2中,tENS为REN1(REN2)的最短建立时间(SETUP),tDS为数据的最短建立时间(SETUP)。由图2可以看出IDT72V231与一般SRAM读时序的一个很大区别是:当RCLK上升沿到来以后,需要有一个比较长的延时tA才会有有效数据出现在总线上。此前一段时间内总线上的数据是不稳定的,并且该延时最长可达到12ns。

但是对于TMS320C6x11而言,数据的读入是在ARE信号的上升沿完成的,故这里设计的主要问題是FIFO的RCLK时钟怎样提供。本设计中采用的解决办法如下:

RCLK=!(ARE)

REN1&REN2=CEx+AOE+Address

也就是说,RCLK是由DSP的ARE信号取反得到的,而REN1和REN2信号是由DSP的AOE信号经过地址译码后提供。这样设计的TMS320C6xll与FIFO接口为了配合FIFO读出时序的要求,还必须要求DSP的读时序(主要是Setup/Strobe/Hold三个时序段)满足以下要求:

Setup≥(tENS+tSKEW)/tcyc

Strobe≥(tA+tDS)/tcyc

Strobe≥(tCLKH(min)/tcyc

Hold+Setup≥(tCLKL(min)/tcyc

Setup+Strobe+Setup≥(trc(min)/tcyc

从时序图上的数据可以看出,tENS≥5ns,tA≤12 ns,tDS≥5 ns;同时,由于IDT72V23l的要求,RCLK高电平时间(tCLKH(min)大于等于8ns、RCLK低电平时间(tCLKL(min)大于等于8 ns以及读写周期(trc(min)必须大于等于20ns。加上一定的冗余,最后计算可以得到:

Setup≥20ns

Strobe≥30 ns

Hold≥l0ns

在本设计的TMS320C6211的系统板上,EMIF的外部时钟频率是100 MHz,所以tcyc=10ns。这样可以得出DSP中CExCTL寄存器中Setup值设置为2,Strobe值设置为3,Hold值设置为1。

实际系统实现证明。通过这样的硬件接口设计后,TMS320C621l可以很稳定地从FIF0中读出数据。

2.3 隔行采样技术

由于DSP接口与FIFO的接口速度只能达到15MB/s的速度,同时当DSP把图像数据从FIFO中读出来以后还需要将数据存入其外部存储器中,这样DSP与FIFO的接口速度是完全不可能跟上解码器SAA7111A的有效数据输出速度(最低19.8 MB/s)的,所以DSP无法实时地从视频流中抓出一幅完整的图像。 因此,在DSP与SAA711lA的接口之间采用高速FIFO进行缓冲的同时,还采取了“隔行采样”的方法来缓冲速度上的差异。通过计算得出DSP每隔4行有效视频信号采1行视频数据是合理的。(把DSP将获取的数据存人其外部存储器中所需要的时间考虑在内。)

“隔行采样”的结果会导致所获取的图像垂直分辨率下降(对于PAL制式视频信号由原来的576行/幅下降到144行/幅)。为了保证图像的分辨率,本设计中将每幅图像分成连续的4次采样.在连续的4次采样中,分别抓取图像中不同的144行数据,也就是说,现在DSP抓取1幅完整幅面(720×576)大小的图像需要分4次获取,然后对数据重排组合得到完整的图像。PAL制信号是按照50Hz的场频对图像进行输出的,即每秒种可以传输25幅图像,现在由于“隔行采样”的原因,DSP每秒钟可以从PAL制信号中解码出6.25幅完整幅面大小的图像。这个速度完全可以满足很多实时系统的要求,如视频监控系统。

“隔行采样”功能的具体实现是由CPLD配合SAA7111A输出的同步信号(行同步、场同步信号)来完成的。由于IDT72V231(FIFO)的写入控制是通过WEN信号完成的,因此CPLD可以通过控制WEN信号来实现图像的隔四行一采样。具体WEN信号的产生逻辑如图3所示。

It can be clearly seen from Figure 3 that after this sampling method, the image rows output each time are 1 rows every 4 rows, while the images obtained 4 consecutive times are the same 576 rows of image data in the entire image. With the same 144 lines of data, these four parts of the image can be combined according to certain rules to obtain a complete digital image with a format of 720×576 pixels.

In addition, it can be seen from Figure 3 that every time SAA7111A writes one line of image data to the FIFO (requiring 53.3μs), the DSP has the time equivalent to 4 lines of image data output (about 256μs) to read out this line of image data. Therefore, "interlaced sampling" effectively buffers the difference in data output and data reading speeds.

3 Software solution design

The design of the decoder DSP software is mainly divided into two parts: ① Read the image data from the FIFO and store it in the external RAM of the DSP; ② Rearrange the read data and combine it into a complete image. The following is divided into two parts to explain.

3.1 QDMA mode data reading

Since DSP reading data from the outside into RAM is usually an image acquisition process of the image processing system, it is obviously unreasonable to keep the CPU in the operation of reading data.

In order to ensure that the CPU time is occupied as little as possible, that is, while the nth image is read into RAM, the DSP can still have enough time to process the n-1th image (do the required processing on it, such as denoising , compression, recognition, etc.). The following readout method is adopted in this design: the video decoder notifies the DSP through an interrupt signal that data has been written to the FIFO, and then the DSP uses the DMA method in the interrupt to move the data in blocks from the FIFO to Go to RAM.

The benefits of this operation are obvious: when the DSP is processing a certain frame of image, if there is data that needs to be read in, the DSP will enter the interrupt, and then only need to start the DMA read operation to exit the interrupt service program and continue There is no finished work; the DMA controller reads a continuous area of image data into RAM in the background. In this way, image acquisition can be completed in the background, and image processing and image acquisition can be performed in parallel, greatly improving CPU utilization.

Specifically, in this solution, since the depth of the FIFO used is 2 K × 9 bits, DMA is used to move one line of image data (that is, 720 × 2 = 1440 bytes) to RAM at a time. At the same time, TMS320C6x11 provides very powerful EDMA functions. In order to speed up the DSP to start the DMA read operation in the interrupt, this design uses its QDMA function. In this way, applying for QDMA only requires a few instructions. The specific operation code to apply for QDMA is as follows:

QSRC=SourceAddress,

//Set the FIFO address in the system

QCNT=0x000005A0;

//Set the amount of data to be read at a time

//(1440)

QDST=(int)DesAddress; //Set Data read destination address

QIDX=0x00000001; //Set QDMA transmission distance

DesAddress=DesAddress+0x5A0;

//Update data read destination address

QSOPT=0x30300000; //Start QDMA channel transmission

3.2 Image data rearrangement

due to this solution The method of sampling every four lines is used to balance the difference in speed, so the data in the manned RAM needs to be rearranged in the end. This rearrangement can be performed when the data in the FIFO is read, or it can be rearranged after all the data is read into the RAM; but the rearrangement plan and process are the same.

If all the data is read and then rearranged, the image data is stored in four consecutive data blocks due to sampling every four rows, and each data block is distributed according to odd and even fields. So, taking the first data block as an example, its odd field part actually stores the 1st, 9th, 17th,..., 561, 569th row data of the image; and its even field part actually stores the image's data Lines 2, 10, 18,…, 562, 570 of data. In addition, the number of rows of the image data stored in the three data blocks in the entire image is distributed in the same way. The specific distribution and rearrangement process is shown in Figure 4.

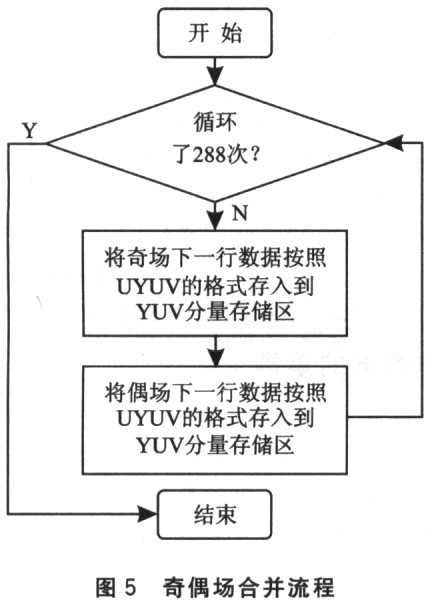

After rearrangement processing as shown in Figure 4, all image data is divided into two large blocks: odd field area and even field area. At this time, you can treat these two areas as needed. What is used in this design is to merge the odd and even fields and separate the YUV components into three independent storage areas. The program flow is shown in Figure 5.

4 Summary and Outlook

This article proposes an image acquisition solution based on the TMS320C6xll interface. It takes advantage of the fact that most mature image acquisition devices are equipped with universal analog video output interfaces, and proposes a solution to capture still digital images from analog encoded video signals. Because its digital part interface is very versatile (8-bit), it is easy to add a real-time image acquisition interface to a general image processing system. The specific implementation proves that this solution is feasible, stable and efficient; it can achieve the acquisition of 6.25 720×576 color images per second, and has the characteristics of good versatility, stable performance and less CPU time. The anti-collision module responds correctly to SELECT commands.

Conclusion

Type A card RFID technology has been widely used in smart cards, ticket items, security inspection, logistics and anti-counterfeiting. According to the RFID anti-collision protocol, this article implements the anti-collision module of type A card on digital hardware. After simulation and synthesis using VHDL language, it passed the XC4010XLFPGA verification of Xilinx Company. The circuit scale is about 5,000 gates, meeting the predetermined indicator requirements. . Finally, the O.35μm process was used for MPW tape-out together with other modules of the electronic anti-counterfeiting label. Practical application tests proved that the module operates correctly and stably.

Previous article:Interface design between TMS320C5402 and MAX147

Next article:Using DSP technology to obtain digital images from analog video signals

- Popular Resources

- Popular amplifiers

-

Point Cloud Registration from Beginner to Master (Guo Hao)

Point Cloud Registration from Beginner to Master (Guo Hao) -

A review of learning-based camera and lidar simulation methods for autonomous driving systems

A review of learning-based camera and lidar simulation methods for autonomous driving systems -

Semantic Segmentation for Autonomous Driving: Model Evaluation, Dataset Generation, Viewpoint Comparison, and Real-time Performance

Semantic Segmentation for Autonomous Driving: Model Evaluation, Dataset Generation, Viewpoint Comparison, and Real-time Performance -

Basics of Machine Learning: From Getting Started to Job Hunting (Hu Huanwu)

Basics of Machine Learning: From Getting Started to Job Hunting (Hu Huanwu)

- Huawei's Strategic Department Director Gai Gang: The cumulative installed base of open source Euler operating system exceeds 10 million sets

- Analysis of the application of several common contact parts in high-voltage connectors of new energy vehicles

- Wiring harness durability test and contact voltage drop test method

- Sn-doped CuO nanostructure-based ethanol gas sensor for real-time drunk driving detection in vehicles

- Design considerations for automotive battery wiring harness

- Do you know all the various motors commonly used in automotive electronics?

- What are the functions of the Internet of Vehicles? What are the uses and benefits of the Internet of Vehicles?

- Power Inverter - A critical safety system for electric vehicles

- Analysis of the information security mechanism of AUTOSAR, the automotive embedded software framework

Professor at Beihang University, dedicated to promoting microcontrollers and embedded systems for over 20 years.

Professor at Beihang University, dedicated to promoting microcontrollers and embedded systems for over 20 years.

- Innolux's intelligent steer-by-wire solution makes cars smarter and safer

- 8051 MCU - Parity Check

- How to efficiently balance the sensitivity of tactile sensing interfaces

- What should I do if the servo motor shakes? What causes the servo motor to shake quickly?

- 【Brushless Motor】Analysis of three-phase BLDC motor and sharing of two popular development boards

- Midea Industrial Technology's subsidiaries Clou Electronics and Hekang New Energy jointly appeared at the Munich Battery Energy Storage Exhibition and Solar Energy Exhibition

- Guoxin Sichen | Application of ferroelectric memory PB85RS2MC in power battery management, with a capacity of 2M

- Analysis of common faults of frequency converter

- In a head-on competition with Qualcomm, what kind of cockpit products has Intel come up with?

- Dalian Rongke's all-vanadium liquid flow battery energy storage equipment industrialization project has entered the sprint stage before production

- Allegro MicroSystems Introduces Advanced Magnetic and Inductive Position Sensing Solutions at Electronica 2024

- Car key in the left hand, liveness detection radar in the right hand, UWB is imperative for cars!

- After a decade of rapid development, domestic CIS has entered the market

- Aegis Dagger Battery + Thor EM-i Super Hybrid, Geely New Energy has thrown out two "king bombs"

- A brief discussion on functional safety - fault, error, and failure

- In the smart car 2.0 cycle, these core industry chains are facing major opportunities!

- The United States and Japan are developing new batteries. CATL faces challenges? How should China's new energy battery industry respond?

- Murata launches high-precision 6-axis inertial sensor for automobiles

- Ford patents pre-charge alarm to help save costs and respond to emergencies

- New real-time microcontroller system from Texas Instruments enables smarter processing in automotive and industrial applications

- 51 delay problem

- Get a gift for your evaluation! Hands-on experience: Recruiting TI millimeter-wave radar testers from all over the Internet

- How does Allegro's built-in package library identify which type of device it belongs to?

- STM8 Little Frog: Return to the Arena

- What are some good ways to transform various periodic waveforms into square waves that can be recognized by microcontrollers?

- General Design Considerations for Embedded Systems

- CH340 circuit improves working stability and anti-interference

- Schematic diagram of numworks

- What are the similarities and differences between the IO port simulation serial port, PWM, IIC functions and the serial port, PWM, IIC built into the chip hardware?

- 【Multi-function open source custom macro keyboard】OLED display test

Point Cloud Registration from Beginner to Master (Guo Hao)

Point Cloud Registration from Beginner to Master (Guo Hao)

京公网安备 11010802033920号

京公网安备 11010802033920号