Introduction

There are many options for network camera solutions, but mainstream products in the market generally choose two solutions: (1) Using CPU+ASIC. (2) Adopt dual CPU structure, that is, an embedded CPU and a dedicated signal processing chip DSP. Limited by the processing capabilities of the dedicated DSP chip, the video processing algorithms used in existing embedded network cameras are basically standards below H.263.

This article introduces a network camera design solution based on TMS320DM642 DSP. Its operating system , communication protocol, network protocol, and audio and video processing software are all implemented on a TMS320DM642, which reduces the difficulty of development.

Figure 1 Network camera hardware schematic diagram

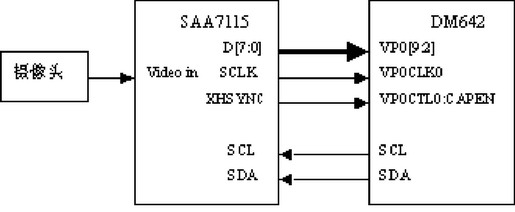

Figure 2 Video interface schematic diagram

Figure 3 Network interface schematic diagram

Introduction to TMS320DM642 chip

TI's TMS320DM642 (hereinafter referred to as DM642) is a dedicated DSP specifically designed for multimedia applications. The DSP has a clock of up to 600MHz, 8 parallel computing units, and a processing capacity of 4800MIPS. It adopts a secondary cache structure and has a 64-bit external memory interface. It is compatible with IEEE-1149.1 (JTAG) boundary scan. In order to be oriented to multimedia applications, it also integrates 3 Configurable video port, McASP (Multi Channel Audio Serial Port) for audio applications, 10/100Mb/s Ethernet MAC and other peripherals. In view of the above advantages of DM642, this network camera system uses DM642 as the core to complete the real-time collection, compression and transmission functions of audio and video signals.

The circuit composition of the hardware design

system is shown in Figure 1. The video signal input from the camera and the audio signal input from the microphone are collected, A/D converted into digital signals and then sent to the DSP. DSP compresses, codes and combines audio and video signals at the source, and then transmits the data to the video monitoring center through the LAN or the Internet. The monitoring center can monitor multiple sites at the same time, receive or send alarm signals, and control the pan/tilt in real time through the asynchronous serial bus RS-485 as needed to adjust the direction and position of the camera.

Video capture circuit

The video decoding chip used in this system is SAA7115 from Philips Company. After the full TV signal input from the analog video input port undergoes clamping, anti-aliasing filtering, A/D conversion, and YUV separation circuits inside the SAA7115, it is converted into a BT.656 video data stream in the YUV to YCrCb conversion circuit, and then input into the compression core unit DM642. The three video ports VP0, VP1, and VP2 of DM642 are connected to the video codec chip.

In this system, there is only one video input, so the VP1 and VP2 ports are unused, and the VP0 channel is configured as an 8-bit BT.656 video input port. The horizontal/field synchronization signal of video data is included in the EAV (end of active video) and SAV (start of active video) time base signals of the BT.656 digital video data stream. The video port only needs the video sampling clock and sampling enable signal. That’s it. The configuration of SAA7115 internal register parameters and the reading of status are performed through the I2C bus. The principle of the video interface is shown in Figure 2.

Audio input/output circuit

This system uses TI's high-performance stereo codec TLV320AIC23 (hereinafter referred to as AIC23) to realize the collection and playback of audio signals. AIC23 is compatible with the I/O voltage of DM642 and can achieve seamless connection with the McASP interface of DM642.

In this system, AIC23 works in main mode, and the sampling word width of the left and right channels is 16 bits. The data interface is in DSP mode. Set the working parameters and feedback status information of the internal register through the I2C bus.

Due to the inherent characteristics of network transmission, the audio data and video data cannot be uniform from the network camera to the monitoring center. If the network camera does not perform any correction processing, it will be difficult to ensure the synchronous output of audio and video. In order to achieve audio and video sampling synchronization, this article uses phase-locked loop PLL1708 to output a 27MHz clock from the LLC pin of SAA7115, and generates the main clock MCLK of AIC23 through PLL1708. Since the audio and video sampling signals use the same clock source, there will be no problem of audio and video being out of sync. The SCKO3 pin of PLL1708 outputs a default clock frequency of 18.433MHz, which is used as the input main clock MCLK of AIC23. The clock used internally in AIC23 can be obtained by dividing the main clock MCLK by setting the register.

Ethernet interface circuit

This system uses LXT971 as the Fast Ethernet physical layer adaptive transceiver. Since LXT971 supports IEEE 802.3 standard, provides MII (media independent interface) interface, and can support MAC, and DM642 has an Ethernet media access controller integrated inside, so LXT971 can achieve seamless connection with DM642. The connection circuit is shown in Figure 3, in which BH1102 is a 1:1 isolation transformer. The data transmitted from DM642 is converted into data that can be received by the Ethernet physical layer through LXT971, and then transmitted to the Internet through the RJ-45 header.

memory expansion circuit

DM642 has a 16KB first-level program cache, a 16KB first-level data cache and a 256KB shared second-level cache for program data. But this is not enough for direct processing of image data, so two 32MB SDRAMs are expanded to store original image data, and 4 MB FLASH is used to store applications. Both are mapped to the DM642's external data space.

CPLD circuit

The CPLD used in this system is Xilinx's XC9572XL. The chip has 72 macrocells, 1600 logic gates; 5ns pin-to-pin logic delay; 178MHz system frequency. The main functions of CPLD are: address decoding for FLASH, UART and CPLD asynchronous register space; generating 3-bit page selection signal for FLASH; monitoring the level interrupt signal from UART, converting it into an edge-triggered interrupt signal and sending it to the DSP.

RS-485 interface circuit

This interface is connected to the camera's PTZ and is used to control the rotation of the PTZ and adjust the direction and position of the camera. The RS-485 bus has strong anti-interference ability and can realize multi-site long-distance communication. This compression card plans to use UART chip SC16C550 and MAX487E of MAXIM Company to realize the transmission of RS-485 signals. The main function of SC16C550 is to convert the parallel signals transmitted by the DSP into serial signals. The receiver and transmitter inside the SC16C550 each have a 16B FIFO and can handle serial signals at a rate up to 3Mbps. MAX487E is an RS-485 bus interface chip that can work in full-duplex and half-duplex modes. The transmission rate can reach 2.5Mbps.

power circuit

The entire compression card is powered by a 5V DC transformer. This 5V voltage regulator generates 1.4V and 3.3V voltages to power the DSP core and I/O ports respectively, and generates another 3.3V to power video codecs and other chips. Note that the two 3.3V power supplies should be designed separately to prevent power supply noise from interfering with each other.

Since DSP requires two voltages, the coordination of the power supply system must be considered. During the power-on process, the core power supply should be powered on first, and at the latest it should be powered on together with the I/O power supply. When turning off the power, turn off the core power first and then turn off the I/O power. The reason for paying attention to the power supply sequence is that if only the CPU core is powered and the peripheral I/O is not powered, there will be no damage to the chip, but there will be no input/output capability. If, in turn, the peripheral I/O is powered but the CPU core is not, the transistors in the buffer/driver part of the chip will operate in an unknown state, which is very dangerous.

In order to solve this problem, this article uses the switching power supply chip TPS54310PWP to connect the power output valid pin PG (power good) of the 1.4V module to the allowed voltage input pin EN of the 3.3V module. In this way, only when the 1.4V voltage is valid, the 3.3V voltage starts to be powered on, which ensures that the core voltage of DM642 is powered on before the I/O voltage.

software design

In this system, image compression adopts H.264 standard. H.264 has high coding efficiency and can save about 50% of the code rate than H.263 under the same reconstructed image quality. H.264's code stream structure has strong network adaptability, increases error recovery capabilities, and can well adapt to IP and wireless network applications. Audio codec uses G.729 algorithm. Network transmission adopts RTP/RTCP protocol and multicast mode, which can ensure the quality of transmission. In terms of operating system, TI Reference Architecture 5 (RF5) based on DSP/BIOS is adopted. The application modules based on the RF5 operating system mainly include: audio and video collection module, compression encoding module, UART control module and network transmission module.

Conclusion

This solution can realize almost all functions of the network camera on a DM642 chip, and can perform real-time encoding and decoding of audio and video and real-time network transmission. With high image quality, low development difficulty and easy upgrade, it is an ideal network camera solution and can be widely used in video surveillance systems.

Previous article:Seagate wades into mobile storage, local partners may become rivals

Next article:Network camera design based on TMS320DM642

Recommended ReadingLatest update time:2024-11-17 05:37

- Popular Resources

- Popular amplifiers

-

A review of learning-based camera and lidar simulation methods for autonomous driving systems

A review of learning-based camera and lidar simulation methods for autonomous driving systems -

Semantic Segmentation for Autonomous Driving: Model Evaluation, Dataset Generation, Viewpoint Comparison, and Real-time Performance

Semantic Segmentation for Autonomous Driving: Model Evaluation, Dataset Generation, Viewpoint Comparison, and Real-time Performance -

Digilent Vivado library

Digilent Vivado library -

Machine Learning and Embedded Computing in Advanced Driver Assistance Systems (ADAS)

Machine Learning and Embedded Computing in Advanced Driver Assistance Systems (ADAS)

- Huawei's Strategic Department Director Gai Gang: The cumulative installed base of open source Euler operating system exceeds 10 million sets

- Analysis of the application of several common contact parts in high-voltage connectors of new energy vehicles

- Wiring harness durability test and contact voltage drop test method

- Sn-doped CuO nanostructure-based ethanol gas sensor for real-time drunk driving detection in vehicles

- Design considerations for automotive battery wiring harness

- Do you know all the various motors commonly used in automotive electronics?

- What are the functions of the Internet of Vehicles? What are the uses and benefits of the Internet of Vehicles?

- Power Inverter - A critical safety system for electric vehicles

- Analysis of the information security mechanism of AUTOSAR, the automotive embedded software framework

Professor at Beihang University, dedicated to promoting microcontrollers and embedded systems for over 20 years.

Professor at Beihang University, dedicated to promoting microcontrollers and embedded systems for over 20 years.

- Innolux's intelligent steer-by-wire solution makes cars smarter and safer

- 8051 MCU - Parity Check

- How to efficiently balance the sensitivity of tactile sensing interfaces

- What should I do if the servo motor shakes? What causes the servo motor to shake quickly?

- 【Brushless Motor】Analysis of three-phase BLDC motor and sharing of two popular development boards

- Midea Industrial Technology's subsidiaries Clou Electronics and Hekang New Energy jointly appeared at the Munich Battery Energy Storage Exhibition and Solar Energy Exhibition

- Guoxin Sichen | Application of ferroelectric memory PB85RS2MC in power battery management, with a capacity of 2M

- Analysis of common faults of frequency converter

- In a head-on competition with Qualcomm, what kind of cockpit products has Intel come up with?

- Dalian Rongke's all-vanadium liquid flow battery energy storage equipment industrialization project has entered the sprint stage before production

- Allegro MicroSystems Introduces Advanced Magnetic and Inductive Position Sensing Solutions at Electronica 2024

- Car key in the left hand, liveness detection radar in the right hand, UWB is imperative for cars!

- After a decade of rapid development, domestic CIS has entered the market

- Aegis Dagger Battery + Thor EM-i Super Hybrid, Geely New Energy has thrown out two "king bombs"

- A brief discussion on functional safety - fault, error, and failure

- In the smart car 2.0 cycle, these core industry chains are facing major opportunities!

- Rambus Launches Industry's First HBM 4 Controller IP: What Are the Technical Details Behind It?

- The United States and Japan are developing new batteries. CATL faces challenges? How should China's new energy battery industry respond?

- Murata launches high-precision 6-axis inertial sensor for automobiles

- Ford patents pre-charge alarm to help save costs and respond to emergencies

- How GaN helps cable providers find the balance

- TI DaVinci Technology

- Award-winning review: Mir Allwinner automotive-grade CPU development board MYC-YT507

- [Evaluation of Anxinke Bluetooth Development Board PB-02-Kit] A/D data acquisition and testing

- MSP430 and ATK-NEO-6M GPS module

- LCD Double Buffering Implementation on S3C2410 Bare Metal

- Electromagnetic compatibility principles and design

- EEWORLD University Hall----Electronic Measurement and Intelligent Instruments (Zhejiang University)

- Controllable non-motor vehicle direction indicator based on LED dot matrix screen

- Crazy Shell AI open source drone SPI (2.4G dual-machine communication)

A review of learning-based camera and lidar simulation methods for autonomous driving systems

A review of learning-based camera and lidar simulation methods for autonomous driving systems Digilent Vivado library

Digilent Vivado library

京公网安备 11010802033920号

京公网安备 11010802033920号