The airborne data bus ARINC429 is widely used in contemporary transport aircraft and a considerable number of civil aviation passenger aircraft (such as A310, A300, A600, B757, B767). At present, the design of ARINC429 bus interface boards in China is generally based on the HS3282 chip of HARRIS Company. Its shortcomings are limited number of channels and very inflexible. Therefore, the development of ARINC429 bus interface board to realize the reception and transmission of multi-channel ARINC429 bus data has become the focus of current research on aircraft airborne bus interface, and has very important practical significance and application prospects.

1 Introduction to ARINC429 bus

On modern civil aircraft, a large amount of information needs to be transmitted between systems and between systems and components. The ARINC specification is an air transportation industry standard developed for the transmission of digital data information between avionics equipment.

The ARINC429 (hereinafter referred to as 429) bus uses twisted-pair shielded wires to transmit information, and is transmitted in reverse phase through a pair of twisted-pair wires, which has strong anti-interference ability. The modulation method adopts the three-state code method of the bipolar return-to-zero system, that is, the three-level state modulation in which the information is composed of "high", "zero" and "low" states. The signal on the 429 cable and the signal after level conversion are shown in Figure 1. Each word of the 429 bus is 32 bits, and its word synchronization is based on a time interval of at least 4 bits in the transmission cycle, that is, a 4-bit code word.

Figure 1 429 signal and waveform after level conversion

2 Overall System Plan

The main function of the 429 bus interface board is to act as a bridge between 429 signals and related peripherals. It can receive bipolar return-to-zero 429 signals and convert them into digital signals and send them to computers or other devices. equipment, and can convert digital signals sent by computers or other equipment into 429 signal output. The bus interface board introduced in this article uses FPGA and DSP to implement four 429 signal receiving channels and four 429 signal sending channels, and each channel is independent of each other. In this interface board, the time interval between every two data words is adjustable. Each transceiver channel can independently define the word interval length. The check mode of each channel can be independently defined as odd check or even check. Data transmission You can choose single frame transmission or automatic repeated transmission (repeated transmission of a certain frame).

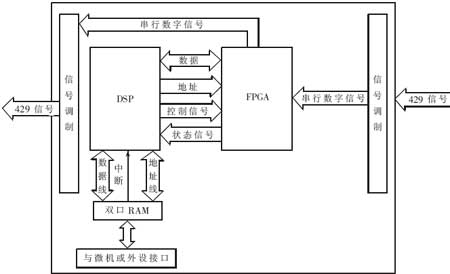

The entire interface board consists of modulation circuit, demodulation circuit, FPGA, DSP and dual-port RAM, as shown in Figure 2.

Figure 2 Interface board hardware structure diagram

3 Hardware circuit design

3.1 Modulation and demodulation circuit design

After the 429 signal enters the interface board, the 429 signal must first be converted into a TTL level that can be recognized by the digital circuit. Here, HOLT's HI-8482 is used to demodulate the signal and convert the standard 429 bus signal into a 5V TTL digital signal. In order to reduce interference, 39pF high-precision military capacitors are connected to the four input pins of the 429 bus signal respectively; HOLT's HI-8585 chip is used to achieve signal modulation and convert TTL digital levels into standard 429 signals.

3.2 FPGA internal logic design

According to the encoding format, characteristics, transmission rules and protocol requirements of the 429 signal, an ACEX1K FPGA from ALTERA Company is selected to send and receive four channels of data. Each channel is divided into a receiving part and a sending part.

The main function of the receiving part is to convert serial data into 32-bit parallel data through serial/parallel conversion, and to automatically implement error control on the received data. Errors such as word interval and bit interval errors can be automatically detected. If there are no errors, the data will be sent to the 16-bit data bus of the DSP twice for reading. The structural block diagram of the receiving module is shown in Figure 3.

Figure 3 Structural diagram of receiving module

The main function of the sending part is to temporarily store the data sent by the DSP in the FIFO inside the FPGA, waiting for the sending command. Once the send control command is received, the FIFO outputs the data and converts the parallel data into serial data through parallel/serial conversion, while adding a preset interval. The user can select the transmission mode (i.e. single frame transmission or automatic repeated transmission), transmission channel delay setting, transmission channel word interval setting by writing the control register, and can also check its working status by reading the status bit (the transmission buffer is empty , the send buffer is full and whether it is sending). The structural block diagram of the sending module is shown in Figure 4.

Figure 4 Structural diagram of sending module

The above introduction is only one sending channel and one receiving channel. Since this system has four independent sending channels and four independent receiving channels, four receiving modules and four sending modules need to be set up in the FPGA. Through the DSP address line to select one of the sending channels or receiving channels.

The internal structure of FPGA is based on SRAM, so a configuration chip is needed to solidify the internal logic. In order to facilitate debugging, two configuration modes, JTAG mode and passive serial mode (PS), are used. During debugging, JTAG mode is used to directly write logic into the FPGA. After debugging, PS mode is used to write the program into the configuration chip. Different configuration methods can be selected by jumpering the pins on the FPGA and configuration chip. The jumper circuit is shown in Figure 5.

Figure 5 FPGA configuration jumper settings

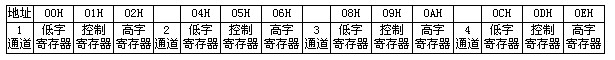

As an I/O peripheral of DSP, FPGA must uniformly address its register addresses. Here, the FPGA is addressed in the I/O space of the DSP. Since the FPGA's receiving channel and sending channel share the 16-bit data line of the DSP, the data registers of the receiving channel and the sending channel can occupy one address. Table 1 shows the addresses allocated to each channel register of FPGA.

Table 1 Register address of each channel inside FPGA

3.3 Communication between DSP, FPGA and external devices In the design of the entire system, DSP is mainly used to control FPGA work, data transfer, and communication with peripheral hosts. DSP is the center of the entire system, controlling the coordinated work of each part. The DSP is used to write a control word to the FPGA, which contains information such as the length of the frame interval, and can control the FPGA; in addition, according to the feedback status of the FPGA, corresponding control adjustments can be made. Considering that there are many I/O ports used to control FPGA, the DSP selected is TI's TMSLF2407A. TMSLF2407A has up to 39 multiplexed peripheral I/O ports [2]. Figure 6 shows the specific connection between DSP and FPGA. Figure 6 Schematic diagram of the connection between DSP and FPGA

DSP provides I/O operation signal /IS, read and write selected signal R/W, read enable signal /RD, write enable signal /WE and the lower four bits of the address line A0, A1, A2, A3. Through these control logic signals, four channels and the high and low words of each channel can be distinguished.

Other auxiliary control and status signals provided by DSP and FPGA include: four-way transmission enable signal/ENTX[0..3], active at low level; four-way transmission stop signal/TXT[0..3], low level The level is valid; the four receiving channel clearing signals/CHACLRN[0..3], low level are valid; the receiving data arrival signal/RER[0..3] is used to inform the DSP to prepare to receive the data that has arrived on a certain channel. Data; send data ready signal/TXR[0..3] signal, used to inform each sending channel whether there is unsent data temporarily stored in the FIFO, low level means there is no data; sending channel FIFO full signal FUL[ 0..3], high level active; GLOBCLRN signal, used to globally clear the FPGA internally during initialization; TESTREQ signal, used for self-test of the entire system.

The entire circuit board communicates with the peripheral host through dual-port RAM. The dual-port RAM is responsible for temporarily storing data to be sent by the peripheral and temporarily storing data processed by the FPGA. It can be roughly divided into 8 areas, each area is responsible for storing one data and control word in four receiving channels and four sending channels. The interface board can be commanded to perform corresponding operations by using the left and right interrupt mailboxes of the dual-port RAM.

4 Software design

Software design is mainly DSP programming. The main tasks of the DSP program are to initialize, manage DSP peripheral circuits, control the FPGA to send and receive data, and interact with peripherals. The main program flow chart of DSP is shown in Figure 7.

After the entire interface circuit board is debugged, it can receive and send four ARINC429 signals at the same time after testing. This solves the bottleneck of too few channels on the interface circuit board in the past. Taking advantage of the advantages of high density, flexible structure, short design time and programmability of FPGA, independent processing of a certain ARINC429 signal is achieved, coupled with the rich I/O interfaces of TI's 2000 series DSP and faster speed than ordinary microcontrollers , realizing the control and management of FPGA and communication with peripherals. Therefore, this system provides a new and advanced method for the interconnection of airborne data communication buses in today's civil aircraft, and has quite general practical significance.

Figure 7 DSP main program flow chart

References

1 Chu Zhenyong, Weng Muyun. FPGA design and application. Xi'an: Xi'an University of Electronic Science and Technology Press, 2000

2 TMSLF2407A Fix-Point Digital Signal Processor (SPRS1451). Texas Instrument, 2000

3 Liu Heping. TMSLF240x DSP c language development and application. Beijing: Beijing University of Aeronautics and Astronautics Press, 2002

Previous article:DSP-based autofocus system

Next article:Seagate wades into mobile storage, local partners may become rivals

- Popular Resources

- Popular amplifiers

- Huawei's Strategic Department Director Gai Gang: The cumulative installed base of open source Euler operating system exceeds 10 million sets

- Analysis of the application of several common contact parts in high-voltage connectors of new energy vehicles

- Wiring harness durability test and contact voltage drop test method

- Sn-doped CuO nanostructure-based ethanol gas sensor for real-time drunk driving detection in vehicles

- Design considerations for automotive battery wiring harness

- Do you know all the various motors commonly used in automotive electronics?

- What are the functions of the Internet of Vehicles? What are the uses and benefits of the Internet of Vehicles?

- Power Inverter - A critical safety system for electric vehicles

- Analysis of the information security mechanism of AUTOSAR, the automotive embedded software framework

Professor at Beihang University, dedicated to promoting microcontrollers and embedded systems for over 20 years.

Professor at Beihang University, dedicated to promoting microcontrollers and embedded systems for over 20 years.

- Innolux's intelligent steer-by-wire solution makes cars smarter and safer

- 8051 MCU - Parity Check

- How to efficiently balance the sensitivity of tactile sensing interfaces

- What should I do if the servo motor shakes? What causes the servo motor to shake quickly?

- 【Brushless Motor】Analysis of three-phase BLDC motor and sharing of two popular development boards

- Midea Industrial Technology's subsidiaries Clou Electronics and Hekang New Energy jointly appeared at the Munich Battery Energy Storage Exhibition and Solar Energy Exhibition

- Guoxin Sichen | Application of ferroelectric memory PB85RS2MC in power battery management, with a capacity of 2M

- Analysis of common faults of frequency converter

- In a head-on competition with Qualcomm, what kind of cockpit products has Intel come up with?

- Dalian Rongke's all-vanadium liquid flow battery energy storage equipment industrialization project has entered the sprint stage before production

- Allegro MicroSystems Introduces Advanced Magnetic and Inductive Position Sensing Solutions at Electronica 2024

- Car key in the left hand, liveness detection radar in the right hand, UWB is imperative for cars!

- After a decade of rapid development, domestic CIS has entered the market

- Aegis Dagger Battery + Thor EM-i Super Hybrid, Geely New Energy has thrown out two "king bombs"

- A brief discussion on functional safety - fault, error, and failure

- In the smart car 2.0 cycle, these core industry chains are facing major opportunities!

- The United States and Japan are developing new batteries. CATL faces challenges? How should China's new energy battery industry respond?

- Murata launches high-precision 6-axis inertial sensor for automobiles

- Ford patents pre-charge alarm to help save costs and respond to emergencies

- New real-time microcontroller system from Texas Instruments enables smarter processing in automotive and industrial applications

- After more than two months of hard work, it is finally finished. Haha

- Live Review: Renesas Electronics R-Car Advanced Driver Assistance System Solution

- TI CC2531 USB Evaluation Module Kit

- Lantern with capacitive touch support

- TI's active equalization solution

- After the ZIGBEE3.0 online seminar this morning, have you DIYed a home automation control system?

- Overcome last-minute requirement changes with small, leaded SOT-23 thin multiplexers

- Where can I find older ICs?

- Make ADAS technology more popular in vehicles

- What is a hysteresis comparator?

Real-time driver monitoring system via modal and viewpoint analysis

Real-time driver monitoring system via modal and viewpoint analysis CVPR 2023 Paper Summary: Efficient and Scalable Vision

CVPR 2023 Paper Summary: Efficient and Scalable Vision

京公网安备 11010802033920号

京公网安备 11010802033920号